12位、300 kSPS、单电源、完全隔离式数据采集系统 用于4-20 mA输入

评估和设计支持

电路评估板

CN0336电路评估板(EVAL-CN0336-PMDZ)

SDP/PMD转接板(SDP-PMD-IB1Z)

系统演示平台(EVAL-SDP-CB1Z)

设计和集成文件

原理图、布局文件、物料清单

电路功能与优势

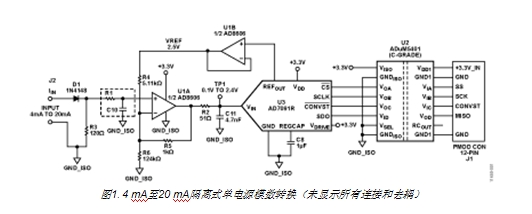

图1所示电路是只采用了三个有源器件的完全隔离式12位、300 kSPS数据采集系统。

该系统采用3.3 V单电源供电,可处理4 mA至20 mA的输入信号。室温校准后在±10°C温度变化范围内的总误差为 ±0.06% FSR,是各种工业测量应用的理想之选。

该电路尺寸小巧使得该组合成为业界领先的4 mA至20 mA数据采集系统解决方案,在这种系统中精度、速度、成本和尺寸极为关键。数据和电源相互隔离,因而该电路具有出色的高电压耐受性,同时还能有效免疫恶劣工业环境下常见的接地环路干扰问题。

电路描述

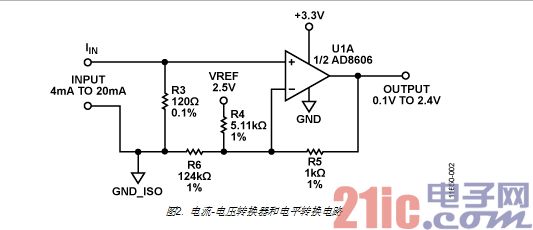

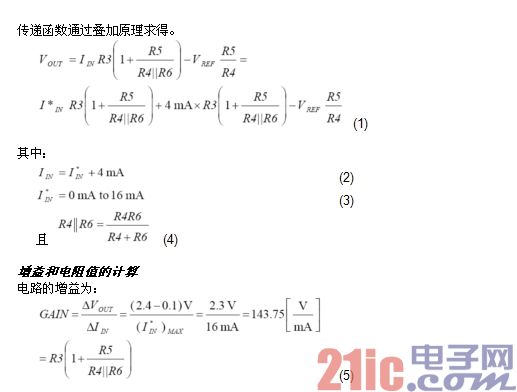

该电路由一个输入电流-电压转换器、一个电平转换电路、一个ADC级和一个输出隔离级构成。4 mA至20 mA输入信号由电阻R3转换成电压。在R3 = 120Ω且输入电流为4 mA至20 mA的情况下,电平转换电路的输入电压为:0.48 V至2.4 V。二极管D1用于提供保护,使电路免受输入电流源意外反相连接的影响。

R3上的电压由U1A运算放大器进行电平转换和衰减,该运算放大器是双通道AD8606的一半。该运算放大器的输出为0.1 V至2.4 V,与ADC的输入范围相匹配(0 V至2.5 V),裕量为100 mV用于维持线性度。来自AD7091R ADC的缓冲基准电压源(VREF = 2.5 V)用于生成所需失调。可以修改电阻值,以适应本电路笔记后面部分所述的其他常用输入范围。

该电路设计支持单电源供电。AD8606的最小额定输出电压为50 mV(2.7 V电源)和290 mV(5 V电源),负载电流为10 mA,温度范围为-40°C至+125°CC。在3.3 V电源、负载电流低于1 mA、温度范围更窄的情况下,保守估计最小输出电压为45 mV至60 mV。

考虑到器件的容差,最小输出电压(范围下限)设为100 mV,以提供安全裕量。输出范围的上限设为2.4 V,以便为ADC输入端的正摆幅提供100 mV的裕量。因此,输入运算放大器的标称输出电压范围为0.1 V至2.4 V。

AD8606 (U1B)的另一半用于缓冲AD7091R (U3) ADC的内部2.5 V基准电压源。

本应用中选用AD8606的原因是该器件具有低失调电压(最大值65 μV)、低偏置电流(最大值1 pA)和低噪声(最大值12 nV/√Hz)等特性。在3.3V电源下,功耗仅为9.2 mW。

运算放大器的输出级后接一个单极点RC滤波器(R2/C11),用于降低带外噪声。RC滤波器的截止频率设为664 kHz。可添加一个可选滤波器(R1/C10),以便在出现低频工业噪声的情况下,进一步降低滤波器截止频率。在这类情况下,由于信号带宽较小,因此可以降低AD7091Rhttp://www.analog.com/AD7091R?doc=CN0336.pdf的采样速率。

选择AD7091R 12位1 MSPS SAR ADC是因为其在3.3 V (1.2 mW)下的功耗超低,仅为349 μA,显著低于当前市场上竞争对手的任何ADC。AD7091R还内置一个2.5 V的基准电压源,其典型漂移为±4.5 ppm/°C。输入带宽为7.5 MHz,且高速串行接口兼容SPI。AD7091R采用小型10引脚MSOP封装。

采用3.3V电源供电时,该电路的总功耗(不包括ADuM5401隔离器)约为10.4 mW。

电流隔离由四通道数字隔离器ADuM5401(C级)提供。除了隔离输出数据以外,ADuM5401还为该电路提供隔离+3.3 V电源。除非需要隔离,否则电路正常运行时并不需要ADuM5401。ADuM5401四通道2.5 kV隔离器集成DC/DC转换器,采用小型16引脚SOIC封装。ADuM5401在7 MHz时钟频率下的功耗约为140 mW。

AD7091R需要50 MHz的串行时钟(SCLK),方能实现1 MSPS的采样速率。然而,ADuM5401(C级)隔离器的最大数据速率为25 Mbps,对应的最大串行时钟频率为12.5 MHz。另外,SPI端口要求,SCLK的后沿将输出数据驱动至处理器,因此,ADuM5401的总双向传播延迟(最大值120 ns)将时钟上限限制在1/120 ns = 8.3 MHz。

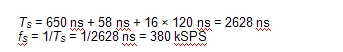

尽管AD7091R是一款12位ADC,但串行数据同样被格式化为16位字,以便与处理器串行端口要求相兼容。因此,采样周期TS包括AD7091R 650 ns的转换时间加上58 ns(数据手册要求的额外时间,t1延迟 + tQUIET延迟),再加上用于SPI接口数据传输的16个时钟周期。

为了提供安全裕量,建议将SCLK和采样速率的最大值分别设为7 MHz和300 kSPS。数字SPI接口可以用12引脚且兼容Pmod的连接器(Digilent Pmod规格)连接到微处理器评估板。

电路设计

图2所示电路提供了适当的增益和电平转换功能,可以将0.48 V至2.4 V信号转换为ADC输入范围,即0.1 V至2.4 V。

当输入范围为0 mA至20 mA时,电路不需要进行电平转换,运算放大器充当跟

- 基于SOC的高精度红外测温系统设计(07-13)

- 12位、1 MSPS、单电源、低功耗数据采集系统(10-16)

- 带三线式补偿的12位、300 kSPS、单电源、完全隔离式RTD温度测量系统(10-16)

- 12位AD574与8088CPU的接口电路图(09-03)

- MAX1437B 8路、12位模数转换器(ADC)(05-21)

- MAX11612-MAX11617低功耗12位多通道模数转换器(ADC)(05-21)