基于DSP的高速AD采集系统设计与实现

要求,AD7656访问时序图见图5所示。

AD7656包括6通道ADC转换,可实现6通道ADC同步转换,减少了多路ADC转换采样时间。在CPLD逻辑设计中采用同时控制“CONVSTA”

“CONVSTB”“CONVSTC”管脚输出有效完成6通道ADC通道同步转换。

根据图5所示AD76565通过“CONVSTA,B,C”信号的上升沿启动ADC转换,ADC转换过程中,“BUSY”信号为逻辑“高”标识,ADC正在转换过程中,ADC转换时钟由内部时钟产生,从“CONVSTA,B,C”信号的上升沿启动转换3 μs后ADC转换结束,“BUSY”信号为逻辑“低”表示ADC转换结束。TMS320C6713B通过EMIF总线接口完成对转换结果的读取。对AD7656芯片转换结果读取,通过“CS”片选信号和“RD”读信号控制,6个通道转换结束后,TMS320C6713B控制“CS”为有效和6个“RD”读有效信号,完成对模拟量输入“V1”信号、“V2”信号、“V3”信号、“V4”信号、“V5”信号、“V6”信号转换结果的读取。

2.3 AD7656设计中应注意问题

2.3.1 电压基准电路设计

由于AD7656转换的精度与参考电压基准电压的精度有很大关系,参考电压基准输出电压值用来确定数据转换系统的满量程输入范围,同时参考电压基准电压的任何误差都会严重影响ADC的线性和无杂散动态范围。

由于AD7656内部集成的电压基准参数精度低,一般在对于分辨率大于12位的ADC应用中采用高精密外部电压基准,本设计采用高精密外部电压基准AD780BR作为AD7656转换的电压基准。通过表2对两种电压基准参数比较,看出外部高精密电压基准精度高,具有更低的温度系数、热迟滞和长期漂移。

3 PCB设计

3.1 数\模区域分割

在高速AD采集电路的设计中,达到高精度与PCB设计是密不可分的,所以进行PCB设计过程中,按照电路实现的功能可以简单地划分为数字电路和模拟电路两部分,将数字区域与模拟区域进行分割,形成每个区域的独立电源和地,这样可以有效抑制干涉的传导和RF能量的辐射。

AD7656芯片在管脚定义时将模拟量和数字量信号按区域定义,有利于PCB设计中数字量和模拟量区域分割,布线时注意模拟信号区域布模拟信号线,数字信号区域布数字信号线,不要将数字信号线和模拟信号线并行布线。

在本系统中模拟地和数字地采用一个电势参考点,所以模拟地和数字地采用单点共地,共地点尽可能地靠近AD7656。

3.2 电源去耦设计

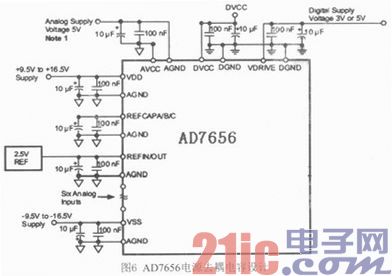

由于AD7656芯片存在多个电源管脚,在每个电源管脚需要连接去耦电容。去耦电容的设计中采用并联100nF和10 μF电容。电容选择时可选用具有小等效串联电感(ESL)瓷介质电容。AD7656的去耦电容设计见图6所示。

4 AD采集软件设计实现

TI公司提供良好的C/C++编译器,在TMS320C6713B软件开放过程中支持C/C++语言设计。并且提供的良好的库函数(DSPLIB),支持TMS3 20C6713B的数学运算和矢量运行。

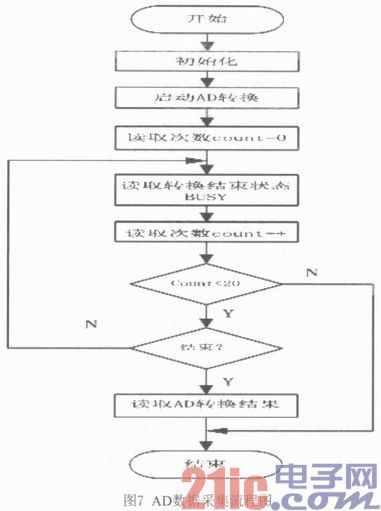

采集软件设计采用了模块化设计,主要包括初始化函数、AD7656转换启动函数和AD7656转换结果读取函数。

初始化函数实现对TMS320C6713B系统时钟、EMIF总线时钟配置,EMIF总线接口访问时序的配置。通过该初始化函数配置,配置CS(片选)RD读信号相对时序关系,满足AD7656访问时序关系。

AD7656转换启动函数实现启动AD7656的AD转换,该函数控制AD7656转换启动信号CONVSTA,B,C为有效状态,同步6路AD转换。

AD7656转换结束标识查询函数实现对AD7656转换状态标识信号BUSY查询,判断AD7656内部ADC转换是否结束。

AD7656转换结果读取函数实现档查询到AD转换结束标识后,读取AD转换结果。该函数通过连续的6次读操作,读取6路AD同步转换结果。 AD采集软件流程见图7所示。

5 结束语

针对要求高精度、多路信号监测和实时采集,本设计选用了AD7656和TMS320C6713B相结合作为某控制系统工作状态实时监控以及故障检测系统方案,本设计接口电路设计简单,采集精度高、速度快,可同时完成对多路信号的采集。系统联试证明,本系统完全满足某控制系统对工作状态监控以及故障检测信号的采集精度和实时性的要求。

TMS320C6713B AD7656 接口电路 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)