基于FPGA的高速数字下变频系统设计

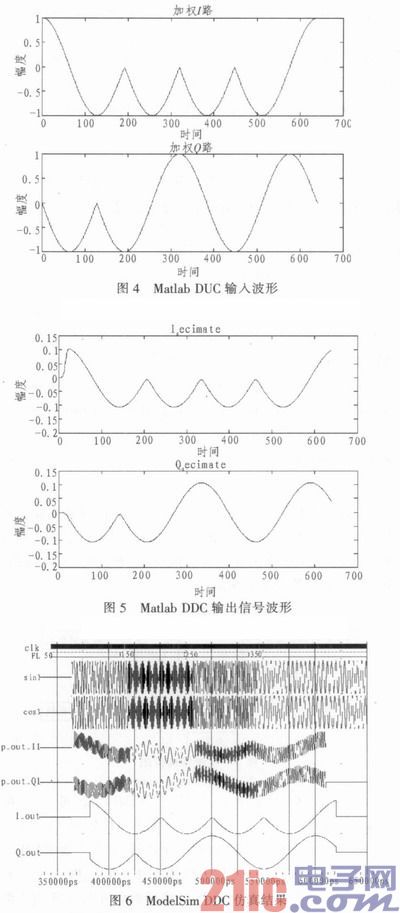

tlab软件对整个的数字下变频系统进行了建模仿真,并使用Verilog硬件描述语言在Xilinx的kintex7系列FPGA上实现了该数字下变频器。为了更好的验证该下变频器的设计,我们利用Matlab建模的上变频系统产生该下变频器的输入激励,如图4所示为上变频系统的输入波形。图5为Matlab建模仿真得到的数字下变频器I、Q两路的输出信号波形。图6为利用Modelsim仿真得到的输出结果,NCO本振频率(CLK)为320 MHz,输入信号跳变频率(FL)分别为50 MHz、150 MHz、250 MHz、350 MHz以及450 MHz,P_out_I1和P_out_Q1分别为混频后四相I、Q信号中的一路,I_out和Q_out为经过多相滤波后最终的输出波形。从Matlab和ModelSim的仿真波形可以很直观的看出我们设计的数字下变频器与理论相符,输出结果正确,达到了预期的设计目的。

4 结论

在设计数字下变频n系统中,提高处理速度是很关键的一部分,本设计首先利用多相结构,将数据分为D路,把每一路的数据速率降成原来的D分之一。在设计低通滤波器和乘法器模块时充分利用了Kintex7上的硬核资源DSP 48,大幅度的提高了电路的处理速度。利用Xilinx的ISEl4.4工具进行综合、布局、布线后的时序报告显示,该电路最高工作速度可达360 MHz,充分显现了此设计的速度优势。由于该数字下变频器是基于FPGA实现的,且具有很高的工作速度,可用它来代替大多数的专用数字下变频芯片,它能够满足大多数通信系统中接收机对数字下变频器处理速度、处理带宽以及滤波性能的要求,可广泛应用于数据采集、软件无线电等领域中,具有较高的实用价值。

- 基于AD9680的宽带高动态全数字雷达接收机设计(10-16)

- 一种基于多相滤波结构的雷达信号检测技术(07-17)

- 基于多相滤波结构的雷达信号检测技术(09-26)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)