基于ADS1278的高精度微应变信号采集系统

摘要:以24位工业模数转换器AD51278为核心,设计了一个高精度微应变信号采集系统,给出对应的前端调理电路和数字采集模块等。模拟测试结果显示,该系统方案可行,可有效采集微应变信号,已成功应用于桥梁振动检测等产品。

微应变信号采集是桥梁振动监测、动态应变测量和压力测量等设备设计的重点。为实现微应变信号的高精度采集,本文基于德州仪器公司的24位高精度工业模拟-数字转换器ADS1278,设计了一个高精度微应变信号采集系统,并给出对应的前端调理电路和数字采集模块。测试结果显示,该系统能有效采集微应变信号。

1 ADS1278简介

1.1 ADS1278特点

ADS1278内部集成有多个独立的高阶斩波稳定调制器、FIR数字滤波器、输入多路复用器等功能。可通过内部控制寄存器的不同配置得到不同的A/D采样速率、采样模式、A/D转换精度等,支持高速、高精度、低功耗、低速等4种工作模式。ADS1278可以通过设置相应的输入/输出引脚选择工作模式,不需寄存器编程。其数据输出可选同步或SPI串行接口,便于连接到FPGA、DSP及微控制器,适用于对性能、功耗要求高、模拟通道要求多的数据采集系统,如桥梁振动分析、动态应变测量及压力测量设备等。

ADS1278的主要性能有:8通道同时采样测量,高达128 kSPS的数据传输速率,线性相位数字滤波器,SPT或帧同步串行接口,62 kHz带宽,111 dB信噪比(高分辨率模式)以及高达108 dB的总谐波失真(THD)等。

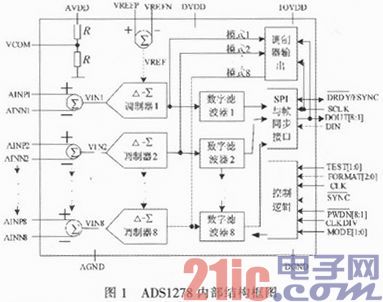

1.2 ADS1278工作原理

如图1所示为ADS1278内部结构框图,主要由8个独立的ADC并行实现8通道输入信号的数字化,每个ADC由先进的6阶斩波△-∑调制器,后接低纹波、线性相位的有限冲积响应(FIR)数字滤波器构成。调制器检测差分输入信号VIN=(AINP-AINN),并与差分参考电压VREF=(VREFP-VREFN)相比较得到一个1秒密度的位流输出,输出的位流经内部的数字滤波器滤波后得到一个低噪声的数字输出。工作时,调制器以高速采样输入信号(典型值输出数据率的64倍),其产生的量化噪声被移入高频带,由内部的数字滤波器滤除。调制器的过采样倍率与工作模式有关,分别可取64倍(高速、低速、低功耗模式)或128倍(高精度模式)。数字滤波器可对截止频率外的信号衰减100 dB以上,使信号导通带宽在90%的奈奎斯特频率时纹波低于0.005 dB。

1.3 ADS1278接口特性

如图1所示,ADS1278转换后的数据输出采用串行接口,可采用SPI和帧同步两种接口协议。对应SPI和帧同步接口协议,转换后的数据分别通过独立的DOUT引脚以并行数据形式(离散模式)移位输出或通过一个共同的引脚DOUT1(TDM模式)移位输出,协议和数据输出格式的选择由FORMAT[2:0]引脚的输入状态确定。

2 以ADS1278为核心的高精度采样电路

2.1 设计框图

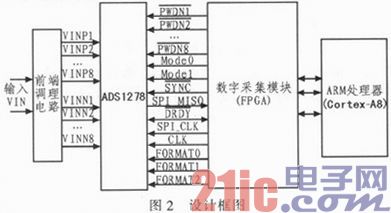

采样电路总体设计框图如图2所示。其中,前端调理电路实现对输入信号VIN的滤波、放大;ADS1278对经滤波、放大的信号实现AD转换;通过FPGA的引脚电平选择实现对ADS1278数据输出的接口类型、接口协议、掉电控制、输出格式、工作模式、主时钟、数据串口传输时钟等配置,并完成数据采集与传输;ARM处理器Cortex—A8主要实现对所采集来的数据进行分析处理。

2.2 前端调理电路

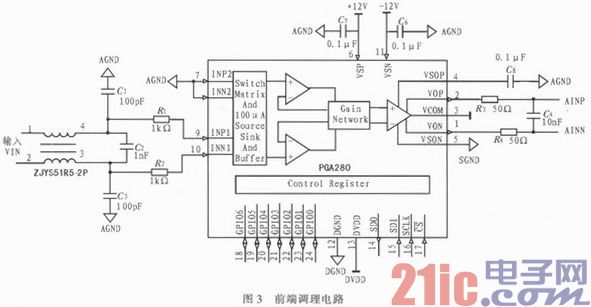

ADS1278的前端调理电路如图3所示。采用共模滤波器ZJYS51R5-2P TDK和可编程增益放大器PGA280AIPW对输入信号VIN进行滤波及放大,其中

、SCLK、SDI可以与FPGA相应输入输出端口连接,通过FPGA的配置实现对输入信号1/8~128(1/8,1/4,1/2,1,2,4,8,…,128)的放大倍数。

2.3 数字采集模块

如图2所示,ADS1278接收差分模拟信号,输入信号接到引脚AINP、AINN,AINP为正信号输入端,AINN为负信号输入端。数字地(DGND)与模拟地(AGND)分开布局,然后在ADS1278上通过一个共地点来连接DGND和AGND引脚。

FPGA的IO_1(IO/LVDS23p)与ADS1278的掉电控制端口

相连接,将IO_1拉低,屏蔽各通道的掉电控制功能。

ADS1278与EP1C12Q240C8之间采用SPI接口实现数据交换,以补码形式输出24位数据,正的满刻度输入时,输出数据编码为7FFFFFH;负的满刻度输入时,输出数据编码为800000H。MODE[1:0]=01。设置成高精度工作模式。TEST[1:0]=00,设置ADS1278处于正常工作模式。

ADS1278的

作为就绪状态查询信号,DOUT1引脚接FPGA的IO_13(IO/LVDS20n),用来接收ADS1278转换后的串行输出数据。 ADS1278无需启动信号,只要通电即开始转换,可在任何需要的时候通过查询

引脚为低电平时取走数据。在SPI串行时钟SCLK的时序下,FPGA从ADS1278的DOUT1引脚一位一位地读取,并首先存储在SRAM1芯片。当SRAM1存储满数据,FPGA内部总线允许ARM

ADS1278模数转换器 微应变信号 数字滤波 高精度采集 相关文章:

- 揭开Σ-ΔADC的神秘面纱(07-06)

- 基于Matlab的IIR数字滤波器设计方法比较及应用(07-15)

- 基于Visual DSP++的无限脉冲响应数字滤波器(IIR)设计(05-21)

- 关于IIR滤波器的设计心得(08-09)

- 数字滤波器的软件设计流程(07-26)

- 基于PIC18F的全自动热敏电阻测试仪设计(04-12)