基于ADS的C波段的低噪声放大器仿真设计研究

时间:10-29

来源:互联网

点击:

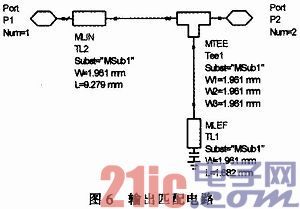

2.7 输出匹配电路设计

输出匹配电路的设计主要考虑增益和驻波比,基本任务是把微波管复数输出阻抗匹配到负载实数阻抗,从而提高增益和输出驻波比,匹配电路如图6所示。

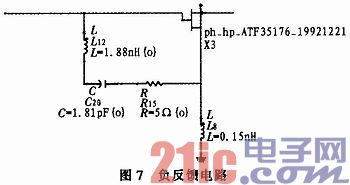

2.8 负反馈电路

为了适当改善放大器增益平坦度,在晶体管栅源之间采用负反馈网络所示,具体电路如图7所示。

实际上负反馈网络除了拓宽频带、改善增益平坦度外,还参与了匹配并改善输入输出驻波,其优点是便于充分发挥PHEMT电路的低噪声和高增益特性。

2.9 整体电路仿真优化

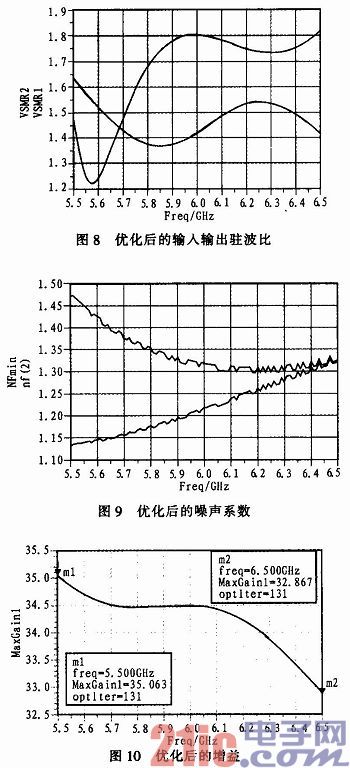

采用ADS中的优化功能,对原理图中微带线的长度、电容与电感值进行优化,最后得到满足要求的低噪声放大器。其仿真所得的驻波比、噪声系数以及增益分别如图8、图9、图10所示。

通过ADS仿真,噪声放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪声系数小于1.5 dB,驻波比小于2,满足设计需求。

3 结束语

文中主要采用三级放大,低噪声放大器选用ATF-35176晶体管,通过仿真分析,完成了偏置电路以及输入、级间和输出的匹配电路设计,并采用ADS软件进行全部电路的优化仿真,仿真结果表明,低噪声放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪声系数小于1.5 dB,驻波比小于2,达到了设计指标的要求。本设计还有进一步改善的可能,接下来将继续采用一些其他的设计结构来改善此设计。

低噪声放大器 ADS PHEMT 负反馈网络 匹配电路 相关文章:

- 利用Cadence设计COMS低噪声放大器(06-11)

- 基于ADS的通信设备低噪声放大器改进设计与仿真(04-09)

- 航天GPS接收机的低噪声放大器设计(05-10)

- X波段低噪声放大器设计分析(08-01)

- 基于Cadence的COMS低噪声放大器设计(02-08)

- 一款超低噪声S频段放大器设计(09-13)