更多功能用于植入式医疗设备的下一代电源组

时间:01-16

来源:互联网

点击:

说到植入式医疗设备,节省空间是最关键的设计问题之一。本文对缩减电子电源器件所需空间可使用的封装概念进行了综述,这样整体植入设备可以收缩——在不扩大使用空间的情况下增加更多的功能。

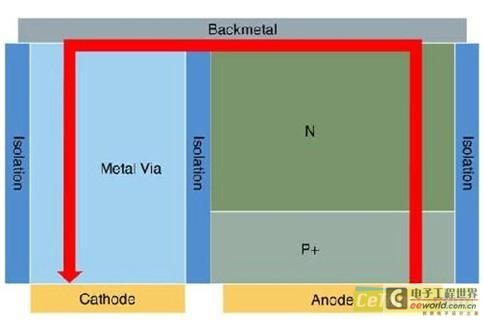

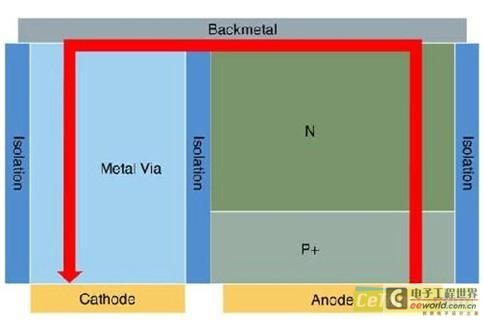

图 1 :镀金属的硅穿孔

植入式医疗设备的市场仍然很大。无论是人口驱动因素和使用次数都在明显扩张。市场的大部分增长来自于努力扩大电子器件能参与的手术治疗方法。改良型起搏器类产品可被用于阻止慢性腰腿疼痛和偏头痛。此外,还有其它医疗电子产品可用于调节与抑郁症、焦虑症、强迫症和贪食症等相关的症状。这本是一个缓慢改变的行业,对于医疗设备供应商来说成本,性能和质量所带来的越来越大压力,从而带动产品和服务的创新。但小型化仍然是植入式医疗设备的关键增长推动力。对于病人来说,一款更小的器件能让手术切口更小,让伤口不那么吓人,手术过程没那么紧迫,身体愈合快,而且植入物没有那么明显。

用于植入式医疗设备的高功率组件,如 IGBT 、 SCR 、 MOSFET 和整流器,给电路设计者独特的电路布局带来了挑战。首先,需要较大的裸片尺寸来处理能量问题。例如,在植入式心脏除颤器中,电压可高达 700 伏,浪涌电流可高达 60 安培。其次,植入设备的顶部和底部都需要电气接点。功率器件采用“垂直”制造结构,从而允许更高的阻断电压和更高的电流。再有,必须对高压电弧加以控制。在植入式医疗设备中,芯片和电线仍然很常用。除了有一层保护性涂层之外,小心裸片和导线的间距对于防止产生电弧至关重要。设计人员正在寻找一个能免除电弧、涂层,电线粘接的封装方案,并且能同时最大限度地节省电路板空间。需要一个芯片级的、能将背面连接到同一块面板正面的倒装芯片电源封装方式。

陶瓷载体

一种创建一个平面倒装芯片功率封装的方法是将裸片附加在陶瓷载体上。在这种情况下,陶瓷载体的形状像一个倒写的“ L ”。裸片焊接或用环氧树脂固定到陶瓷上。金属走线被嵌到陶瓷里面,将背面连接路由至与正面,形成一款平面器件。裸片和陶瓷载体都放有焊球,以便能贴上平面倒装芯片,相比芯片和电线和节省空间。此外,陶瓷是一种耐高压电弧的良好绝缘体。制造中有待克服的问题包括 X, Y 和 Z 平面性,因为裸片在附着到陶瓷载体时会产生移动或倾斜。

TSV 技术

另一种解决方案是通过使用金属填充硅片通孔( TSV )技术。若使用此方法,芯片的尺寸扩大到包括邻近活性硅( active silicon )附近的非活性硅区域。先在非活性硅里打通一个通孔,然后用金属填充(图 1 )这个通孔,从而建立一个电路信道。电流从活性硅区域,通过背面的金属再到 TSV 。这就可以将背面的接触点转移到前面。芯片的尺寸有所增加,但没有第一种采用陶瓷载体方案的芯片增加的多。图 1 只是使用 TSV 时的一个结构图。从这个基本结构可以引申出很多变化。例如,建立允许中介层连接或者裸片堆叠的背部连接。

TSV 是一项新兴的制造工艺,似乎在用于处理功率器件的大电流方面也是一款很有前景的解决方案。但据 VLSI Research 在近期国际互连技术会议的说法,“大规模生产 TSV 仍然还要等几年”。在实现大规模生产之前,每片晶圆的加工成本仍将过高。成本较低的 TSV 解决方案仍然在电源设备生产中受到检验。

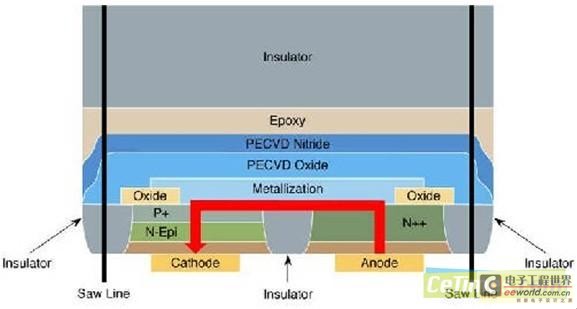

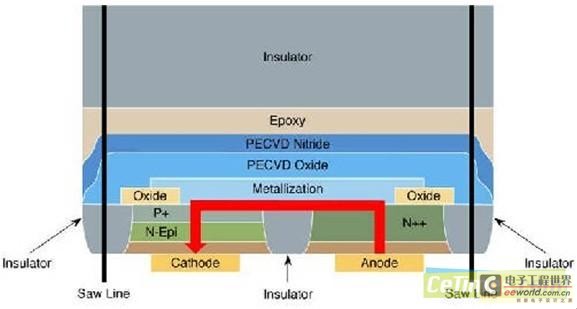

图 2 绝缘体上的功率芯片

功率裸片堆叠

电源芯片堆叠在今天得以实用。这种技术首先要求有两个或多个预知良好的裸片,并将其垂直焊接在一起。这些设计采用完善的技术,包括中介层、焊接和引线粘接,以垂直整合芯片功能。这种方法的主要优点是,它只需要一半的电路板空间,并且允许使用多种晶圆加工技术。主要缺点是仍然需要引线连接,高压电弧仍然是一个问题,累计的成品率损失往往会使成本增高。折叠式柔性电路是另一种可使用的裸片堆叠方法。利用折纸般的折叠方法,功率裸片可以彼此堆叠在一起。诀窍在于如何在保持较小尺寸,且不需要引线的同时实现同一块功率裸片的顶部和底部的连接。

绝缘体上的功率芯片

绝缘层上的功率芯片( PSOI )是一类密封芯片级封装,采用不同的方法将电气连接放到同一侧(图 2 )。 PSOI 使用标准的加工工艺在同一侧开发有源区域,但采用顶部金属化融入此区域。然后将顶层通过附着一层顶层绝缘体进行密封和保护。外部金属化接触点被放在器件的底部,非常类似倒装芯片封装,但是有了 PSOI ,底部和两侧被隔离开,形成了独特的“晶圆级封装”。芯片可以以任何形式切开,如单锯,对偶、四边形等。这样消除了任何后期制造步骤。经过以晶圆的形式切割后,产品经测试,并采用合适的容器如松饼式或凝胶进行封装,可以随意拾取和放置。

顶部、底部和侧面的绝缘体将接合处与环境污染物和湿气隔离开。这一工艺无需引线连接和保护性涂层,从而缩小了整个芯片的尺寸。 PSOI 也可以采用顶部接触堆叠的方式制造,提供卓越的热特性和小尺寸,同时保持浪涌性能。这一过程提供了芯片 - 芯片的电气隔离并降低了寄生效应。总产出量必须与标准晶圆方式的产量不相上下,以匹配成本。与目前所用的封装技术相比,可将整体电路所占用的空间减少 20 %至 55 %。

图 1 :镀金属的硅穿孔

植入式医疗设备的市场仍然很大。无论是人口驱动因素和使用次数都在明显扩张。市场的大部分增长来自于努力扩大电子器件能参与的手术治疗方法。改良型起搏器类产品可被用于阻止慢性腰腿疼痛和偏头痛。此外,还有其它医疗电子产品可用于调节与抑郁症、焦虑症、强迫症和贪食症等相关的症状。这本是一个缓慢改变的行业,对于医疗设备供应商来说成本,性能和质量所带来的越来越大压力,从而带动产品和服务的创新。但小型化仍然是植入式医疗设备的关键增长推动力。对于病人来说,一款更小的器件能让手术切口更小,让伤口不那么吓人,手术过程没那么紧迫,身体愈合快,而且植入物没有那么明显。

用于植入式医疗设备的高功率组件,如 IGBT 、 SCR 、 MOSFET 和整流器,给电路设计者独特的电路布局带来了挑战。首先,需要较大的裸片尺寸来处理能量问题。例如,在植入式心脏除颤器中,电压可高达 700 伏,浪涌电流可高达 60 安培。其次,植入设备的顶部和底部都需要电气接点。功率器件采用“垂直”制造结构,从而允许更高的阻断电压和更高的电流。再有,必须对高压电弧加以控制。在植入式医疗设备中,芯片和电线仍然很常用。除了有一层保护性涂层之外,小心裸片和导线的间距对于防止产生电弧至关重要。设计人员正在寻找一个能免除电弧、涂层,电线粘接的封装方案,并且能同时最大限度地节省电路板空间。需要一个芯片级的、能将背面连接到同一块面板正面的倒装芯片电源封装方式。

陶瓷载体

一种创建一个平面倒装芯片功率封装的方法是将裸片附加在陶瓷载体上。在这种情况下,陶瓷载体的形状像一个倒写的“ L ”。裸片焊接或用环氧树脂固定到陶瓷上。金属走线被嵌到陶瓷里面,将背面连接路由至与正面,形成一款平面器件。裸片和陶瓷载体都放有焊球,以便能贴上平面倒装芯片,相比芯片和电线和节省空间。此外,陶瓷是一种耐高压电弧的良好绝缘体。制造中有待克服的问题包括 X, Y 和 Z 平面性,因为裸片在附着到陶瓷载体时会产生移动或倾斜。

TSV 技术

另一种解决方案是通过使用金属填充硅片通孔( TSV )技术。若使用此方法,芯片的尺寸扩大到包括邻近活性硅( active silicon )附近的非活性硅区域。先在非活性硅里打通一个通孔,然后用金属填充(图 1 )这个通孔,从而建立一个电路信道。电流从活性硅区域,通过背面的金属再到 TSV 。这就可以将背面的接触点转移到前面。芯片的尺寸有所增加,但没有第一种采用陶瓷载体方案的芯片增加的多。图 1 只是使用 TSV 时的一个结构图。从这个基本结构可以引申出很多变化。例如,建立允许中介层连接或者裸片堆叠的背部连接。

TSV 是一项新兴的制造工艺,似乎在用于处理功率器件的大电流方面也是一款很有前景的解决方案。但据 VLSI Research 在近期国际互连技术会议的说法,“大规模生产 TSV 仍然还要等几年”。在实现大规模生产之前,每片晶圆的加工成本仍将过高。成本较低的 TSV 解决方案仍然在电源设备生产中受到检验。

图 2 绝缘体上的功率芯片

功率裸片堆叠

电源芯片堆叠在今天得以实用。这种技术首先要求有两个或多个预知良好的裸片,并将其垂直焊接在一起。这些设计采用完善的技术,包括中介层、焊接和引线粘接,以垂直整合芯片功能。这种方法的主要优点是,它只需要一半的电路板空间,并且允许使用多种晶圆加工技术。主要缺点是仍然需要引线连接,高压电弧仍然是一个问题,累计的成品率损失往往会使成本增高。折叠式柔性电路是另一种可使用的裸片堆叠方法。利用折纸般的折叠方法,功率裸片可以彼此堆叠在一起。诀窍在于如何在保持较小尺寸,且不需要引线的同时实现同一块功率裸片的顶部和底部的连接。

绝缘体上的功率芯片

绝缘层上的功率芯片( PSOI )是一类密封芯片级封装,采用不同的方法将电气连接放到同一侧(图 2 )。 PSOI 使用标准的加工工艺在同一侧开发有源区域,但采用顶部金属化融入此区域。然后将顶层通过附着一层顶层绝缘体进行密封和保护。外部金属化接触点被放在器件的底部,非常类似倒装芯片封装,但是有了 PSOI ,底部和两侧被隔离开,形成了独特的“晶圆级封装”。芯片可以以任何形式切开,如单锯,对偶、四边形等。这样消除了任何后期制造步骤。经过以晶圆的形式切割后,产品经测试,并采用合适的容器如松饼式或凝胶进行封装,可以随意拾取和放置。

顶部、底部和侧面的绝缘体将接合处与环境污染物和湿气隔离开。这一工艺无需引线连接和保护性涂层,从而缩小了整个芯片的尺寸。 PSOI 也可以采用顶部接触堆叠的方式制造,提供卓越的热特性和小尺寸,同时保持浪涌性能。这一过程提供了芯片 - 芯片的电气隔离并降低了寄生效应。总产出量必须与标准晶圆方式的产量不相上下,以匹配成本。与目前所用的封装技术相比,可将整体电路所占用的空间减少 20 %至 55 %。

- 基于中颖SH79F164单片机的电子血压计应用(07-01)

- 医疗电子发展方向(04-17)

- 世界首个固态量子处理器问世(07-13)

- 医疗电子技术大会折射行业发展方向(04-18)

- 医疗电子:梦想与现实的巨大鸿沟(07-16)

- “聪明的药丸”(07-20)