降低SoC中互连部分的功耗

时间:07-17

来源:互联网

点击:

作者: Jonah Probell,Arteris

虽然对系统级芯片开发人员来说电源管理的重要性越来越高,但有个关键区域经常被忽视,那就是互连。虽然大多数电源管理工作集中于SoC的运算部分,但采用更加模块化互连的设计师可以减小裸片尺寸、减轻布线拥塞,这就可以将总的芯片功耗最多降低达0.7mw。如此显著的功耗下降将成为下一代移动和功耗敏感性数据中心应用系统中的游戏规则改变者。

模块化概念有别于其它类型的互连,因为它由分布式架构的开关、缓冲器、防 火 墙、管线结构以及时钟和电源域交叉组成。通过在芯片上的所有独立单元之间使用通用传输协议,模块化方法可以帮助设计师实现单元级时钟选通,从而消除没有事务处理区域的时钟树开关功耗。

模块化片上网络级芯片(NoC)技术还能通过逻辑局部化、尽量缩短长的走线并保持低电容来降低功耗。想要进一步增强SoC设计的电源管理能力的设计师可以采取一定的措施减小芯片的面积和泄漏功耗,方法是使用NoC传输协议的简易性实现数据路径的串行化,进而最大程度地减少逻辑用量。

低功耗

目前常用的顶层互连结构一般都要依赖于较长的走线,而这些走线会消耗与它们在芯片上占用的逻辑区域面积不成比例的功耗。时钟树通常是互连内最大的功耗源,而时钟选通提供了降低功耗的最大潜力。另外,漏电功耗是第二大功耗源,减小这种结构所需的逻辑面积可以最大限度地减小漏电功耗。

采用模块化NoC互连的设计师可以从本文中了解到时钟树管理的局部化、数据路径的串行化和精确定位的管线结构所带来的功耗和面积方面的好处。

总线和交叉矩阵:互连历史简介

了解互连结构的历史就能知道模块化NoC设计的由来了,它能解决可扩展性问题。

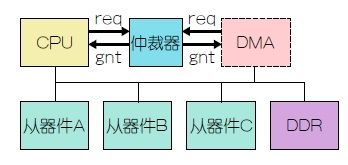

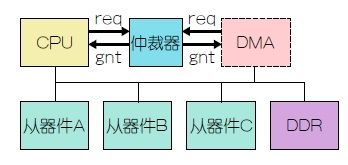

SoC是一种含CPU和外设的芯片,开发人员提出的接口协议标准可以将各单元链接在一起。借助新增总线主器件的推出,到外设的连接可以得到共享。控制对总线的访问要求一个中央仲裁器,比如在板级协议中使用的仲裁器。

图1:带仲裁器的共享型总线展示了访问控制为何要使用中央仲裁器。

随着时间的推移,SoC设计增加了越来越多的IP内核。由于这些设计变得越来越复杂,他们要求更多的总线接口。当对接口进行密集操作时,总线主器件可能会浪费很多时间等待对总线的访问权,即使在不同的主器件请求操作不同的从器件时,也是如此。

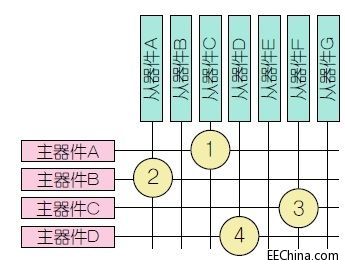

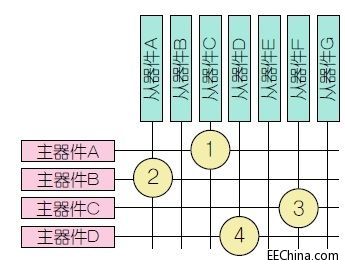

为了解决等待延时问题,交叉矩阵开关应运而生,它们支持在片上互连内不同的主和从器件之间开展并行访问。下面这个逻辑框图显示了4个主器件同时对4个不同从器件进行事务操作。

图2:SoC设计中的交叉矩阵开关逻辑视图,展示了每个从器件端复用器的关系。

从物理上看,交叉矩阵开关是用每个从器件端的复用器(mux)实现的。每个复用器以分布式仲裁机制与仲裁器相耦合。

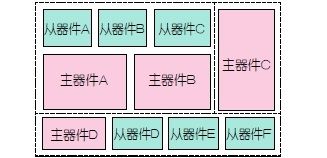

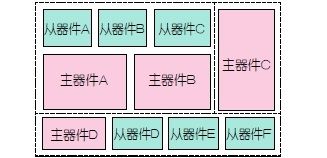

图3:4个主器件、6个从器件的交叉矩阵实现表明,在SoC周围采用完整数据路径的尺寸路由是不切实际的。

这种方法最多只能扩展到几个主和从器件接口。然而,除了特定数量外,在SoC周围路由完整数据路径的尺寸对布局布线来说也变得不切实际。

图4:随着功能清单的增长和IP模块的增加,SoC底层规划变得更加复杂。

对于具有很多个主/从接口的更加复杂的芯片来说,有必要在多个物理区域设计独立的互连,具体取决于IP内核分组的布局情况。不同区域之间的桥接提供了主器件和从器件之间必要的互连。

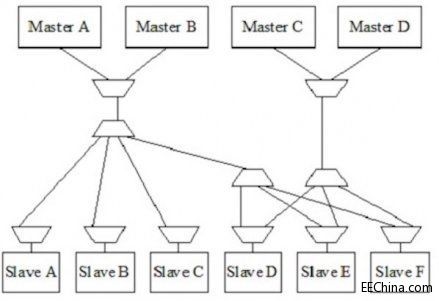

图5:4个主器件与6个从器件的互连,用了一个桥承载逻辑延时开销。

桥会为数据处理的增加延时周期,因为它们承载了逻辑延时部分。

交叉矩阵互连可以解决并行访问带来的系统架构问题,但在有大量主和从IP模块的情况下,又会造成芯片中的物理实现问题。

模块化设计和NoC

为了减小延时,地址可以在主接口侧解码,并转换为简单的路由ID号。片上的仲裁器-复用器和路由器-解复用器网络可以使用简单的路由ID,并通过链路芯片周围的简单伪开关复用器扩展路由分布。这样做还能实现更好的互连逻辑布局。对于芯片中越来越多的走线来说,布局越来越重要,因为它会使路由更加容易。

NoC互连可以同时解决这两个问题,因此在手机应用处理器、数字电视和机顶盒控制器等先进设计中得到了广泛使用。

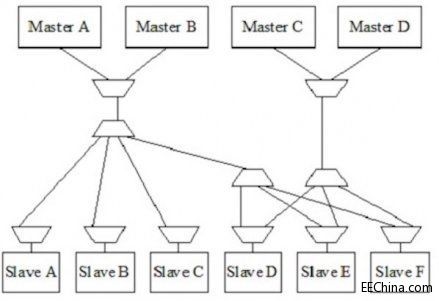

图6:利用一个NoC实现的4个主器件与6个从器件的互连。

设计师一直被要求在SoC中集成更多的功能,因此对互连技术的需求与日俱增。为了跟上形势,对以下功能的需求非常迫切:

●到不同事务处理协议的接口

●开关(解复用-路由器和仲裁器-复用器)

●QoS(优先级)

●缓冲器

●数据路径串行化

●统计性探测

●调试跟踪

●防 火 墙

●寄存器片(管线结构)

●时钟域交叉

●电压域

●电源域

这对互连设计提出了新的挑战。设计师希望IP可以重复使用并且可以重复配置。而在交叉矩阵逻辑中支持不断增加的功能要求将会提高复杂性,减慢关键路径速度。另外,许多走线即使在少量数据操作时也会被触发,因此消耗了与之不成比例的功耗。然而,可复用的模块化互连设计在简便性、速度、面积和功效方面有很大的优势,可克服传统总线和交叉矩阵技术的复杂性。

虽然对系统级芯片开发人员来说电源管理的重要性越来越高,但有个关键区域经常被忽视,那就是互连。虽然大多数电源管理工作集中于SoC的运算部分,但采用更加模块化互连的设计师可以减小裸片尺寸、减轻布线拥塞,这就可以将总的芯片功耗最多降低达0.7mw。如此显著的功耗下降将成为下一代移动和功耗敏感性数据中心应用系统中的游戏规则改变者。

模块化概念有别于其它类型的互连,因为它由分布式架构的开关、缓冲器、防 火 墙、管线结构以及时钟和电源域交叉组成。通过在芯片上的所有独立单元之间使用通用传输协议,模块化方法可以帮助设计师实现单元级时钟选通,从而消除没有事务处理区域的时钟树开关功耗。

模块化片上网络级芯片(NoC)技术还能通过逻辑局部化、尽量缩短长的走线并保持低电容来降低功耗。想要进一步增强SoC设计的电源管理能力的设计师可以采取一定的措施减小芯片的面积和泄漏功耗,方法是使用NoC传输协议的简易性实现数据路径的串行化,进而最大程度地减少逻辑用量。

低功耗

目前常用的顶层互连结构一般都要依赖于较长的走线,而这些走线会消耗与它们在芯片上占用的逻辑区域面积不成比例的功耗。时钟树通常是互连内最大的功耗源,而时钟选通提供了降低功耗的最大潜力。另外,漏电功耗是第二大功耗源,减小这种结构所需的逻辑面积可以最大限度地减小漏电功耗。

采用模块化NoC互连的设计师可以从本文中了解到时钟树管理的局部化、数据路径的串行化和精确定位的管线结构所带来的功耗和面积方面的好处。

总线和交叉矩阵:互连历史简介

了解互连结构的历史就能知道模块化NoC设计的由来了,它能解决可扩展性问题。

SoC是一种含CPU和外设的芯片,开发人员提出的接口协议标准可以将各单元链接在一起。借助新增总线主器件的推出,到外设的连接可以得到共享。控制对总线的访问要求一个中央仲裁器,比如在板级协议中使用的仲裁器。

图1:带仲裁器的共享型总线展示了访问控制为何要使用中央仲裁器。

随着时间的推移,SoC设计增加了越来越多的IP内核。由于这些设计变得越来越复杂,他们要求更多的总线接口。当对接口进行密集操作时,总线主器件可能会浪费很多时间等待对总线的访问权,即使在不同的主器件请求操作不同的从器件时,也是如此。

为了解决等待延时问题,交叉矩阵开关应运而生,它们支持在片上互连内不同的主和从器件之间开展并行访问。下面这个逻辑框图显示了4个主器件同时对4个不同从器件进行事务操作。

图2:SoC设计中的交叉矩阵开关逻辑视图,展示了每个从器件端复用器的关系。

从物理上看,交叉矩阵开关是用每个从器件端的复用器(mux)实现的。每个复用器以分布式仲裁机制与仲裁器相耦合。

图3:4个主器件、6个从器件的交叉矩阵实现表明,在SoC周围采用完整数据路径的尺寸路由是不切实际的。

这种方法最多只能扩展到几个主和从器件接口。然而,除了特定数量外,在SoC周围路由完整数据路径的尺寸对布局布线来说也变得不切实际。

图4:随着功能清单的增长和IP模块的增加,SoC底层规划变得更加复杂。

对于具有很多个主/从接口的更加复杂的芯片来说,有必要在多个物理区域设计独立的互连,具体取决于IP内核分组的布局情况。不同区域之间的桥接提供了主器件和从器件之间必要的互连。

图5:4个主器件与6个从器件的互连,用了一个桥承载逻辑延时开销。

桥会为数据处理的增加延时周期,因为它们承载了逻辑延时部分。

交叉矩阵互连可以解决并行访问带来的系统架构问题,但在有大量主和从IP模块的情况下,又会造成芯片中的物理实现问题。

模块化设计和NoC

为了减小延时,地址可以在主接口侧解码,并转换为简单的路由ID号。片上的仲裁器-复用器和路由器-解复用器网络可以使用简单的路由ID,并通过链路芯片周围的简单伪开关复用器扩展路由分布。这样做还能实现更好的互连逻辑布局。对于芯片中越来越多的走线来说,布局越来越重要,因为它会使路由更加容易。

NoC互连可以同时解决这两个问题,因此在手机应用处理器、数字电视和机顶盒控制器等先进设计中得到了广泛使用。

图6:利用一个NoC实现的4个主器件与6个从器件的互连。

设计师一直被要求在SoC中集成更多的功能,因此对互连技术的需求与日俱增。为了跟上形势,对以下功能的需求非常迫切:

●到不同事务处理协议的接口

●开关(解复用-路由器和仲裁器-复用器)

●QoS(优先级)

●缓冲器

●数据路径串行化

●统计性探测

●调试跟踪

●防 火 墙

●寄存器片(管线结构)

●时钟域交叉

●电压域

●电源域

这对互连设计提出了新的挑战。设计师希望IP可以重复使用并且可以重复配置。而在交叉矩阵逻辑中支持不断增加的功能要求将会提高复杂性,减慢关键路径速度。另外,许多走线即使在少量数据操作时也会被触发,因此消耗了与之不成比例的功耗。然而,可复用的模块化互连设计在简便性、速度、面积和功效方面有很大的优势,可克服传统总线和交叉矩阵技术的复杂性。

电源管理 SoC 电容 总线 数字电视 机顶盒 电压 电路 EDA 电流 解码器 相关文章:

- 嵌入式系统电源管理软件比较(02-16)

- 在异步SRAM中实现速度与功耗的完美平衡(01-03)

- SoC:IP是新的抽象(10-24)

- 图形化系统设计加速应用实现和创新(11-04)

- 如何提高芯片级封装集成电路的热性能(03-16)

- 14nm的FPGA需要什么样的电源管理IC?(06-04)