适用于系统级验证的VMM多层框架

时间:11-16

来源:互联网

点击:

作者:ADI公司 Ashok Chandran,Sajeev Thomas,Saj Kapoor

基于验证方法手册(VMM)的验证是非常有效的模块级验证环境实现方法。在系统级采用模块级验证组件可显著改善验证质量,缩短满足系统级覆盖率所需的时间。但是,这种方法也给系统级测试平台带来了一系列需要应对的挑战,包括运行时间、随机化质量、系统存储器管理、多寄存器访问接口、时钟域和随机稳定性。此外,模块到系统的重用方法应当简单、可扩展。

对于具有专有内核和系统接口的片上系统(SoC),通过汇编语言编码进行各种外围器件不同模式下的测试并不是一个可扩展的解决方案,也不大适合基于VMM的流程。在VMM流程中,会出现多个仿真线程同时访问外设的情况。例如,在配置一个外设时,可能有另一个线程正在读取同一寄存器空间以检查中断状态。在汇编测试中,一个内核只有一个指令流,因此无法模拟这种行为。本文所述方法将内核替换为总线功能模型(BFM),直接驱动系统接口总线。每个模块测试平台在不同的线程中处理,并可以访问相应的外围组件。采用VMM寄存器抽象层(RAL)可确保由模块级测试平台迁移到系统级时,仅发生极小的行为改变。

系统测试平台需要根据外设要求对系统组件进行编程。例如,通用异步接收机/发射机(UART)模块在发射之前,需要配置直接存储器访问(DMA)引擎并且初始化存储器。由于系统架构是所有外设的公用资源,因此提供一个统一的平台和一些实用任务来根据外设要求配置系统会更合理。多层架构能够确保系统支持每个外围组件。同时各层实现了随机化,确保系统和外设覆盖率最大化。

环境针对性能进行了优化,支持线程管理、条件编译和模块级测试平台的即插即用。因此,这是一种自下而上的方法,模块级需要遵守一套基本但宽泛的原则,以便简化集成。

本文将介绍传统的系统级验证方法,并说明改进的新方法,进一步阐述分层架构及其优势。本文还将讨论通过适当的线程和存储器管理来改善运行时间的技术,以及利用分离编译和多核编译技术解决编译时间较长问题的方法。最后,本文将涉及该测试平台如何利用VMM录制/回放方法来避免随机稳定性问题,以及如何支持汇编格式的测试转储。

设计详情

本文考虑的设计是一个复杂的通用SoC,它包含多个内核、一个中断控制器、大量专有外设模块、L1/L2/L3存储器、存储器控制器、DMA引擎和多个IP(知识产权)模块。一些模块可以通过内置的DMA引擎访问系统存储器,另一些模块则使用系统DMA引擎访问存储器。虽然没有明确显示,但外设与存储器之间有多个仲裁层。

该芯片还有多个模块、电源和用于仲裁的系统交叉开关,如图1的简化示意图所示。外部引脚通过多路复用方案由多个外设共用。

图1 :设计概览。

系统级验证挑战

系统级验证旨在验证系统配置与外设模式的不同组合,这会揭示许多有意义的情况,其中包括:

是否经历了所有可能影响外设的系统配置模式下的外设模式?

1.关于连接是否存在遗漏?一旦处在特定的系统/外设配置下,该连接就可能变得可见。

2.是否所有模块都已连接到适当的时钟域?

3.当多个外设为获得系统资源而竞争时,系统中是否存在带宽问题?

4.每个DMA/外设都有对整个存储器空间的读写权限吗?

5.系统内的所有寄存器都可以访问吗?

6.是否会产生流量模式,从而验证系统真正支持使用案例?

7.模块是否采用了在系统上无效的行为,或者模块是否看到了它不是为此而设计的行为?

由于涉及到大量组合,对于如此复杂的SoC利用定向测试来验证上述各种情况是不可行的。

使用模块级VMM测试平台可在系统级提供良好的覆盖率,但是随着模块数量的增加,将会带来一系列全新的挑战。

1.系统编程应与外设模式相关。例如,针对接收模式下的一个外设,需要在存储器写入模式下对DMA进行编程。当模块级测试平台在系统级工作时,将系统配置信息封装在外设交易(transaction)类中,这种分层方法提供一种可在所有模块上实现的通用方法。

2.大量模块子环境和线程一起运行必然会拖慢仿真,因此必须对线程进行管理,确保只有活动的测试平台占用CPU周期。

3.庞大的测试平台和复杂的设计会导致编译时间过长,形成严重的开发瓶颈,必须利用工具的高级特性来克服这一障碍。

4.寄存器访问机制必须对所有模块和系统测试平台一致。VMM RAL提供了合理的解决方案,消除了寄存器访问的物理接口在模块级与系统级之间改变时的所有问题。

5.引起故障的测试案例必须能够再现,以充分验证解决办法有效性。

多层框架

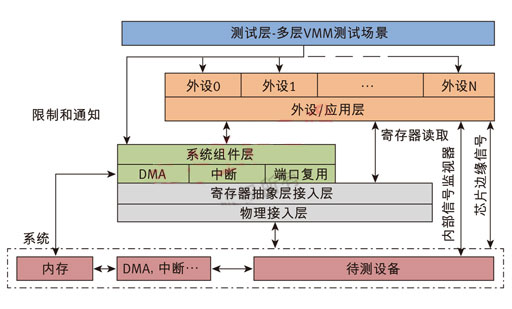

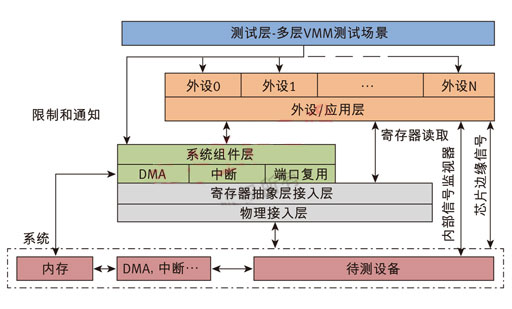

测试平台组件在不同层工作。图2所示的分层架构支持模块到系统重用和系统级的即插即用功能。下面将从下至上描述各个不同的层。

图2:分层架构。

1. VMM寄存器抽象层

此层处理基于RAL的寄存器读写操作。RAL对于测试平台从模块到系统的重用起着重要的促进作用。测试平台独立于物理总线协议。高级RAL交易转化为RAL访问层内的物理层交易。物理层交易描述物理协议(如APB、AHB和AXI等)。物理层利用RAL访问层提供的交易驱动总线信号。

2. 系统组件层

此层管理所有系统组件,如DMA、存储器和中断控制器等。该层与软件API相似,提供一套任务、对象、协议和原则用于系统管理。例如,请求n个数据项将转换为适当的DMA编程,利用所需数据初始化存储器并处理DMA中断。该层还增加了数据校验以验证数据路径,并向外设层显示中断。

3. 外设层

此层管理模块级子环境(subenv)。它还能同步系统事件,如中断和利用模块级子环境进行配置等。

4. 测试层

此层利用VMM方案和多流方案发生器(MSSG)产生随机交易。通过对外设属性和系统配置应用限制条件,能够产生定向随机方案。

基于验证方法手册(VMM)的验证是非常有效的模块级验证环境实现方法。在系统级采用模块级验证组件可显著改善验证质量,缩短满足系统级覆盖率所需的时间。但是,这种方法也给系统级测试平台带来了一系列需要应对的挑战,包括运行时间、随机化质量、系统存储器管理、多寄存器访问接口、时钟域和随机稳定性。此外,模块到系统的重用方法应当简单、可扩展。

对于具有专有内核和系统接口的片上系统(SoC),通过汇编语言编码进行各种外围器件不同模式下的测试并不是一个可扩展的解决方案,也不大适合基于VMM的流程。在VMM流程中,会出现多个仿真线程同时访问外设的情况。例如,在配置一个外设时,可能有另一个线程正在读取同一寄存器空间以检查中断状态。在汇编测试中,一个内核只有一个指令流,因此无法模拟这种行为。本文所述方法将内核替换为总线功能模型(BFM),直接驱动系统接口总线。每个模块测试平台在不同的线程中处理,并可以访问相应的外围组件。采用VMM寄存器抽象层(RAL)可确保由模块级测试平台迁移到系统级时,仅发生极小的行为改变。

系统测试平台需要根据外设要求对系统组件进行编程。例如,通用异步接收机/发射机(UART)模块在发射之前,需要配置直接存储器访问(DMA)引擎并且初始化存储器。由于系统架构是所有外设的公用资源,因此提供一个统一的平台和一些实用任务来根据外设要求配置系统会更合理。多层架构能够确保系统支持每个外围组件。同时各层实现了随机化,确保系统和外设覆盖率最大化。

环境针对性能进行了优化,支持线程管理、条件编译和模块级测试平台的即插即用。因此,这是一种自下而上的方法,模块级需要遵守一套基本但宽泛的原则,以便简化集成。

本文将介绍传统的系统级验证方法,并说明改进的新方法,进一步阐述分层架构及其优势。本文还将讨论通过适当的线程和存储器管理来改善运行时间的技术,以及利用分离编译和多核编译技术解决编译时间较长问题的方法。最后,本文将涉及该测试平台如何利用VMM录制/回放方法来避免随机稳定性问题,以及如何支持汇编格式的测试转储。

设计详情

本文考虑的设计是一个复杂的通用SoC,它包含多个内核、一个中断控制器、大量专有外设模块、L1/L2/L3存储器、存储器控制器、DMA引擎和多个IP(知识产权)模块。一些模块可以通过内置的DMA引擎访问系统存储器,另一些模块则使用系统DMA引擎访问存储器。虽然没有明确显示,但外设与存储器之间有多个仲裁层。

该芯片还有多个模块、电源和用于仲裁的系统交叉开关,如图1的简化示意图所示。外部引脚通过多路复用方案由多个外设共用。

图1 :设计概览。

系统级验证挑战

系统级验证旨在验证系统配置与外设模式的不同组合,这会揭示许多有意义的情况,其中包括:

是否经历了所有可能影响外设的系统配置模式下的外设模式?

1.关于连接是否存在遗漏?一旦处在特定的系统/外设配置下,该连接就可能变得可见。

2.是否所有模块都已连接到适当的时钟域?

3.当多个外设为获得系统资源而竞争时,系统中是否存在带宽问题?

4.每个DMA/外设都有对整个存储器空间的读写权限吗?

5.系统内的所有寄存器都可以访问吗?

6.是否会产生流量模式,从而验证系统真正支持使用案例?

7.模块是否采用了在系统上无效的行为,或者模块是否看到了它不是为此而设计的行为?

由于涉及到大量组合,对于如此复杂的SoC利用定向测试来验证上述各种情况是不可行的。

使用模块级VMM测试平台可在系统级提供良好的覆盖率,但是随着模块数量的增加,将会带来一系列全新的挑战。

1.系统编程应与外设模式相关。例如,针对接收模式下的一个外设,需要在存储器写入模式下对DMA进行编程。当模块级测试平台在系统级工作时,将系统配置信息封装在外设交易(transaction)类中,这种分层方法提供一种可在所有模块上实现的通用方法。

2.大量模块子环境和线程一起运行必然会拖慢仿真,因此必须对线程进行管理,确保只有活动的测试平台占用CPU周期。

3.庞大的测试平台和复杂的设计会导致编译时间过长,形成严重的开发瓶颈,必须利用工具的高级特性来克服这一障碍。

4.寄存器访问机制必须对所有模块和系统测试平台一致。VMM RAL提供了合理的解决方案,消除了寄存器访问的物理接口在模块级与系统级之间改变时的所有问题。

5.引起故障的测试案例必须能够再现,以充分验证解决办法有效性。

多层框架

测试平台组件在不同层工作。图2所示的分层架构支持模块到系统重用和系统级的即插即用功能。下面将从下至上描述各个不同的层。

图2:分层架构。

1. VMM寄存器抽象层

此层处理基于RAL的寄存器读写操作。RAL对于测试平台从模块到系统的重用起着重要的促进作用。测试平台独立于物理总线协议。高级RAL交易转化为RAL访问层内的物理层交易。物理层交易描述物理协议(如APB、AHB和AXI等)。物理层利用RAL访问层提供的交易驱动总线信号。

2. 系统组件层

此层管理所有系统组件,如DMA、存储器和中断控制器等。该层与软件API相似,提供一套任务、对象、协议和原则用于系统管理。例如,请求n个数据项将转换为适当的DMA编程,利用所需数据初始化存储器并处理DMA中断。该层还增加了数据校验以验证数据路径,并向外设层显示中断。

3. 外设层

此层管理模块级子环境(subenv)。它还能同步系统事件,如中断和利用模块级子环境进行配置等。

4. 测试层

此层利用VMM方案和多流方案发生器(MSSG)产生随机交易。通过对外设属性和系统配置应用限制条件,能够产生定向随机方案。

- 日立公司采用ADI的高性能Blackfin处理复杂算法及繁重I/O负载(01-16)

- ADI诠释DSP技术针对热点应用的五大竞争法宝(04-21)

- 中国仪控产业蕴含巨大商机,ADI DSP助跑本土军团(05-25)

- ADI常用DDS的线性扫频特性比较研究(04-16)

- ADI Blackfin?处理器架构概述 (07-12)

- DSP热点应用的五大竞争法宝(02-05)