高效率高谐波抑制功率放大器的设计

的部分为片内实现,方框外的部分采用多层基板、绑定线和贴片元件来实现。对于级间 匹配网络,匹配电感于外部绑定线实现有助于减少级间匹配网络的插损,获得了较高的效率和功率,同时调试灵活方便。对于输出匹配网络,其中L4由绑定线和基 板上的传输线共同组成,通过调节金线的长度,可以控制二次谐波分量的大校而对于L3和L2,由于该网络是对高次谐波进行抑制,所需电感较小,主要是由多 层基板的过孔构成。

2 测试结果

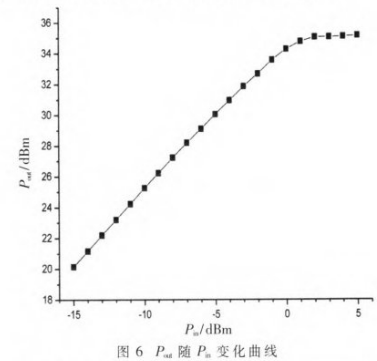

本芯片采用InGaP/GaAs HBT工艺制作,图4为芯片实物图,DIE面积为1 mm×1 mm,整体封装大小为4 mm×4 mm。图5为本设计S参数测试结果,测试平台为安捷伦矢量网络分析仪E5071C。测试结果表明,在2 GHz频率处该设计的S参数为:S21=35.1 dB,S11<-10 dB,S22<-10 dB,从S参数看出本设计获得了很好的小信号性能。图6为输出功率和输入功率的关系图,从图可知当Pin小于0 dBm时,放大器工作于线性工作状态,当Pin大于0时开始出现压缩,到达3 dBm时,输出功率已经饱和,此时Pout=35.2 dBm,放大器的1 dB压缩点为P1dB=34.2 dBm。

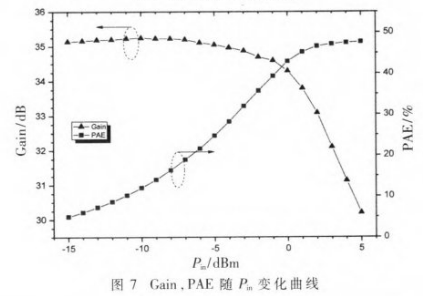

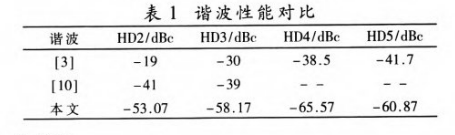

从该图可知,该放大器获得了较好的线性度。图7为增益Gain和效率PAE随着输入功率的变化的曲线图,该图表明该设计的增益在Pin<0 dBm时,增益波动小于0.2 dB,表明该设计获得了很好的AM-AM,在饱和工作时,即Pout=35.2 dBm时,效率为PAE=48%;工作于1 dB压缩点时,即Pout=34.2 dBm时,效率为PAE=43%。从效率曲线图可知,该放大器不但在饱和工作时获得了很高的效率,在线性工作时也获得了很好的效率。表1是该设计的谐波性 能与其他设计的比较,从表1可知本设计在考虑二次谐波同时还兼顾了高次谐波,达到了良好的谐波抑制,特别是在对高次谐波的处理上。

3 总结

本文通过在功率放大器的输出匹配网络中引入多个LC谐振网络来对功率放大器的谐波能量进行回收和利用,提高了功率放大器的效率,抑制了负载端的谐波分 量。该方法简单,易于实现及利于功率放大器的小型化。利用该方法设计了一个工作于2 GHz频率的功率放大器,该功率放大器的实测结果为:增益为Gain=35 dB,1 dB压缩点为P1dB=34.2 dBm,饱和工作时效率为PAE=48%,各次谐波分量大小分别为:HD2=-53 dBc、HD3=-58 dBc、HD4=-65 dBc、HD5=-60 dBc。测试结果表明,该方法设计的功率放大器获得了很好的效率和谐波性能。

功率放大器 效率 谐波抑制 InGaP GaAs HBT 相关文章:

- WCDMA基站天线和多载波功率放大器方案(02-03)

- Avago ACPM-7355 HSPA双频段功率放大方案(07-05)

- Anadigics AWT6241 TD-SCDMA手机线性功率放大方案(07-26)

- Cree应用AWR软件设计GaN高功率放大器 效率提高达70%(10-06)

- AWR软件助力R&S设计和优化新型宽带功率放大器关键器件(03-13)

- 仿真图解:高增益0.5W驱动放大器为什么适合Pico cell(11-05)