频率合成器的高性能架构实现技术

近端杂散信号进行少许衰减或不做额外衰减。这样,PLL的环路带宽可以保持比传统PLL合成器中的实际带宽大许多,从而提高频率切换速度。PLL参考频率可以做得比DDS频率步长高出许多,分频比则非常小,从而实现优异的相位噪声性能。由于更大的环路带宽等同于特定偏移处更大的环路增益,而且来自相位检测器的噪声贡献更低,因此VCO贡献的噪声成份也可以得到有效降低。

值得注意的是,对这种架构中的频率规划细节必须仔细斟酌。参考振荡器、DDS时钟源和PLL参考源的频率必须相对于要求的信道间隔加以仔细选择,以便最大限度地降低所需参考发生硬件的复杂性,避免产生不能被滤除的近端杂散信号。

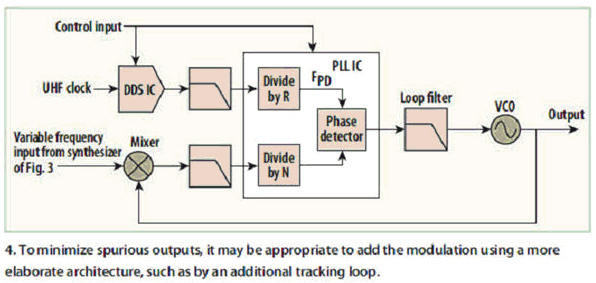

如上所述,许多DDSIC具有频率和相位调制功能,而这些功能可能在要求调制后输出的场合用得到,例如产生频率调制连续波(FMCW)雷达系统要求的线性频率斜坡场合。在实际应用中,为了尽量减少杂散信号输出,最好是增加使用更精巧架构的调制电路,比如通过额外的跟踪环路,如图4所示。

图4、为了尽量减少杂散输出,正确的做法是增加使用更加精巧架构的调制电路,比如通过额外的跟踪环路。

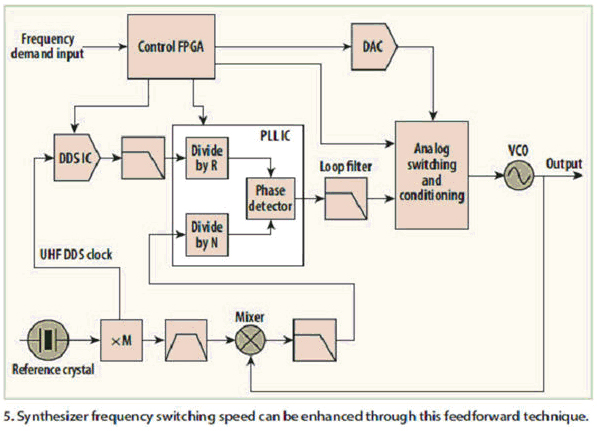

特别是在宽带系统中,通过使用前馈技术可以极大地提高频率切换速度,案例见图5。当接收到一个改变频率的命令时,环路被断开,VCO控制电压随后受DAC的控制,并到达一个预期对应所需新输出频率的值。接着环路再次闭合,同时PLL开始消除任何残留的相位与频率误差。在实际应用中,控制电压会很快调整到接近要求的值,而且由于PLL只需消除很小的残留误差,因此系统总的稳定时间将得到显著缩短。注意,除了加快稳定过程外,这种安排实际上在环路中使用许多频率转换级的宽带系统中已被证明是非常有用的,而如果不这样做的话,PLL可能没有足够的捕获带宽来稳定大的步长。为了实现信道改变过程中严格受控的时间顺序,控制逻辑功能最好由FPGA来完成。在实际使用时,对于拥有串行控制接口的器件来说,写入要求的寄存器数据所需的时间可能是决定可以实现的切换时间中最重要的因素。

图5、通过这种前馈技术可以提高合成器的频率切换速度。

基于上述技术的实用微波频率合成器可以同时实现低杂散信号电平、很快的切换速度和优秀的相位噪声,同时还能提供频率调制(FM)和相位调制功能。通过仔细地选择架构和频率规划,同时在基于现场可编程门阵列(FPGA)的逻辑控制下使用现代PLL合成器和DDSIC,我们完全可以在高功效和高空间效率的封装中实现这种高性能的设计(图6)。

图6、在FPGA控制的架构中组合使用PLL和DDSIC能以高功效和高空间效率的封装提供所需的性能等级。

频率合成器 相关文章:

- 基于单片机的直接数字频率合成器的设计(11-14)

- 精密频率合成技术助力多通道频率合成器的应用(06-08)

- 基于PE3236的L波段频率合成器的设计(08-29)

- 基于锁相环的频率合成器的设计(08-28)