复杂电源管理组件的设计挑战及解决方案

时间:12-06

来源:互联网

点击:

随着系统内电源数量的增多,为了确保其安全、经济、持续和正常的工作,对电源轨进行监测和控制变得非常重要,特别是在使用微处理器时。确定电压轨是否处于工作范围内,以及该电压相对于其它电压轨是否按照正确的时序上电或断电,这些对于系统执行的可靠性和安全性来说都是至关重要的。例如FPGA,在向组件提供5V I/O(输入/输出)电压之前,必须先施加3.3V的核心电压,并持续至少20ms,以避免组件上电时受到损坏。对于系统的可靠性来说,满足这样的时序要求就像要保证组件在规定的电源电压和温度范围内工作一样至关重要。

同时,电源轨数量也在显著增加。一些复杂的系统,如LAN(局域网络)交换机和移动电话基站,线路卡通常会包含10路或更多电压轨;即使是对成本敏感的消费性系统,如等离子电视,也可能具有多达15路的独立电压轨,其中许多电压轨都需要进行监控和时序控制。在高阶系统中,每个DSP组件会需要多达四个独立的电源。而在更多情况下,单一系统中可能存在着大量的多电源组件,包括FPGA、ASIC、DSP、微处理器和微控制器(以及模拟组件)。

电压监控和时序控制有时会变得极为复杂,特别是当一个系统必须设计为能够支持上电时序控制和断电时序控制,并能够在工作期间的不同时间点上对不同电源轨上的所有可能故障状况均产生多种响应时。中心电源管理控制器是解决这个难题的最佳方案。

设计风险与电源数量、组件数量和系统复杂程度成正比,外部因素也会增加风险。例如,如果在初始设计阶段没有完整地定义出主ASIC的特性,那么电源设计工程师必须用硬联机实现电压监控阈值和时序控制,但这些都可能会随着ASIC技术指标的改变而产生变化。故对于任何一个中心电源系统管理器来说,易于调整电源的方法将会是非常有用的。

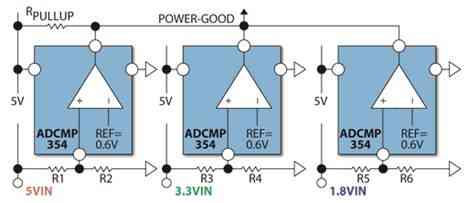

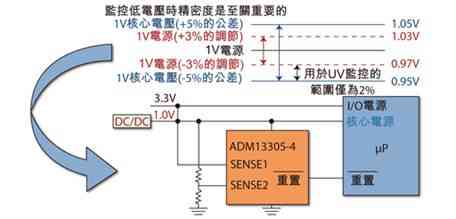

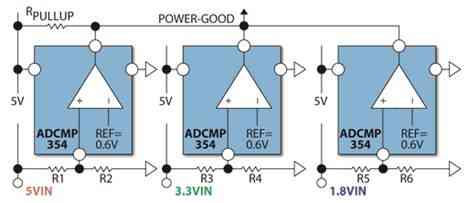

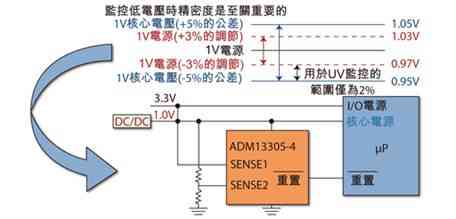

基本监控

图1所示的是监控多任务电压轨的简单方法。其中,每路电压轨都使用独立的电路。电阻分压器将电压轨按比例降低,并为每一路电源设置一个欠压跳变点。所有的输出被连接在一起,产生通用电源良好讯号。更小的制程尺寸正推动核心电压向更低的方向发展。低压时余量的不足可能会引起预想不到的组件行为。随着核心电压的下降,对高精密度电压监控器的要求将更加苛刻,如图2所示。

图1:基于比较器的欠压检测,提供通用电源良好输出,适用于3路电源系统。

图2:现代电子系统中需要高精密度监控器。

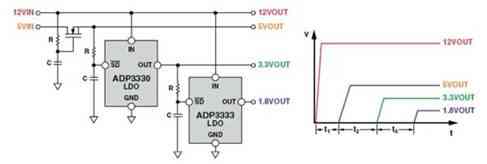

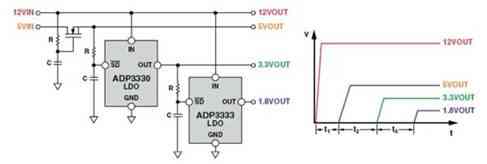

基本时序控制

图3所示的是如何利用分离组件实现基本的时序控制,此处采用逻辑阈值而不是比较器。12V和5V电源轨是由其它电路产生的。为了确保系统能够正确工作,必须导入一段时间延迟。这里是透过使用RC电路来缓慢升高与5V电源串联的N信道FET的闸极电压而实现的。所选用的RC值可确保FET在达到阈值电压并导通之前能获得足够的延迟时间。这些电压的上电时间也是利用RC来进行时序控制的。由于RC能驱动每个LDO的EN(使能)接脚,因此无需串联FET。选定的RC值要确保在EN接脚上的电压爬升到其阈值之前有足够的延迟时间(t2,t3)。

图3:四路电源系统的基本分离式时序控制。

这种简单、低成本的电源时序控制方法只占用很少的电路板面积,因此适用于多种应用。这种方法适合于成本是主要考虑因素、时序要求很简单,且时序控制电路的精确性不是十分重要的系统。

但许多情况下需要比RC延迟电路更高的精确性。此外,这种简单的解决方案也不允许以结构化的方法处理故障(例如,一个5V电源失效最终将影响到其它电源轨)。

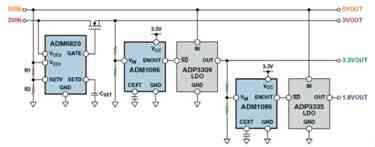

利用IC进行时序控制

市场上有各种各样的电源时序控制器。有些组件能够直接实现电源模块的输出,并提供多种输出配置。有些组件内建电荷泵电压产生器,对于需要对更高电压轨进行时序控制、却又缺少高压源(如12V电源轨)的低压系统来说,这一点特别有用,能够驱动N信道FET的闸极。许多这类组件具有使能接脚,可以接受来自于按钮开关或控制器的外部讯号,以便在需要时重新启动时序控制或切断所控制的电压轨。

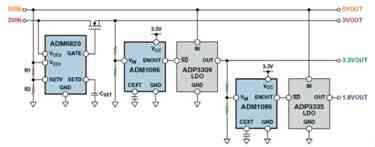

图4所示的是如何使用电源时序控制器ADM6820和ADM1086精确且可靠地对系统中的电源轨进行时序控制。内部比较器检测电压轨何时会超过精密的设定电平,经过可程序的上电延迟之后,按正确时序产生输出。阈值透过电阻比值来设定,延迟透过电容来设定。

图4:使用监控IC对四路电源系统进行时序控制。

整合的电源系统管理

有些系统具有许多电源轨,采用这种使用大量IC,并利用电阻和电容来设置时序和阈值电平的分离解决方案会变得过于复杂、成本过高,且不能提供适当的性能。

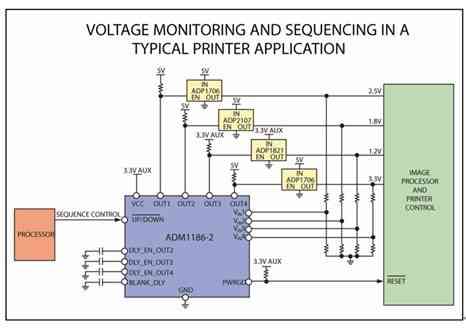

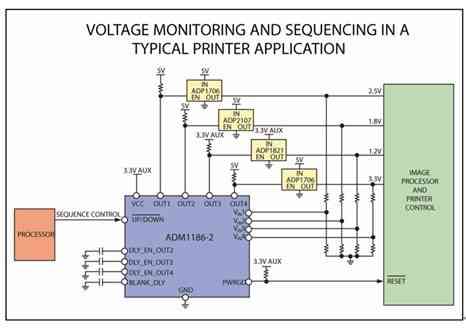

具有八路电压轨的系统会需要复杂的上电时序控制。每路电压轨都要监控,以免出现欠压或过压故障。产生故障时,根据故障机制,需要切断所有电源电压,或初始化电源切断时序。此外,必须根据控制讯号的状态采取相应措施,并根据电源的状态产生标志位。在具有四路或更多电源的系统中,使用集中式组件来管理电源比较可取。图5所示的是采用这种方法的一个例子。

图5:打印机应用中的上电与断电时序。

同时,电源轨数量也在显著增加。一些复杂的系统,如LAN(局域网络)交换机和移动电话基站,线路卡通常会包含10路或更多电压轨;即使是对成本敏感的消费性系统,如等离子电视,也可能具有多达15路的独立电压轨,其中许多电压轨都需要进行监控和时序控制。在高阶系统中,每个DSP组件会需要多达四个独立的电源。而在更多情况下,单一系统中可能存在着大量的多电源组件,包括FPGA、ASIC、DSP、微处理器和微控制器(以及模拟组件)。

电压监控和时序控制有时会变得极为复杂,特别是当一个系统必须设计为能够支持上电时序控制和断电时序控制,并能够在工作期间的不同时间点上对不同电源轨上的所有可能故障状况均产生多种响应时。中心电源管理控制器是解决这个难题的最佳方案。

设计风险与电源数量、组件数量和系统复杂程度成正比,外部因素也会增加风险。例如,如果在初始设计阶段没有完整地定义出主ASIC的特性,那么电源设计工程师必须用硬联机实现电压监控阈值和时序控制,但这些都可能会随着ASIC技术指标的改变而产生变化。故对于任何一个中心电源系统管理器来说,易于调整电源的方法将会是非常有用的。

基本监控

图1所示的是监控多任务电压轨的简单方法。其中,每路电压轨都使用独立的电路。电阻分压器将电压轨按比例降低,并为每一路电源设置一个欠压跳变点。所有的输出被连接在一起,产生通用电源良好讯号。更小的制程尺寸正推动核心电压向更低的方向发展。低压时余量的不足可能会引起预想不到的组件行为。随着核心电压的下降,对高精密度电压监控器的要求将更加苛刻,如图2所示。

图1:基于比较器的欠压检测,提供通用电源良好输出,适用于3路电源系统。

图2:现代电子系统中需要高精密度监控器。

基本时序控制

图3所示的是如何利用分离组件实现基本的时序控制,此处采用逻辑阈值而不是比较器。12V和5V电源轨是由其它电路产生的。为了确保系统能够正确工作,必须导入一段时间延迟。这里是透过使用RC电路来缓慢升高与5V电源串联的N信道FET的闸极电压而实现的。所选用的RC值可确保FET在达到阈值电压并导通之前能获得足够的延迟时间。这些电压的上电时间也是利用RC来进行时序控制的。由于RC能驱动每个LDO的EN(使能)接脚,因此无需串联FET。选定的RC值要确保在EN接脚上的电压爬升到其阈值之前有足够的延迟时间(t2,t3)。

图3:四路电源系统的基本分离式时序控制。

这种简单、低成本的电源时序控制方法只占用很少的电路板面积,因此适用于多种应用。这种方法适合于成本是主要考虑因素、时序要求很简单,且时序控制电路的精确性不是十分重要的系统。

但许多情况下需要比RC延迟电路更高的精确性。此外,这种简单的解决方案也不允许以结构化的方法处理故障(例如,一个5V电源失效最终将影响到其它电源轨)。

利用IC进行时序控制

市场上有各种各样的电源时序控制器。有些组件能够直接实现电源模块的输出,并提供多种输出配置。有些组件内建电荷泵电压产生器,对于需要对更高电压轨进行时序控制、却又缺少高压源(如12V电源轨)的低压系统来说,这一点特别有用,能够驱动N信道FET的闸极。许多这类组件具有使能接脚,可以接受来自于按钮开关或控制器的外部讯号,以便在需要时重新启动时序控制或切断所控制的电压轨。

图4所示的是如何使用电源时序控制器ADM6820和ADM1086精确且可靠地对系统中的电源轨进行时序控制。内部比较器检测电压轨何时会超过精密的设定电平,经过可程序的上电延迟之后,按正确时序产生输出。阈值透过电阻比值来设定,延迟透过电容来设定。

图4:使用监控IC对四路电源系统进行时序控制。

整合的电源系统管理

有些系统具有许多电源轨,采用这种使用大量IC,并利用电阻和电容来设置时序和阈值电平的分离解决方案会变得过于复杂、成本过高,且不能提供适当的性能。

具有八路电压轨的系统会需要复杂的上电时序控制。每路电压轨都要监控,以免出现欠压或过压故障。产生故障时,根据故障机制,需要切断所有电源电压,或初始化电源切断时序。此外,必须根据控制讯号的状态采取相应措施,并根据电源的状态产生标志位。在具有四路或更多电源的系统中,使用集中式组件来管理电源比较可取。图5所示的是采用这种方法的一个例子。

图5:打印机应用中的上电与断电时序。

电压 FPGA DSP 电源管理 电路 电阻 比较器 电子 LDO 电源模块 电容 LED DAC ADI ADC 相关文章:

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)