DC-DC有源箝位正激拓扑技术

时间:11-14

来源:互联网

点击:

提供“电压为5V随着分布式电源系统 (DPS)在当今的电信、网络和计算设备中出现,对高效功率转换的需求日益紧迫。本文概述了分布式电源架构的趋势,介绍了一个高效DC-DC变换器的实例,并提供了设计方程、原理图和性能结果。

一、分布式电源系统的演变和发展趋势

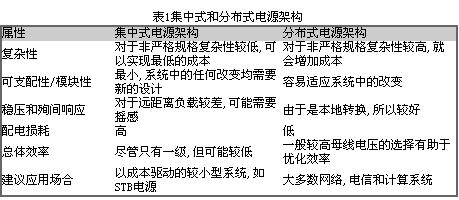

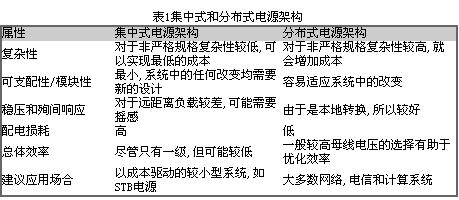

传统的功率转换系统是集中式电源系统,其中,单个电源从输入交流线路向所有需要的输出提供功率转换。随着电源电平的上升和负载电压的下降,提供接近于负载的功率转换非常重要,以便满足稳压要求并减小配电损耗。分布式电源系统由此产生并占据了主导地位,典型的应用例子是计算机电源。在计算机电源中,由非常接近处理器的稳压模块(VRM)提供最终转换。当然,DPS中常见的架构是48 V分布式电源。表1总结了集中式和分布式电源系统的差异。

48V架构继续成为电信市场的主导,并且已经适用于许多网络和高端计算应用中。图1给出了48V分布式电源的架构,在系统前端包括具有功率因数修正(PFC)的隔离式AC-DC变换,以满足减少谐波的要求。乍看之下,在AC-DC变换中加入PFC前端增加了系统的成本、复杂性和潜在效率损失。但是,通过提供预稳压和减小输入端峰值电流,PFC电路实际上有助于优化系统性能。在功率较低(< 250 W)的情况下,系统的成本和性能可以通过使用安森美半导体的NCP1651中独有的单级方法加以优化 。

板上电源架构包括从48V母线进行的隔离DC-DC转换。尽管48V母线应该已经妥善稳压(±5%),电信系统也要求通过电池备份进行工作,结果导致板上DC-DC变换器的输入电压规格更宽(一般为36??72V)。处理这么宽的电压范围对DC-DC 变换器提出了独特的挑战。此外,电压较低(<3.3V)、电流较大(>30A)的输出也使实现高效的功率转换变得更加困难。虽然设计这些变换器是可行的,但是挑战并不仅仅来自于电路设计,还必须特别关注EMI、散热和封装问题,以获得最优的性能。硅技术和无源元件的进步以及封装和电源拓扑结构方面的创新,使DC-DC 变换器的功率密度在近年来急剧增加。

图1 48V分布式架构

在过去几年中,分布式电源系统开始根据不同的应用而的采用了不同的形式和形状。对于不限制使用电池备份选项的应用(如网络和一些电信局端的应用)而言,12V和24V母线系统已被广泛采用。使用更低的母线电压增加了母线电流,功率较低的系统是可以接受的。有了分布式电源系统,板上DC-DC转换无需隔离,而且简化了实现方法。另一方面,由于输出电压接近1V,从 48V到1V的转换并不是非常有效和经济,许多系统现在都包含中间电源架构。

二、DC-DC变换器的设计考虑

无论分布式电源系统中的DC-DC变换器是否产生最终逻辑电压(如3.3V 或 2.5V)或上文提及的中间母线电压,这种类型的功率变换器均需要进行特殊的设计考虑。这些变换器倾向于具有特殊的元件高度限制、隔离要求、效率要求和尺寸限制,这些都要求在变换器设计的方方面面都采用创新的方法。

设计这类变换器的首要考虑事项应该是选择拓扑结构。由于传统的正激或反激拓扑结构成本较低,设计中可以考虑加以采用,但是它们在功率传输能力上受到限制,而且硬切换也影响了效率。由于转换效率取决于最优的变压器核心使用率,这些拓扑结构只在一个方向激发变压器核心,从而限制了功率通过率。另一方面,真正的双端拓扑结构(如半桥和推拉式拓扑结构)允许更小的输出电感和完全的变压器利用率。尽管这两种拓扑结构需要两个开关,但在高功率变换器中,通常还是采用这些拓扑结构。半桥促使高端驱动的要求,而推拉则在开关上施加双倍的最大输入电压。

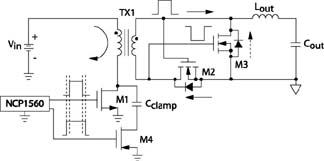

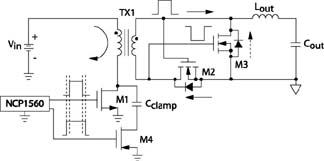

在上述所有方法中,MOSFET的硬切换导致泄漏电感能量的耗散。当与低输出电压变换器一起工作时,泄漏能量会非常高(因为匝数比高)。因此,在许多中高功率电源应用中,使用由NCP1560驱动的有源箝位正激拓扑结构具有很大的实际意义。 图2给出了有源箝位变换器的原理图。从图中可以看出,它要求在传统的正激变换器上增加一个有源开关(M4)和一个电容(Cclamp),同时去除了复位绕组和二极管。下文中将对这种拓扑结构进行详细说明。

图2 有源箝位变换器

三、有源箝位变换器

如图2所示,有源箝位拓扑结构是正激变换器的延伸。但是,增加了开关M4、电容Cclamp和相应的控制电路(如NCP1560 IC),这样使电路又具有了诸多新的优势。为了理解这些优势,现在详细介绍一下变换器是如何工作的。变换器的主要工作原理与正激变换器相似,也就是说,当开关M1打开时,功率从输入向输出传输。在M1关闭时,输出电感向输出提供能量,其功率转换方程为

Vout=Vin×D/N (1)

其中:D为占空比,N为变压器匝数比。有源箝位变换器在工作中的主要特点是:当开关M1关闭时,开关M4打开(经过一段可调的延迟后),并且在M1的整个关闭阶段中保持打开。在稳态中,电容Cclamp上的电压 (Vcl) Vin×D=(Vcl-Vin)×(1-D) (2)

如方程(2)所示,Vcl 电压提供了变压器绕组的复位,且不需要复位绕组。由于不同于传统正激变换器的复位电压即为输入电压(假设初级和复位绕组之间的比是1:1),在这种情况下,复位电压和复位间隔都与工作条件相匹配。换句话说,在主开关M1的整个关闭阶段都可以获得复位电压。当输入电压Vin低而占空比D高时,复位电压趋向于高,而在输入电压Vin高时,情况正好相反。因此,当Vin改变时,Vcl 电压(即Vin+复位电压)变化不会太大。从图2中也可以发现,当 M1关闭时,箝位电路(M4和Cclamp)会将M1上的电压钳制为Vcl。因此,M1上的电压在线路电压变化中保持相对稳定。这与正激变换器正好相反, 在正激变换器中M1上的电压等于2Vin。

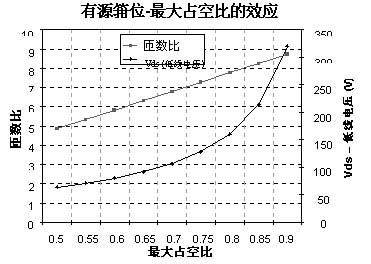

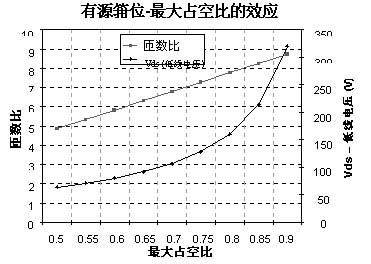

此外,在正激变换器的情况下,最大占空比Dmax不再限于50%。理论上,对于任何非100%占空比,箝位电压均可以调整以提供足够的复位电压。图3给出了最大占空比和匝数比选择,从图中可以看出,高占空比和箝位电压之间有清楚的权衡。高占空比使匝数比(N)可以更高,从而导致较小的初级电流和较低的次级电压。然而,当占空比太高时,Vcl(和M1上的电压)也会变高。对于每种引用,Dmax和匝数比的选择由系统要求决定。在某些情况下,可能需要较高的初级电压,以便减小输出整流器上的电压额定值,而在其他一些情况下,限制初级电压则可能更为重要。

有源箝位电路给系统带来了一些新的优点。

在许多大电流系统中,次级中需要同步整流(用MOSFET代替肖特基或其他整流器)。有了有源箝位电路后,同步整流器开关(M2和M3)的驱动信号可以直接来自次级绕组, 如图4所示。因为同步整流器是自驱动的,驱动次级开关M2和M3不产生任何功率损失。在传统的正激变换器中,因为在部分开关周期中绕组上的电压为零,所以M2的驱动必须单独产生。

增加了有源箝位电路也使得变压器中的磁化电流可以在两个方向上流动。这样,变压器核心得到了更好的利用(第一和第三象限是相等旋转的)。这使得在频率和总通量摆幅相同的情况下,核心损失较低。这种特性使有源箝位电路与双端拓扑结构(如桥式和推拉结构)相似,但依然使用一个电源开关。

最后,有源箝位电路最重要的优点之一是能够使用泄漏电感能量,并能够实现初级开关软打开。通过调整关闭一个初级开关(M1或M4)和打开另一个开关(M4或M1)之间的定时,漏级电压可以在开关打开之前谐振到低值。这样不仅减少了打开损耗,还减少了电路中的振铃和EMI。

一、分布式电源系统的演变和发展趋势

传统的功率转换系统是集中式电源系统,其中,单个电源从输入交流线路向所有需要的输出提供功率转换。随着电源电平的上升和负载电压的下降,提供接近于负载的功率转换非常重要,以便满足稳压要求并减小配电损耗。分布式电源系统由此产生并占据了主导地位,典型的应用例子是计算机电源。在计算机电源中,由非常接近处理器的稳压模块(VRM)提供最终转换。当然,DPS中常见的架构是48 V分布式电源。表1总结了集中式和分布式电源系统的差异。

48V架构继续成为电信市场的主导,并且已经适用于许多网络和高端计算应用中。图1给出了48V分布式电源的架构,在系统前端包括具有功率因数修正(PFC)的隔离式AC-DC变换,以满足减少谐波的要求。乍看之下,在AC-DC变换中加入PFC前端增加了系统的成本、复杂性和潜在效率损失。但是,通过提供预稳压和减小输入端峰值电流,PFC电路实际上有助于优化系统性能。在功率较低(< 250 W)的情况下,系统的成本和性能可以通过使用安森美半导体的NCP1651中独有的单级方法加以优化 。

板上电源架构包括从48V母线进行的隔离DC-DC转换。尽管48V母线应该已经妥善稳压(±5%),电信系统也要求通过电池备份进行工作,结果导致板上DC-DC变换器的输入电压规格更宽(一般为36??72V)。处理这么宽的电压范围对DC-DC 变换器提出了独特的挑战。此外,电压较低(<3.3V)、电流较大(>30A)的输出也使实现高效的功率转换变得更加困难。虽然设计这些变换器是可行的,但是挑战并不仅仅来自于电路设计,还必须特别关注EMI、散热和封装问题,以获得最优的性能。硅技术和无源元件的进步以及封装和电源拓扑结构方面的创新,使DC-DC 变换器的功率密度在近年来急剧增加。

图1 48V分布式架构

在过去几年中,分布式电源系统开始根据不同的应用而的采用了不同的形式和形状。对于不限制使用电池备份选项的应用(如网络和一些电信局端的应用)而言,12V和24V母线系统已被广泛采用。使用更低的母线电压增加了母线电流,功率较低的系统是可以接受的。有了分布式电源系统,板上DC-DC转换无需隔离,而且简化了实现方法。另一方面,由于输出电压接近1V,从 48V到1V的转换并不是非常有效和经济,许多系统现在都包含中间电源架构。

二、DC-DC变换器的设计考虑

无论分布式电源系统中的DC-DC变换器是否产生最终逻辑电压(如3.3V 或 2.5V)或上文提及的中间母线电压,这种类型的功率变换器均需要进行特殊的设计考虑。这些变换器倾向于具有特殊的元件高度限制、隔离要求、效率要求和尺寸限制,这些都要求在变换器设计的方方面面都采用创新的方法。

设计这类变换器的首要考虑事项应该是选择拓扑结构。由于传统的正激或反激拓扑结构成本较低,设计中可以考虑加以采用,但是它们在功率传输能力上受到限制,而且硬切换也影响了效率。由于转换效率取决于最优的变压器核心使用率,这些拓扑结构只在一个方向激发变压器核心,从而限制了功率通过率。另一方面,真正的双端拓扑结构(如半桥和推拉式拓扑结构)允许更小的输出电感和完全的变压器利用率。尽管这两种拓扑结构需要两个开关,但在高功率变换器中,通常还是采用这些拓扑结构。半桥促使高端驱动的要求,而推拉则在开关上施加双倍的最大输入电压。

在上述所有方法中,MOSFET的硬切换导致泄漏电感能量的耗散。当与低输出电压变换器一起工作时,泄漏能量会非常高(因为匝数比高)。因此,在许多中高功率电源应用中,使用由NCP1560驱动的有源箝位正激拓扑结构具有很大的实际意义。 图2给出了有源箝位变换器的原理图。从图中可以看出,它要求在传统的正激变换器上增加一个有源开关(M4)和一个电容(Cclamp),同时去除了复位绕组和二极管。下文中将对这种拓扑结构进行详细说明。

图2 有源箝位变换器

三、有源箝位变换器

如图2所示,有源箝位拓扑结构是正激变换器的延伸。但是,增加了开关M4、电容Cclamp和相应的控制电路(如NCP1560 IC),这样使电路又具有了诸多新的优势。为了理解这些优势,现在详细介绍一下变换器是如何工作的。变换器的主要工作原理与正激变换器相似,也就是说,当开关M1打开时,功率从输入向输出传输。在M1关闭时,输出电感向输出提供能量,其功率转换方程为

Vout=Vin×D/N (1)

其中:D为占空比,N为变压器匝数比。有源箝位变换器在工作中的主要特点是:当开关M1关闭时,开关M4打开(经过一段可调的延迟后),并且在M1的整个关闭阶段中保持打开。在稳态中,电容Cclamp上的电压 (Vcl) Vin×D=(Vcl-Vin)×(1-D) (2)

如方程(2)所示,Vcl 电压提供了变压器绕组的复位,且不需要复位绕组。由于不同于传统正激变换器的复位电压即为输入电压(假设初级和复位绕组之间的比是1:1),在这种情况下,复位电压和复位间隔都与工作条件相匹配。换句话说,在主开关M1的整个关闭阶段都可以获得复位电压。当输入电压Vin低而占空比D高时,复位电压趋向于高,而在输入电压Vin高时,情况正好相反。因此,当Vin改变时,Vcl 电压(即Vin+复位电压)变化不会太大。从图2中也可以发现,当 M1关闭时,箝位电路(M4和Cclamp)会将M1上的电压钳制为Vcl。因此,M1上的电压在线路电压变化中保持相对稳定。这与正激变换器正好相反, 在正激变换器中M1上的电压等于2Vin。

此外,在正激变换器的情况下,最大占空比Dmax不再限于50%。理论上,对于任何非100%占空比,箝位电压均可以调整以提供足够的复位电压。图3给出了最大占空比和匝数比选择,从图中可以看出,高占空比和箝位电压之间有清楚的权衡。高占空比使匝数比(N)可以更高,从而导致较小的初级电流和较低的次级电压。然而,当占空比太高时,Vcl(和M1上的电压)也会变高。对于每种引用,Dmax和匝数比的选择由系统要求决定。在某些情况下,可能需要较高的初级电压,以便减小输出整流器上的电压额定值,而在其他一些情况下,限制初级电压则可能更为重要。

有源箝位电路给系统带来了一些新的优点。

在许多大电流系统中,次级中需要同步整流(用MOSFET代替肖特基或其他整流器)。有了有源箝位电路后,同步整流器开关(M2和M3)的驱动信号可以直接来自次级绕组, 如图4所示。因为同步整流器是自驱动的,驱动次级开关M2和M3不产生任何功率损失。在传统的正激变换器中,因为在部分开关周期中绕组上的电压为零,所以M2的驱动必须单独产生。

增加了有源箝位电路也使得变压器中的磁化电流可以在两个方向上流动。这样,变压器核心得到了更好的利用(第一和第三象限是相等旋转的)。这使得在频率和总通量摆幅相同的情况下,核心损失较低。这种特性使有源箝位电路与双端拓扑结构(如桥式和推拉结构)相似,但依然使用一个电源开关。

最后,有源箝位电路最重要的优点之一是能够使用泄漏电感能量,并能够实现初级开关软打开。通过调整关闭一个初级开关(M1或M4)和打开另一个开关(M4或M1)之间的定时,漏级电压可以在开关打开之前谐振到低值。这样不仅减少了打开损耗,还减少了电路中的振铃和EMI。

电压 电流 电路 半导体 变压器 电感 MOSFET 电容 二极管 PWM 电阻 相关文章:

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)