DC-DC有源箝位正激拓扑技术

时间:11-14

来源:互联网

点击:

四、功率级的设计考虑

为优化有源箝位电路的设计,功率和控制级的元件选择非常重要。对于功率级而言,应谨慎地选择和设计变压器、初级开关、箝位电容和次级开关。

如前一节所示,功率级的设计从选择变压器匝数比和最大占空比开始。在大电流 DC-DC变换器中,应该尽力减小变压器次级匝数(理想情况为1)。这样不但能防止铜损耗,而且也使变压器便于构造。次级匝数为1时,初级匝数等于匝数比N,注意, 匝数必须是整数。如果开始计算时未假设一个整数N,则要求重新计算Dmax和Vds电压,而N等于初始选择以下最大的整数。由于有源箝位变换器利用变压器磁化和泄漏能量来实现软开关,因此允许核心中有间隔,并且有意识的减少磁化电感是有意义的。

电源开关根据最大电压额定值和电流要求进行选择。如前文中所述,M1和M4上的峰值电压相等。除了稳态电压以外,Vds具有低频纹波,由变压器磁化电流和箝位电容Cclamp的值确定。M1中的峰值电流等于输出电流除以匝数比,其RMS值为Ipk×D0.5。M4中的电流是M1关闭阶段中的磁化电流,通常要小得多。因此,M4 Rds-on可以比M1 Rds-on高得多。如图4所示,M4 是一个p-沟道MOSFET,如果它连接到Vin而不是连接到地,也可以选择n-沟道。但是,n-沟道M4要求浮动驱动信号。

图5 NEP1560框图

箝位电容值也涉及到保持Vds低纹波以及更好地瞬态响应线路电压变化之间的权衡。低Cclamp值增加纹波,但是在输入电压改变时,允许复位电压更快达到稳态。建议Cclamp的选择使Vds上得到大约10%的纹波。 任何更高的电容值会导致变压器瞬态饱和。

通常选择次级开关以使导通损耗最小,而且应该选择最低可用的Rds-on值。这些开关上的电压额定值通常必须足够低(M3上的Vin/N以及M2上的Vreset/N),以便使用沟道或等效的技术MOSFETs。

五、控制的设计考虑

如上所述,与传统的正激变换器相比,使用有源箝位的正激变换器拥有明显的优势。但是,这种变换器要求为有源箝位开关提供额外的控制信号和紧凑的最大占空比控制。针对有源箝位拓扑结构的独特要求,安森美半导体开发了NCP1560电压模式控制器。此控制器包含了其他传统PWM控制器中所没有的广泛特性,实现了高度集成化。这使NCP1560所需要配置的外接元件达到最少。实际上,它的大多数特性通过单个电阻或电容进行设置。

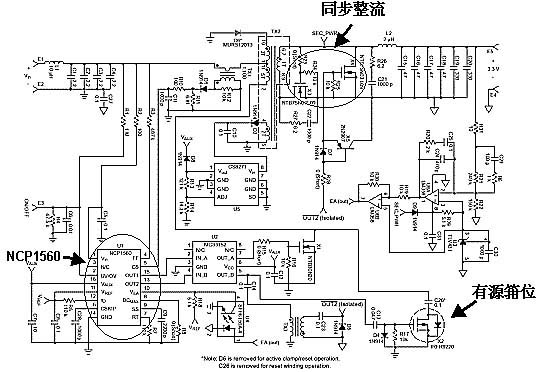

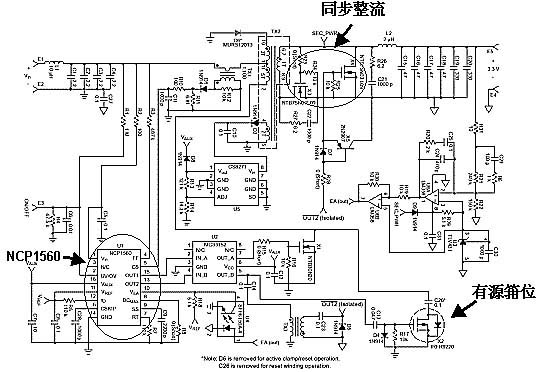

图6 变换器原理图

NCP1560 提供2个互补的具有可调重叠延迟的控制输出。图5为NCP1560的原理框图,描述了此控制器的全部功能。输出1可以用于控制主开关,输出2可以用于控制有源箝位开关或同步整流拓扑结构。 输出设计用于互补用途。输出2 不反相,可以用于控制使用p-沟道MOSFET的有源箝位。NCP1560的特性包括:一个前馈斜升电压发生器、可编程软启动和高压启动稳压器。在各种故障情况下,通过欠压或过压检测器的单条线路提供保护,此检测器具有滞后、可调最大占空比限制和双模式电流限制(包括逐周期和跳周期)的功能。如果检测到严重的过流情况,跳周期特性在CSKIP引脚上电容确定的时间内禁用变换器。

六、电路实现和结果

设计48V 电信系统的变换器验证了NCP1560的灵活性。它提供了100W的功率和3.3V的输出电压。变换器的完整规格列示如下:

1. 输入:32 78V(大于标准电信范围)

2. 输出电压:3.3V(±5%)

3. 输出电流:3 30A

4. 输出电压纹波:最大50mV

5. 效率:满负载时大于85%

6. 开关频率:275kHz

7. 物理尺寸:2.5英寸×3.0英寸×0.4英寸

8. 初-次级隔离:工作时500V

9. 印刷电路板:4层,单面元件布局

为便于比较,设计一个变换器用于使用有源箝位或复位绕组(需拆去一些元件)的工作。完整的演示板电路原理图如图6所示。这种解决方案的全部硅元件除光耦合器和有源箝位开关除外均采用安森美半导体的产品。

图6中着重标出了NCP1560控制器、同步整流和有源箝位电路。同步整流和有源箝位电路均由NCP1560的第二个输出控制。tD 和 VREF引脚之间的单个电阻(R5)设定了100 ns的输出重叠延迟。前馈斜升电压通过在输入电压源和FF引脚之间连接R3而产生。60 %的最大占空比通过DCMAX引脚接地进行设定。电阻R7(110kΩ)设定工作频率为275 kHz。电源变压器(TX2)以外的辅助绕组提供了启动后的功率,以禁用NCP1560内部的启动稳压器。

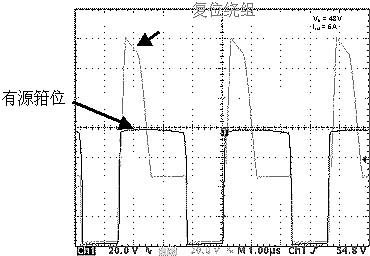

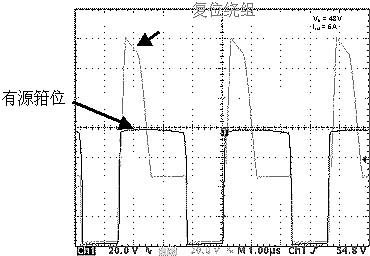

复位绕组和有源箝位配置关闭时的电源开关电压波形如图7所示。曲线a表示复位绕组操作所配置的变换器的电压,曲线b表示使用有源箝位复位的变换器的电压。两个波形在同样的操作条件下捕获。

图7 复位绕组和有源箝位配置关闭时的电源开关电压

从图7中可以看到,使用复位绕组时,48V的输入电压产生了大约140V的峰值电压。相比较而言,使用有源箝位复位的峰值电压大约为78V。请注意,使用复位绕组时,主开关的电压大于输入电压的两倍。这是因为初级和复位绕组匝数比为 5:3(而非5:5),以使操作达到60%的占空比。

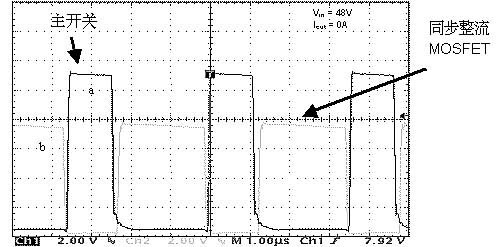

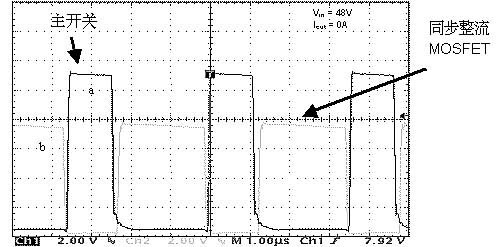

图8 主开关和同步整流MOSFET栅极驱动信号

图8为主开关和同步整流MOSFET栅极驱动信号图,图中,可调的重叠延迟防止主开关和同步整流MOSFET X4同时导通。曲线a表示主开关栅极,曲线b表示同步MOSFET。

变换器效率和负载电流的关系如图9所示。图中分别给出了最小、典型和最大输入电压时的结果。

变换器可以实现90%的最大效率,满负载时的效率超过85%。负载和线路调整在整个操作范围内的测量值小于1%。变换器板如图10所示。

为优化有源箝位电路的设计,功率和控制级的元件选择非常重要。对于功率级而言,应谨慎地选择和设计变压器、初级开关、箝位电容和次级开关。

如前一节所示,功率级的设计从选择变压器匝数比和最大占空比开始。在大电流 DC-DC变换器中,应该尽力减小变压器次级匝数(理想情况为1)。这样不但能防止铜损耗,而且也使变压器便于构造。次级匝数为1时,初级匝数等于匝数比N,注意, 匝数必须是整数。如果开始计算时未假设一个整数N,则要求重新计算Dmax和Vds电压,而N等于初始选择以下最大的整数。由于有源箝位变换器利用变压器磁化和泄漏能量来实现软开关,因此允许核心中有间隔,并且有意识的减少磁化电感是有意义的。

电源开关根据最大电压额定值和电流要求进行选择。如前文中所述,M1和M4上的峰值电压相等。除了稳态电压以外,Vds具有低频纹波,由变压器磁化电流和箝位电容Cclamp的值确定。M1中的峰值电流等于输出电流除以匝数比,其RMS值为Ipk×D0.5。M4中的电流是M1关闭阶段中的磁化电流,通常要小得多。因此,M4 Rds-on可以比M1 Rds-on高得多。如图4所示,M4 是一个p-沟道MOSFET,如果它连接到Vin而不是连接到地,也可以选择n-沟道。但是,n-沟道M4要求浮动驱动信号。

图5 NEP1560框图

箝位电容值也涉及到保持Vds低纹波以及更好地瞬态响应线路电压变化之间的权衡。低Cclamp值增加纹波,但是在输入电压改变时,允许复位电压更快达到稳态。建议Cclamp的选择使Vds上得到大约10%的纹波。 任何更高的电容值会导致变压器瞬态饱和。

通常选择次级开关以使导通损耗最小,而且应该选择最低可用的Rds-on值。这些开关上的电压额定值通常必须足够低(M3上的Vin/N以及M2上的Vreset/N),以便使用沟道或等效的技术MOSFETs。

五、控制的设计考虑

如上所述,与传统的正激变换器相比,使用有源箝位的正激变换器拥有明显的优势。但是,这种变换器要求为有源箝位开关提供额外的控制信号和紧凑的最大占空比控制。针对有源箝位拓扑结构的独特要求,安森美半导体开发了NCP1560电压模式控制器。此控制器包含了其他传统PWM控制器中所没有的广泛特性,实现了高度集成化。这使NCP1560所需要配置的外接元件达到最少。实际上,它的大多数特性通过单个电阻或电容进行设置。

图6 变换器原理图

NCP1560 提供2个互补的具有可调重叠延迟的控制输出。图5为NCP1560的原理框图,描述了此控制器的全部功能。输出1可以用于控制主开关,输出2可以用于控制有源箝位开关或同步整流拓扑结构。 输出设计用于互补用途。输出2 不反相,可以用于控制使用p-沟道MOSFET的有源箝位。NCP1560的特性包括:一个前馈斜升电压发生器、可编程软启动和高压启动稳压器。在各种故障情况下,通过欠压或过压检测器的单条线路提供保护,此检测器具有滞后、可调最大占空比限制和双模式电流限制(包括逐周期和跳周期)的功能。如果检测到严重的过流情况,跳周期特性在CSKIP引脚上电容确定的时间内禁用变换器。

六、电路实现和结果

设计48V 电信系统的变换器验证了NCP1560的灵活性。它提供了100W的功率和3.3V的输出电压。变换器的完整规格列示如下:

1. 输入:32 78V(大于标准电信范围)

2. 输出电压:3.3V(±5%)

3. 输出电流:3 30A

4. 输出电压纹波:最大50mV

5. 效率:满负载时大于85%

6. 开关频率:275kHz

7. 物理尺寸:2.5英寸×3.0英寸×0.4英寸

8. 初-次级隔离:工作时500V

9. 印刷电路板:4层,单面元件布局

为便于比较,设计一个变换器用于使用有源箝位或复位绕组(需拆去一些元件)的工作。完整的演示板电路原理图如图6所示。这种解决方案的全部硅元件除光耦合器和有源箝位开关除外均采用安森美半导体的产品。

图6中着重标出了NCP1560控制器、同步整流和有源箝位电路。同步整流和有源箝位电路均由NCP1560的第二个输出控制。tD 和 VREF引脚之间的单个电阻(R5)设定了100 ns的输出重叠延迟。前馈斜升电压通过在输入电压源和FF引脚之间连接R3而产生。60 %的最大占空比通过DCMAX引脚接地进行设定。电阻R7(110kΩ)设定工作频率为275 kHz。电源变压器(TX2)以外的辅助绕组提供了启动后的功率,以禁用NCP1560内部的启动稳压器。

复位绕组和有源箝位配置关闭时的电源开关电压波形如图7所示。曲线a表示复位绕组操作所配置的变换器的电压,曲线b表示使用有源箝位复位的变换器的电压。两个波形在同样的操作条件下捕获。

图7 复位绕组和有源箝位配置关闭时的电源开关电压

从图7中可以看到,使用复位绕组时,48V的输入电压产生了大约140V的峰值电压。相比较而言,使用有源箝位复位的峰值电压大约为78V。请注意,使用复位绕组时,主开关的电压大于输入电压的两倍。这是因为初级和复位绕组匝数比为 5:3(而非5:5),以使操作达到60%的占空比。

图8 主开关和同步整流MOSFET栅极驱动信号

图8为主开关和同步整流MOSFET栅极驱动信号图,图中,可调的重叠延迟防止主开关和同步整流MOSFET X4同时导通。曲线a表示主开关栅极,曲线b表示同步MOSFET。

变换器效率和负载电流的关系如图9所示。图中分别给出了最小、典型和最大输入电压时的结果。

变换器可以实现90%的最大效率,满负载时的效率超过85%。负载和线路调整在整个操作范围内的测量值小于1%。变换器板如图10所示。

电压 电流 电路 半导体 变压器 电感 MOSFET 电容 二极管 PWM 电阻 相关文章:

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)