基于EPM570的可逆直流调速模块设计

时间:11-14

来源:互联网

点击:

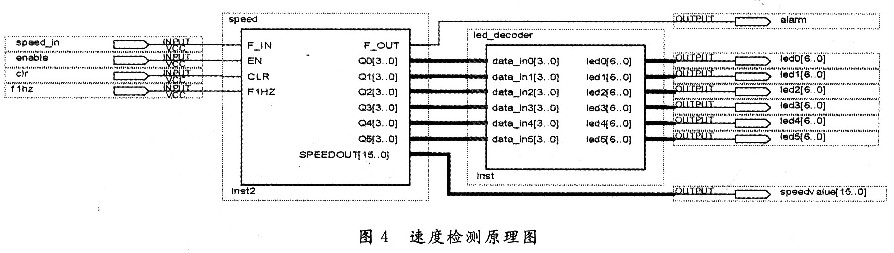

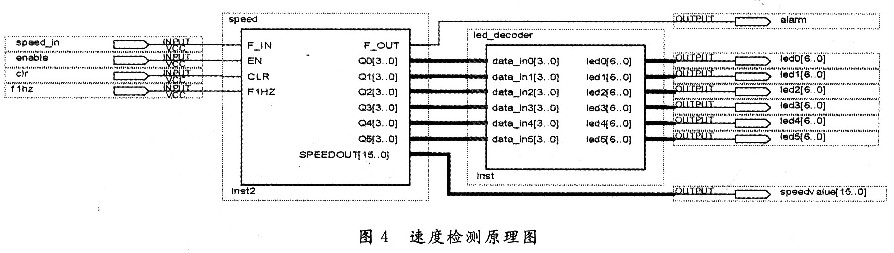

3.2 速度检测

速度检测模块主要包括频率计和译码电路,如图4所示。enable为速度检测使能信号,clr为输出清零信号,speed_in为输入速度脉冲信号,led0~led5为6位数码管输出信号。

3.3 速度控制

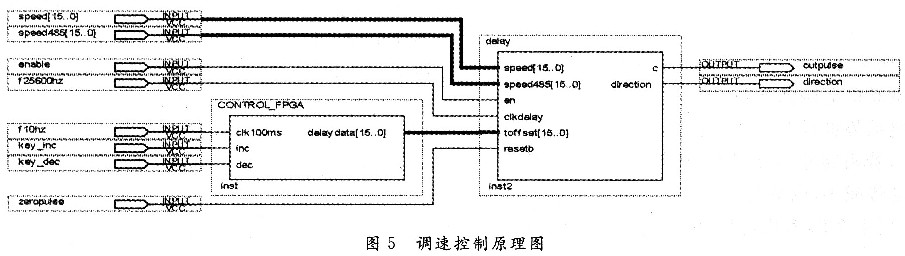

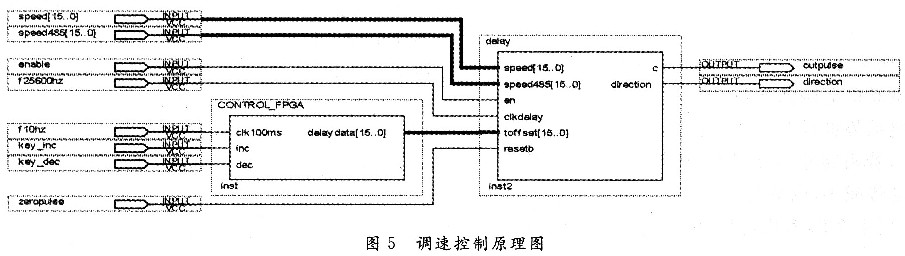

速度控制的原理是根据设定速度与实际速度的偏差用PID算法产生控制量,根据控制量的大小把过零检测脉冲移相后加宽作为输出控制信号,如图5所示。

enable为输入使能控制信号;f25600hz为决定移相单位时间的输入信号;delay_flhz为按键加减的单位时间输入信号;key_inc和key_ dec分别为加速和减速按键的输入信号;zeroin为输入同步过零脉冲信号,频率为100Hz;outpulse为输出的移相脉冲信号;direction为转向信号。

3.4 RS 485通信模块

RS 485总线是一种多点差分数据传输的电气规范,其通信接口允许在简单的一对双绞线上进行多点双向通信,具有噪声抑制能力强,高速数据传输,且电缆比较长及可靠性高的特点。

RS 485子模块主要实现UART功能,并通过notre和de信号控制发送和接收。串行通信固定设为9 600波特、8位数据、无奇偶校验、1位停止位。数据格式:地址码、数据、结束字符,其长度分别为8位、16位、8位。当总线上挂接多个调速模块时,采用广播方法发送消息,地址码可根据实际情况约定。由于RS 485总线是异步半双工的通信总线,一个时刻总线只可能呈现一种状态。因此在空闲状态时,将RS 485总线始终设置为接收状态。

3.5 仿真

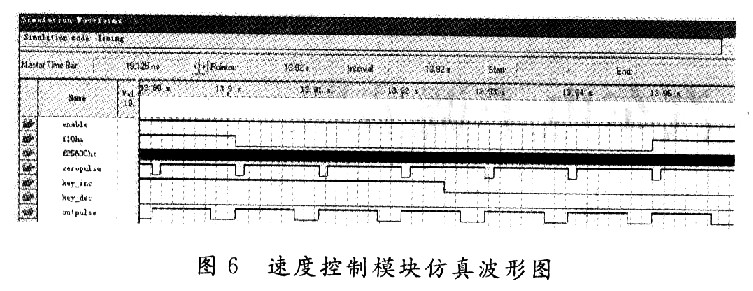

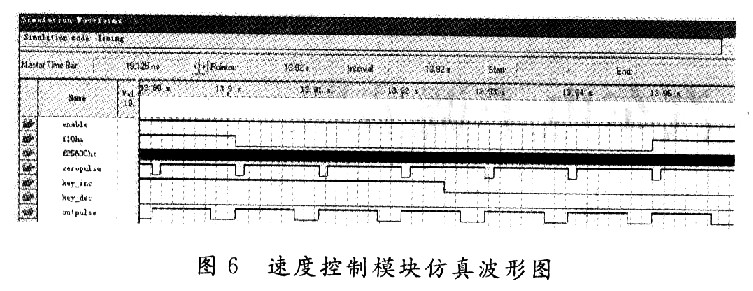

功能仿真又称前仿真,其目的是检查HDL代码所描述的逻辑功能是否和预期的功能一致。全部模块已在QuartusⅡ中仿真通过,图6给出速度控制模块功能仿真波形。仿真时间为30 s,假设期间实际速度为常数,在3.9 s按下加速按键,使key_inc变为高电平,10 s后(13.90 s时刻)加速按键释放变为低电平,据图6的仿真波形图中可知,在13.90 s时刻,输出脉冲下降沿相对于过零脉冲从180°向前移相约70°,表明移相调速功能正常。

4 实际系统运行数据

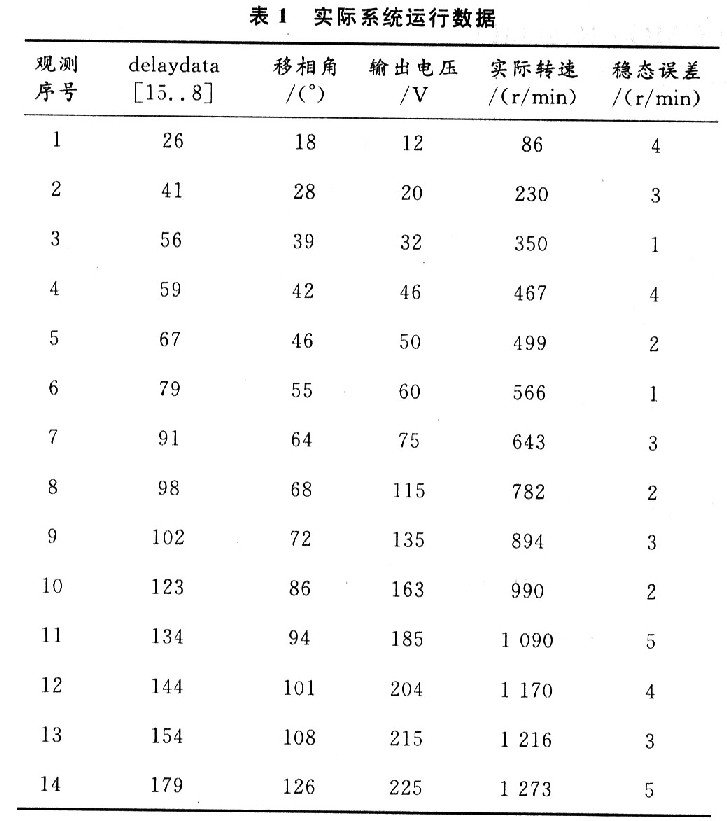

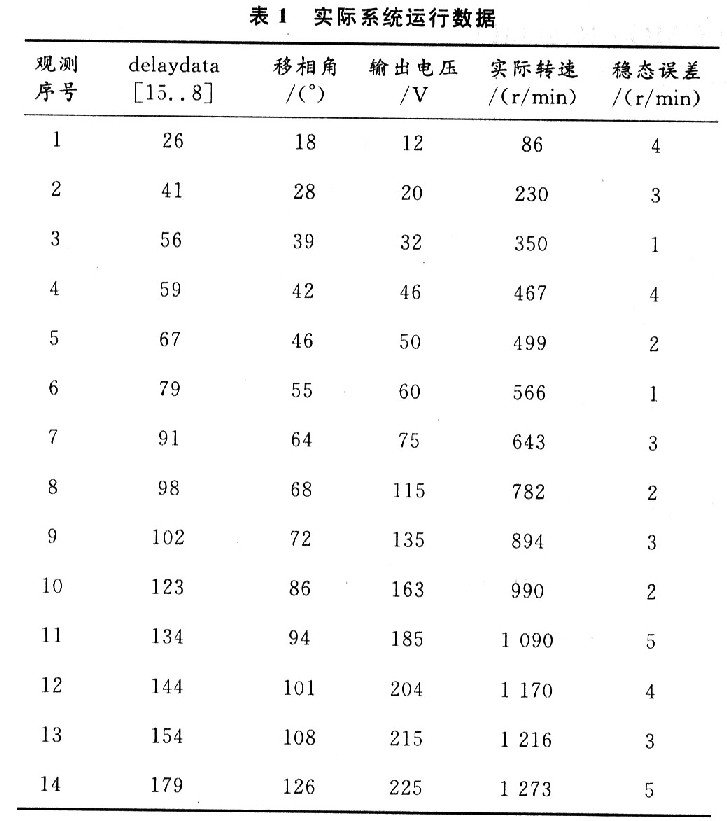

为调试和分析系统运行状况,测得如表1所示系统运行数据。主电动机型号110ZF53,pN=100 W,UN=220 V,IN=0.50 A,1 600 rpm。 delaydata[15..8]是速度控制模块中元件CONTROL FPGA的延时,输出数据高8位。

从表1中数据看出,控制系统可有效、连续地调整电机速度,稳态误差较小,负载转矩的变化使移相角与转速之间呈非线性关系,但移相角与输出电压——对应。

5 结语

该设计具有通用性、经济性、可靠性,是常规直流速度控制的较好解决方案。由于采用CPLD芯片作为控制核心,可方便地进行各种改进。若要进一步提高控制性能,可以增加电流闭环;或稍加改动,可以控制两台直流电机的单向运行;可以实现组成分布式网络控制系统等。

速度检测模块主要包括频率计和译码电路,如图4所示。enable为速度检测使能信号,clr为输出清零信号,speed_in为输入速度脉冲信号,led0~led5为6位数码管输出信号。

3.3 速度控制

速度控制的原理是根据设定速度与实际速度的偏差用PID算法产生控制量,根据控制量的大小把过零检测脉冲移相后加宽作为输出控制信号,如图5所示。

enable为输入使能控制信号;f25600hz为决定移相单位时间的输入信号;delay_flhz为按键加减的单位时间输入信号;key_inc和key_ dec分别为加速和减速按键的输入信号;zeroin为输入同步过零脉冲信号,频率为100Hz;outpulse为输出的移相脉冲信号;direction为转向信号。

3.4 RS 485通信模块

RS 485总线是一种多点差分数据传输的电气规范,其通信接口允许在简单的一对双绞线上进行多点双向通信,具有噪声抑制能力强,高速数据传输,且电缆比较长及可靠性高的特点。

RS 485子模块主要实现UART功能,并通过notre和de信号控制发送和接收。串行通信固定设为9 600波特、8位数据、无奇偶校验、1位停止位。数据格式:地址码、数据、结束字符,其长度分别为8位、16位、8位。当总线上挂接多个调速模块时,采用广播方法发送消息,地址码可根据实际情况约定。由于RS 485总线是异步半双工的通信总线,一个时刻总线只可能呈现一种状态。因此在空闲状态时,将RS 485总线始终设置为接收状态。

3.5 仿真

功能仿真又称前仿真,其目的是检查HDL代码所描述的逻辑功能是否和预期的功能一致。全部模块已在QuartusⅡ中仿真通过,图6给出速度控制模块功能仿真波形。仿真时间为30 s,假设期间实际速度为常数,在3.9 s按下加速按键,使key_inc变为高电平,10 s后(13.90 s时刻)加速按键释放变为低电平,据图6的仿真波形图中可知,在13.90 s时刻,输出脉冲下降沿相对于过零脉冲从180°向前移相约70°,表明移相调速功能正常。

4 实际系统运行数据

为调试和分析系统运行状况,测得如表1所示系统运行数据。主电动机型号110ZF53,pN=100 W,UN=220 V,IN=0.50 A,1 600 rpm。 delaydata[15..8]是速度控制模块中元件CONTROL FPGA的延时,输出数据高8位。

从表1中数据看出,控制系统可有效、连续地调整电机速度,稳态误差较小,负载转矩的变化使移相角与转速之间呈非线性关系,但移相角与输出电压——对应。

5 结语

该设计具有通用性、经济性、可靠性,是常规直流速度控制的较好解决方案。由于采用CPLD芯片作为控制核心,可方便地进行各种改进。若要进一步提高控制性能,可以增加电流闭环;或稍加改动,可以控制两台直流电机的单向运行;可以实现组成分布式网络控制系统等。

可控硅 电路 单片机 电动机 编码器 电压 LED Altera FPGA Quartus 电感 电阻 电流 总线 仿真 CPLD 相关文章:

- 关键电源及LED照明应用的最新高能效规范要求、设计挑战及解决方案(12-07)

- 对双向可控硅内部电路的探讨(05-18)

- 电源高位跟踪系统的设计与实现(07-17)

- 基于TCA785移相触发器的中频感应加热电源(07-23)

- 基于AT89C52的励磁调节器的设计与实现(07-23)

- 浅谈功率器件在静止变频技术中的应用(08-03)