新型大电流CPU供电的设计挑战

时间:09-11

来源:互联网

点击:

在过去五年里,Intel和AMD的CPU性能有了显著提高。CPU性能的提高要求为其供电的电压调节器更加精确和复杂。

电源设计人员所面临的最大挑战是如何满足更大的功率、更小的电压容限以及更快的瞬态响应,并降低电源的总成本。本文简要探讨了脉宽调制(PWM)的发展历程、多相工作模式和电流均衡,并提供了一些有助于设计人员应对大功率CPU供电各种挑战的最新技术。

性能要求不断提高,成本控制更加严格

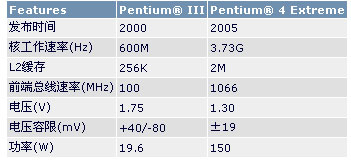

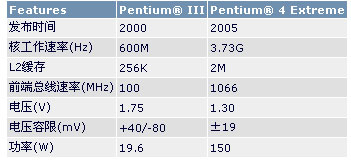

下表展示了CPU性能在过去5年间的发展。注意:在功率大幅增加的同时,电压尤其是电压容限显著降低。

功率: 电压调节器的一个参数为“相”数,或其提供的通道数。依据可用空间和散热等因素,每相可提供25W至40W的功率。对于Pentium 3而言,单相电压调节器就可满足要求,而最新一代CPU则需要采用3相或4相电压调节器。

电流均衡: 设计多相电源所面临的挑战之一便是合理分配各相电流(功率)。如果某相电流严重地不成比例,会加大元器件的负荷并缩短使用寿命。实际上,所有多相电压调节器都包含了能够主动均衡各相电流的电路。

精度: 为使CPU工作在较高的时钟频率,要求其电源电压具有极高精度。并且必须在静态和动态负载下都能保持高精度指标。通过采用精密的片上基准,以及最大程度地降低失调电压和偏置电流,可获得良好的静态精度。而动态电压精度则与电压调节器的控制环路带宽以及调节器输出端的大容量电容有关。由于调节器不能立刻响应CPU的电流突变,因此设计电路需要大容量的电容。调节器控制环路带宽越高,响应CPU动态需求的速度就越高,并可快速补充大容量输出电容的暂态电流。

对CPU电压调节器的要求并非不计成本,裸片尺寸和引脚数都与调节器提供的相数成比例。高精度电压基准要求采用成熟、完善的设计方案和校准技术。用于电压和电流检测、电压调节以及有源均流的放大器必须保证高速工作,并具有较低的失调误差和偏置电流,而且相对于工艺和温度保持稳定。

大功率CPU调节器设计所面临的严峻挑战也许就是成本问题,在过去5年当中,CPU核电压调节器的每相价格降低了4倍甚至更多。

电源控制的基本要素

所有多相电压调节器都采用这种或那种形式的PWM结构。大多数电压调节器工作在固定频率,由时钟信号触发高边MOSFET (图1中的QHI)导通,使输入电源开始对电感充电。

图1. 简化的单相降压调节器

当控制环路确定应该终止“导通脉冲”时,高边MOSFET断开,低边MOSFET (QLO)导通,电感对负载放电。由于脉冲前沿(高边开通)时间固定(由内部时钟设置),而脉冲后沿(高边断开)则根据控制环路和实时状态变化,因此这种PWM控制类型称为后沿调制。高边MOSFET导通时间相对于时钟周期的百分比称为占空比(D),该占空比在稳定状态下等于VOUT/VIN。

在电压控制模式下(参见图2),输出电压(或其比例)与固定的内部基准电压进行比较。产生的误差信号再与内部固定的锯齿波(或斜坡)信号进行比较。该斜坡信号与时钟脉冲同时触发,而且只要斜坡信号低于误差电压,PWM比较器的输出就一直保持为高电平。当斜坡信号高于误差电压时,PWM比较器的输出变为低电平并终止导通。电压环路通过适当的调节控制电压(VC)以及由此产生的占空比,使输出电压(图3)保持恒定。

图2. 简化的电压模式降压调节器

图3. 电压模式波形图

峰值电流模式(参见图4)将电流检测引入控制环路,用电感电流斜坡取代了电压模式下的斜坡信号。与电压模式类似,按照固定频率开通高边MOSFET,使电感电流线性上升。当峰值电感电流等于误差电压时,导通脉冲终止,高边MOSFET断开。这种方式需要一个电压环路和一个电流环路,电压环路通过适当调整由电流环路测量的电感峰值电流,来保持输出电压的稳定。

图4. 简化的峰值电流模式降压调节器

需要考虑及权衡的事项

正如人们所料,每种方法都存在其优缺点。以下各节将对电源设计人员必须考虑的因素加以说明。

噪声抑制

电压模式具有良好的噪声抑制能力,这是因为在设计控制IC时,可以使斜坡信号的大小与实际信号一样大。输出电压是返回到控制器的唯一敏感信号,因此,电压模式相对容易布局。

除了输出电压外,峰值电流模式还需要返回一个电流检测信号,可以由负载电流通路的取样电阻提供(参见电流均衡)。若要最大限度地降低I2R损耗,检流电阻的阻值要尽可能小一些。因此,取样信号往往比电压模式的内部斜坡信号小一个数量级。值得注意的是,应确保信号不受外部噪声源的干扰。在实际应用中,峰值电流模式非常通用,而且,采用标准的的电路板布局原则,其布局布线并不困难。

电源设计人员所面临的最大挑战是如何满足更大的功率、更小的电压容限以及更快的瞬态响应,并降低电源的总成本。本文简要探讨了脉宽调制(PWM)的发展历程、多相工作模式和电流均衡,并提供了一些有助于设计人员应对大功率CPU供电各种挑战的最新技术。

性能要求不断提高,成本控制更加严格

下表展示了CPU性能在过去5年间的发展。注意:在功率大幅增加的同时,电压尤其是电压容限显著降低。

功率: 电压调节器的一个参数为“相”数,或其提供的通道数。依据可用空间和散热等因素,每相可提供25W至40W的功率。对于Pentium 3而言,单相电压调节器就可满足要求,而最新一代CPU则需要采用3相或4相电压调节器。

电流均衡: 设计多相电源所面临的挑战之一便是合理分配各相电流(功率)。如果某相电流严重地不成比例,会加大元器件的负荷并缩短使用寿命。实际上,所有多相电压调节器都包含了能够主动均衡各相电流的电路。

精度: 为使CPU工作在较高的时钟频率,要求其电源电压具有极高精度。并且必须在静态和动态负载下都能保持高精度指标。通过采用精密的片上基准,以及最大程度地降低失调电压和偏置电流,可获得良好的静态精度。而动态电压精度则与电压调节器的控制环路带宽以及调节器输出端的大容量电容有关。由于调节器不能立刻响应CPU的电流突变,因此设计电路需要大容量的电容。调节器控制环路带宽越高,响应CPU动态需求的速度就越高,并可快速补充大容量输出电容的暂态电流。

对CPU电压调节器的要求并非不计成本,裸片尺寸和引脚数都与调节器提供的相数成比例。高精度电压基准要求采用成熟、完善的设计方案和校准技术。用于电压和电流检测、电压调节以及有源均流的放大器必须保证高速工作,并具有较低的失调误差和偏置电流,而且相对于工艺和温度保持稳定。

大功率CPU调节器设计所面临的严峻挑战也许就是成本问题,在过去5年当中,CPU核电压调节器的每相价格降低了4倍甚至更多。

电源控制的基本要素

所有多相电压调节器都采用这种或那种形式的PWM结构。大多数电压调节器工作在固定频率,由时钟信号触发高边MOSFET (图1中的QHI)导通,使输入电源开始对电感充电。

图1. 简化的单相降压调节器

当控制环路确定应该终止“导通脉冲”时,高边MOSFET断开,低边MOSFET (QLO)导通,电感对负载放电。由于脉冲前沿(高边开通)时间固定(由内部时钟设置),而脉冲后沿(高边断开)则根据控制环路和实时状态变化,因此这种PWM控制类型称为后沿调制。高边MOSFET导通时间相对于时钟周期的百分比称为占空比(D),该占空比在稳定状态下等于VOUT/VIN。

在电压控制模式下(参见图2),输出电压(或其比例)与固定的内部基准电压进行比较。产生的误差信号再与内部固定的锯齿波(或斜坡)信号进行比较。该斜坡信号与时钟脉冲同时触发,而且只要斜坡信号低于误差电压,PWM比较器的输出就一直保持为高电平。当斜坡信号高于误差电压时,PWM比较器的输出变为低电平并终止导通。电压环路通过适当的调节控制电压(VC)以及由此产生的占空比,使输出电压(图3)保持恒定。

图2. 简化的电压模式降压调节器

图3. 电压模式波形图

峰值电流模式(参见图4)将电流检测引入控制环路,用电感电流斜坡取代了电压模式下的斜坡信号。与电压模式类似,按照固定频率开通高边MOSFET,使电感电流线性上升。当峰值电感电流等于误差电压时,导通脉冲终止,高边MOSFET断开。这种方式需要一个电压环路和一个电流环路,电压环路通过适当调整由电流环路测量的电感峰值电流,来保持输出电压的稳定。

图4. 简化的峰值电流模式降压调节器

需要考虑及权衡的事项

正如人们所料,每种方法都存在其优缺点。以下各节将对电源设计人员必须考虑的因素加以说明。

噪声抑制

电压模式具有良好的噪声抑制能力,这是因为在设计控制IC时,可以使斜坡信号的大小与实际信号一样大。输出电压是返回到控制器的唯一敏感信号,因此,电压模式相对容易布局。

除了输出电压外,峰值电流模式还需要返回一个电流检测信号,可以由负载电流通路的取样电阻提供(参见电流均衡)。若要最大限度地降低I2R损耗,检流电阻的阻值要尽可能小一些。因此,取样信号往往比电压模式的内部斜坡信号小一个数量级。值得注意的是,应确保信号不受外部噪声源的干扰。在实际应用中,峰值电流模式非常通用,而且,采用标准的的电路板布局原则,其布局布线并不困难。

电压 PWM 电流 电路 电容 放大器 MOSFET 电感 比较器 电阻 电容器 Maxim 示波器 DAC 滤波器 相关文章:

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)