微带线和带状线设计

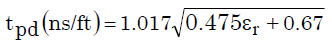

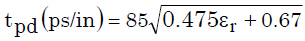

根据等式5,也可以计算微带线的传播延迟。这是微带信号走线的单向通过时间。有趣的是,对于给定的几何模型,延迟常数(单位:ns/ft)仅为介电常数而非走线维度的函数(见参考文献6)。请注意,这可以带来极大的便利。意味着,当给定PCB基板(并给定εr)时,各种阻抗线路的传播延迟常数是固定不变的。

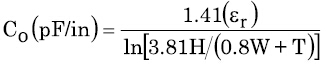

等式5

等式5

该延迟常数也可以ps/in为单位,这样更适用于小型PCB。即:

等式6

等式6

因此,举例来说,对于PCB介电常数4.0,不难发现微带线的延迟常数约为1.63 ns/ft,合136 ps/in。这两条额外的准则对于设计PCB走线中信号的时序具有参考意义。

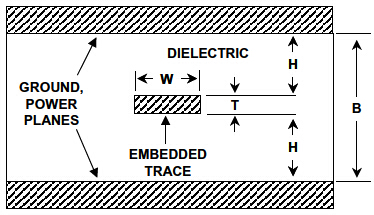

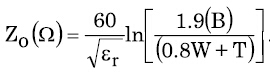

对称带状线PCB传输线路

从多种角度来看,多层PCB是一种更好的PCB设计方法。在这种模式下,信号走线嵌入电源层与接地层之间,如图3中的横截面视图所示。低阻抗交流接地层和嵌入的信号走线形成一条对称带状线传输线路。

从图中可以看出,高频信号走线的电流回路直接位于接地层/电源层上的信号走线的上方和下方。因此,高频信号被完全限制在PCB板内部,结果使放射降至最低,为输入杂散信号提供了天然的屏障。

Figure 3: A Symmetric Stripline Transmission Line With Defined Impedance is Formed by a PCB Trace of Appropriate Geometry Embedded Between Equally Spaced Ground and/or Power Planes

该设计的特性阻抗同样取决于几何图形以及PCB介电质的εr。该带状传输线路的ZO可表示为:

等式7

等式7

这里的所有维度同样以mil为单位,B为两个层的间距。在这种对称几何图形中,需要注意的是,B同样等于2H + T。参考文献2指出,参考文献1中的这个等式的精度通常在6%左右。

适用于εr= 4.0的对称带状线的另一条便利准则是,使B成为W的倍数,范围为2至2.2。结果将得到约50Ω的带状线阻抗。当然,这条法则是以另一近似法为基础的,忽略了T。尽管如此,该法则对于粗略估算还是很有用的。

对称带状线同样有一个特性电容,其计算单位为pF/in,如等式8所示。

等式8

等式8

对称带状线的传播延迟如等式9所示。

等式9

等式9

或者以ps为单位:

等式10

等式10

当PCB介电常数为4.0时,可以发现,对称带状线的延迟常数几乎正好为2 ns/ft,合170 ps/in。

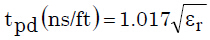

走线嵌入法的利弊

根据上述讨论,在设计阻抗既定的PCB走线时,既可以置于一个表层之上,也可嵌入两层之间。当然,在这些阻抗因素之外,还有许多其他考虑因素。

嵌入式信号确实存在一个明显的大问题——隐藏电路走线的调试非常困难,甚至无法做到。图4总结了嵌入式信号走线的利弊。

图4:多层PCB设计中嵌入与不嵌入信号走线的利弊

设计多层PCB时也可能不使用嵌入式走线,如最左边的横截面视图所示。可以将这种嵌入式设计看作一种双重双层PCB设计(共有四层铜)。顶部的走线与电源层构成微带,底部的走线则与接地层构成微带。在本例中,两个外层的信号走线可以方便地供测量和故障排查使用。但这种设计并未利用各层的屏蔽作用。

这种非嵌入式设计的辐射量较大,更容易受到外部信号的影响,而右侧的嵌入式设计采用了嵌入法,则很好地利用了各层的优势。就如诸多其他工程设计一样,PCB设计中到底采用嵌入法还是非嵌入法是折衷的结果。这里的折衷则体现在减少辐射与方便测试之间。

参考文献:

1. Standard IPC-2141A, "Controlled Impedance Circuit Boards and High Speed Logic Design," 2004, Institute for Interconnection and Packaging Electronic Circuits, 3000 Lakeside Drive, 309 S, Bannockburn, IL 60015, 847-615-7100.2. Eric Bogatin, BTS015, PCB Impedance Design: Beyond the IPC Recommendations, BeTheSignal.com.

3. Eric Bogatin, Signal Integrity – Simplified, Prentice Hall PTR, 2003, ISBN-10: 0130669466, ISBN-13: 978-0130669469.

4. Andrew Burkhardt, Christopher Gregg, Alan Staniforth, "Calculation of PCB Track Impedance," Technical Paper S-19-5, presented at the IPC Printed Circuits Expo '99 Conference, March 14–18, 1999.

5. Brian C. Wadell, Transmission Line Design Handbook, Artech House, Norwood, MA, 1991, ISBN: 0- 89006-436-9.

6. William R. Blood, Jr., MECL System Design Handbook (HB205/D, Rev. 1A May 1988), ON Semiconductor, August, 2000.

7. Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as Linear Circuit Design Handbook, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

8. Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

9. Walter G. Jung, Op Amp Applications, Analog Devices, 2002, ISBN 0-916550-26-5, Chapter 7. Also available as Op Amp Applications Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 7.

- 如何避免放大器电路设计中的常见问题(07-30)

- 通信链路与电子护栏:有关RS-485EMC稳定性的演示(04-16)