基于嵌入式技术的MultiBus-CPU模块设计

时间:12-27

来源:互联网

点击:

MultiBus-CPU模块是基于AT91RM9200微控制器的智能化多总线测控模块。该CPU模块主要实现对下位机的控制,并建立基于Modbus-RTU总线协议的总线通信体系结构,让系统设备可以无缝接入基于Modbus-RTU模式的总线系统,可靠、实时、准确地实现工业现场数据采集、信号输出等功能;同时,提供标准视频接口用于显示16位色图像,提供标准音频输入输出接口用于实现录放音功能。该模块作为嵌入式开发环境的核心,可实现人机界面的交互操作和显示、海量数据的存储、多串口、多USB口、音频信号输入输出、以太网口等接口;运行Linux操作系统,可以快速搭建面向应用的嵌入式应用系统。

1 MultIBus-CPU模块软件设计方案

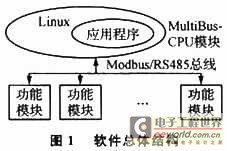

为了满足实际应用对实时性的要求,MultiBus-CPU模块软件采用了Linux 2.6.21操作系统。其中,Linux 2.6的内核任务可以被抢占,这一特性使得Linux 2.6内核适用于实时系统和嵌入式系统中。驱动程序在Linux环境下进行开发,应用层采用标准的通信协议——Modbus协议,控制设备可以连成工业网络进行集中监控。通过一致的Modbus接口,MultiBus-CPU模块与扩展下位机均可作为对等设备在工业网络中进行对话,使得各个设备无缝接人到工业控制网络中。MNtiBus-CPU模块支持现阶段工业测控系统中最常用的以太网(UDP)通信及RS485通信协议。因此,本模块在与其他功能模块进行通信时,采用Modbus-RTU数据通信方式,利用以太网(UDP)/RS485总线进行数据的发送与接收,实现对各功能模块的集中监控。软件总体结构如图1所示。

2 MultiBus-CPU模块硬件设计方案

硬件设计原理图如图2所示。MultiBus-CPU模块选用Atmel公司的AT91RM9200为主处理器,融合了ARM920T ARM Thumb处理器。其工作于180 MHz时性能高达200 MIPS;具备存储器管理单元,可以运行Linux等实时操作系统;具备10/100 Base-T型以太网卡接口,只需外扩一个PHY即可实现以太网通信;具备USB 2.0全速(12 Mb/s)主机双端口,可以扩展键盘、鼠标、U盘等标准外设。

主处理器AT91RM9200具备5个串口:1个DEBUG串口,设计为RS232接口,可以直接连接PC的串口进行调试;1个RS485接口,可以与其他功能模块的RS485接口组成网络;其余3个串口均设计为RS232接口。

通过CPU模块的外部总线和Epson公司的S1D13506显示芯片扩展了一个VGA接口,分辨率为640×480,256色。IS41LVl6100为其提供独立显存,容量为1M×16位,支持EDO PAGE模式。

GL850A芯片是一个低功耗的USB 2.0 HUB控制器,AT91RM9200本身的USB HOST接口通过GL850A芯片扩展为4个USB HOST接口。

DS3231是精度非常高的I2C集成实时时钟。其精度在0~40℃内高达±2 ppm,在-40~85℃内精度可达±3.5ppm;板载电池,掉电后可以保持时间;可为系统提供秒、分、小时、日、日期、月、年等信息,具有自动闰年调整功能。

WM8731是一个低功耗网络音频编解码器(CODEC),具有输出功率放大器和可编程采样速率设定功能。WM8731芯片通过I2S接口与CPU连接,为CPU模块扩展了音频信号的输入输出接口,使系统具备音频采样功能,音频信号数字化后可以通过以太网传送。

DM9161为10/100M快速以太网物理层单芯片收发器,H1102为网络隔离变压器,用于实现10/100M自适应的可靠网络传输功能。

MultiBus-CPU模块通过增加显示控制芯片及其驱动实现了显示接口,系统运行信息可以直接通过VGA显示器显示出来,大大提高了人机交互的可操作性。

3 显示模块硬件设计方案

3.1 接口芯片选择

接口芯片选用Epson公司生产的大规模显示控制器S1D13506。它是以SEDl354控制器为基础发展起来的具有更多功能的LCD显示控制器,支持全类型、大规模的LCD及CRT/TV显示器。S1D13506内置RAMDAC(Random Access Memory Digital-to-Analog Converter,随机数模转换记忆体)硬件X-Y轴转置二维加速器,共有114个寄存器,可以灵活地设置各种不同的显示方式。

3.2 接口硬件设计

S1D13506与处理器的接口采用通用类型总线(包括数据总线、地址总线、控制总线)。接口定义如表1所列。芯片所用像素时钟CLK1、CLK2是由同步信号发生器ICS1523来提供的,外接1M×16位的EDO-DRAM IS41LV16100。

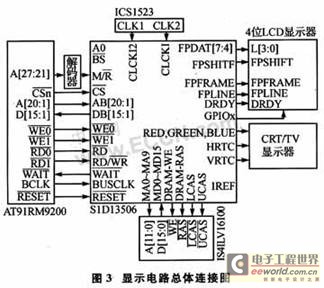

图3是显示电路总体连接图。S1D13506连接到AT9IRM9200的信号有:M/R、AB1~AB20、DB1~DB15、WE0、WE1、RD、RD/WR、CS、RFSET、BUSCLK、WAIT。连接到ICSl523的信号有:CLCKI、CLCK12(用于内部显示及外部媒体接口时钟)。连接到IS41LVl6100的信号有:DRAM-WE、DRAM-RAS、LCAS、UCAS、MA0~MA9、MD0~MD15。其中,MD1、MD2、MD4、MD6、MD15需要外接上拉电阻用于S1D13506初始配置。其他控制信号连接到LCD/CRT显示器。S1D13506芯片有个测试使能引脚TFSTEN在芯片正常工作时接地。如果不使用RAMDAC的数模转换功能,那么IREF引脚必须接地。ICS1523通过I2C串行总线(TWD、TWCK)接受AT91RM9200对它的寄存器配置。本设计中,ICS1523的输入时钟是50 MHz,输出CLK1为25 MHz,CLK2为12.5 MHz。

1 MultIBus-CPU模块软件设计方案

为了满足实际应用对实时性的要求,MultiBus-CPU模块软件采用了Linux 2.6.21操作系统。其中,Linux 2.6的内核任务可以被抢占,这一特性使得Linux 2.6内核适用于实时系统和嵌入式系统中。驱动程序在Linux环境下进行开发,应用层采用标准的通信协议——Modbus协议,控制设备可以连成工业网络进行集中监控。通过一致的Modbus接口,MultiBus-CPU模块与扩展下位机均可作为对等设备在工业网络中进行对话,使得各个设备无缝接人到工业控制网络中。MNtiBus-CPU模块支持现阶段工业测控系统中最常用的以太网(UDP)通信及RS485通信协议。因此,本模块在与其他功能模块进行通信时,采用Modbus-RTU数据通信方式,利用以太网(UDP)/RS485总线进行数据的发送与接收,实现对各功能模块的集中监控。软件总体结构如图1所示。

2 MultiBus-CPU模块硬件设计方案

硬件设计原理图如图2所示。MultiBus-CPU模块选用Atmel公司的AT91RM9200为主处理器,融合了ARM920T ARM Thumb处理器。其工作于180 MHz时性能高达200 MIPS;具备存储器管理单元,可以运行Linux等实时操作系统;具备10/100 Base-T型以太网卡接口,只需外扩一个PHY即可实现以太网通信;具备USB 2.0全速(12 Mb/s)主机双端口,可以扩展键盘、鼠标、U盘等标准外设。

主处理器AT91RM9200具备5个串口:1个DEBUG串口,设计为RS232接口,可以直接连接PC的串口进行调试;1个RS485接口,可以与其他功能模块的RS485接口组成网络;其余3个串口均设计为RS232接口。

通过CPU模块的外部总线和Epson公司的S1D13506显示芯片扩展了一个VGA接口,分辨率为640×480,256色。IS41LVl6100为其提供独立显存,容量为1M×16位,支持EDO PAGE模式。

GL850A芯片是一个低功耗的USB 2.0 HUB控制器,AT91RM9200本身的USB HOST接口通过GL850A芯片扩展为4个USB HOST接口。

DS3231是精度非常高的I2C集成实时时钟。其精度在0~40℃内高达±2 ppm,在-40~85℃内精度可达±3.5ppm;板载电池,掉电后可以保持时间;可为系统提供秒、分、小时、日、日期、月、年等信息,具有自动闰年调整功能。

WM8731是一个低功耗网络音频编解码器(CODEC),具有输出功率放大器和可编程采样速率设定功能。WM8731芯片通过I2S接口与CPU连接,为CPU模块扩展了音频信号的输入输出接口,使系统具备音频采样功能,音频信号数字化后可以通过以太网传送。

DM9161为10/100M快速以太网物理层单芯片收发器,H1102为网络隔离变压器,用于实现10/100M自适应的可靠网络传输功能。

MultiBus-CPU模块通过增加显示控制芯片及其驱动实现了显示接口,系统运行信息可以直接通过VGA显示器显示出来,大大提高了人机交互的可操作性。

3 显示模块硬件设计方案

3.1 接口芯片选择

接口芯片选用Epson公司生产的大规模显示控制器S1D13506。它是以SEDl354控制器为基础发展起来的具有更多功能的LCD显示控制器,支持全类型、大规模的LCD及CRT/TV显示器。S1D13506内置RAMDAC(Random Access Memory Digital-to-Analog Converter,随机数模转换记忆体)硬件X-Y轴转置二维加速器,共有114个寄存器,可以灵活地设置各种不同的显示方式。

3.2 接口硬件设计

S1D13506与处理器的接口采用通用类型总线(包括数据总线、地址总线、控制总线)。接口定义如表1所列。芯片所用像素时钟CLK1、CLK2是由同步信号发生器ICS1523来提供的,外接1M×16位的EDO-DRAM IS41LV16100。

图3是显示电路总体连接图。S1D13506连接到AT9IRM9200的信号有:M/R、AB1~AB20、DB1~DB15、WE0、WE1、RD、RD/WR、CS、RFSET、BUSCLK、WAIT。连接到ICSl523的信号有:CLCKI、CLCK12(用于内部显示及外部媒体接口时钟)。连接到IS41LVl6100的信号有:DRAM-WE、DRAM-RAS、LCAS、UCAS、MA0~MA9、MD0~MD15。其中,MD1、MD2、MD4、MD6、MD15需要外接上拉电阻用于S1D13506初始配置。其他控制信号连接到LCD/CRT显示器。S1D13506芯片有个测试使能引脚TFSTEN在芯片正常工作时接地。如果不使用RAMDAC的数模转换功能,那么IREF引脚必须接地。ICS1523通过I2C串行总线(TWD、TWCK)接受AT91RM9200对它的寄存器配置。本设计中,ICS1523的输入时钟是50 MHz,输出CLK1为25 MHz,CLK2为12.5 MHz。

总线 嵌入式 USB Linux Atmel ARM MIPS 解码器 放大器 收发器 变压器 显示器 LCD DAC 信号发生器 电路 电阻 电压 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 基于FPGA安全封装的身份认证模型研究(05-27)

- 高精度压力测控系统的试验研究(04-08)