利用时钟再生技术进行的极端的信号调整

时间:12-09

来源:互联网

点击:

由于PLL在时钟发生和分配中所起的作用持续增长因此将PLL转移函数用作减轻抖动的方法是值得考虑的这种采用PLL来减轻抖动的处理过程要求对其实现方法假定有一个可提供满足设计目标的足够编程选项的器件有一个全面深入的了解。

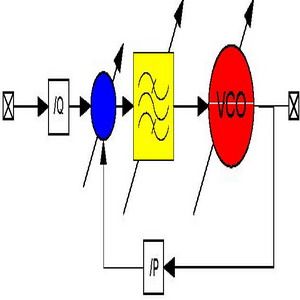

PLL具有可为上述采用带通滤波器来减轻抖动的方法提供跟踪功能的优点环路内部的增益和环路带宽组合通过改变响应来改变转移函数在处理高集成度的低成本PLL解决方案时通常会牺牲编程方面的灵活性包括更改常常是集成化的环路滤波器图3描绘了一种理想的PLL编程方案在该方案中电荷泵环路滤波器和VCO增益均可在一个扩展范围内进行修改然而如果没有仔细的分析以及准确的实验室结果则PLL实际上有可能造成系统的噪声增加这首先就从本质上使采用PLL的做法变得毫无意义。

图3可编程PLL架构

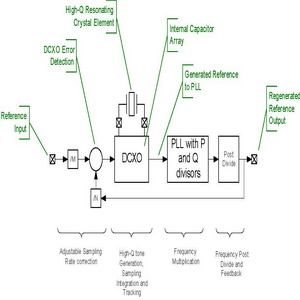

所需要的东西等效于一个频带非常窄的跟踪滤波器该滤波器接受一个具有RJ和DJ的输入且最终输出只产生尽可能低的本征RJ为此人们发现FailSafe架构具有那些饱受系统DJ困扰的系统所追寻的特性虽然RJ始终存在但减轻RJ被证明同样是值得考虑的FailSafeTM还根据高抖动衰减提出了大时钟倍频比的概念而这在采用标准PLL器件时是非常难以实现的由于我们正在处理的是如何减轻抖动因而此类应用完全有理由使用一个更加合适的名称在下文中所讨论的器件被称为带宽可调抖动衰减器或BAJA芯片。

4 BAJA架构概述

BAJA架构还支持一项额外功能该功能允许在器件中设置16种不同的抖动衰减模式模式的选择是通过外部引脚配置来完成的对于动态可重构系统来说这种方法被证明是极为有用的当在系统上进行电路板的插拔操作时噪声分布会发生改变BAJA的作用是为现有的特定电路板配置提供优化的抖动衰减可对一个FailSafe输出系统锁定进行逻辑监控以确保获得完全的器件同步。

5 实验的设计

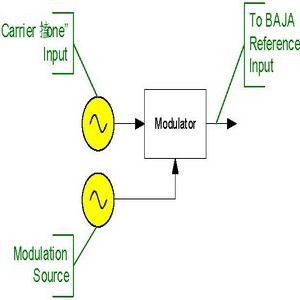

最为困难的工作之一是如何定义一组能够满足某些常见系统表示法的噪声条件选择了两种受控噪声注入分布该过程包括增加平均高斯白噪声我们的RJ影响以及通过对一个方波进行微分处理以抽取边缘速率信息的方法来进行脉冲调制后者的目的是在信号上生成一个DJ分量载波音输入由一个噪声层特性远远低于噪声调制分布的无干扰型音频发生器提供的该载频的漂移也非常低于是长期抖动特性保持稳定载频和调制信号源输入均被馈入调制器而调制器的输出则被传递给至BAJA器件的基准输入。

由于噪声测量从很大程度上来说是一种统计特性测量因此我们的实验设计要求采用归一化常数来获得一个基准点在这种场合调制指数将被增加直到一个1ns峰-峰测量结果能够在10s的最大时间窗口间隔上保持一致为止从统计的立场出发我们的分析捕获了至少6的采样内容。

图5测试输入配置

我们所做的第一个试验是采用一个具有良好工作性能的白高斯噪声信号源来对一个音调进行调制对于脉冲系统必须规定重复频率和占空比的选择依据对于脉冲频率研究了100kHz和33kHz两种设计依据其中100kHz用于模拟一个开关模式电源而33kHz则用于受EMI影响的系统和扩频定时解决方案中的典型调制频率当占空比被选为50%时脉冲频率即被选定为33kHz调制信号源的频率被增加直至观测到一个1ns的峰-峰输出调制幅度为止。

6 试验结果

表1罗列了针对BAJA配置的编程参数设置由于BAJA是可编程的故可以选用多种系统专用频率本次试验的目的在于将一个分别满足2.048MHz和155.52MHz的输入和输出标准的晶体用作通用通信频率并未尝试针对输入DJ来优化校正速率。

表1BAJA可编程配置

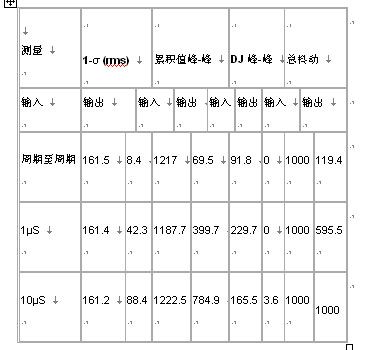

表2至表4 汇总了实验室数据结果针对AWGN输入条件进行了三项测量并采用脉冲注入对DJ进行了相同项目的测量每组测量均包括周期至周期以及1s和10s间隔这三个项目对各个BAJA输入至输出做了比较表4包括了本征测量以便于对实验室设置的噪声层有一个更好的认识虽然本征噪声层看上去并不令人满意今后还需在某些方面加以改进但毋庸置疑的是BAJA在未调制条件下将继续展现优良的工作性能。

表2AWGN输入的累积抖动单位ps 。

表3方波调制的累积抖动单位ps

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 卫星电源分系统可靠性设计与研究(02-12)