基于CPLD的时间控制器设计

时间:12-08

来源:互联网

点击:

传统时间控制器功能简单,硬件线路多,设计复杂,可靠性差。随着CPLD(复杂可编程逻辑器件)的飞速发展,它以其编程方便、集成度高,速度快、价格低等特点越来越受到广大电子设计人员的青睐。

本文介绍一种以CPLD为核心、以VHDL为开发工具的时间控制器,该控制器不仅具有时间功能,而且具有定时器功能,能在00:00~23:59之间任意设定开启时间和关闭时间,其设置方便、灵活,广泛应用于路灯、广告灯箱、霓虹灯等处的定时控制。

1 系统设计方案

1.1 系统总体结构

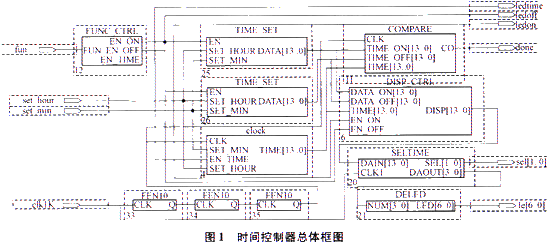

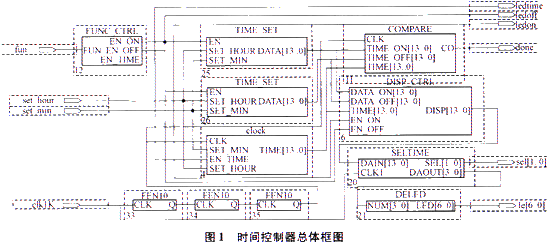

时间控制器主要由CLOCK(数字时钟)、TIMESET(定时器开启时间和关闭时间设置)、COMPARE(比较输出)、FUNC-CTRL(功能控制模块)和显示输出控制模块等组成。

系统方框图如图l所示。

FUNC-CTRL模块控制系统处于不同的功能状态,并产生不同的控制信号分别控制TIME-SET模块和CLOCK模块,而这3个模块的输出连接到COMPARE模块,当系统时间处在开启时间和关闭时间段时,则定时器输出端done输出控制信号,DISP_CTRL(输出选择模块)根据功能模块的控制信号选择不同功能状态的时间输出,通过SELTIME(动态扫描模块)和DELED(七段译码模块)驱动七段数码管显示相应的时间。

1.2 系统功能要求

a)具有数字时钟功能,用4个数码管分别显示小时、分钟,并且具有时间校对功能。

b)能方便地设定定时器的开启时间和关闭时间,通过比较器输出时间控制信号。

c)具有4种功能状态:系统时间校对状态、开启时间设定状态、关闭时间设定状态、时钟正常显示状态,通过功能转换键(fun)可以使系统在这4种状态之间循环变化,并且可以通过指示灯LED显示当前系统功能状态,数码管显示相应功能状态的时间,如当前在开启时间设定状态下,开启时间设置指示灯ledon会亮,数码管同时显示当前设置的时间。

d)开启时间设定、关闭时间设定和时间校对采用共同的时调节键set_hour和分调节键set_min;每按一下set_hour键,小时就会自动加1,采用24进制计数,当计数到23时又会恢复为00;每按一下set_min键,分钟会自动加1;采用60进制计数,当计数到59时,又会恢复为00。

2 子模块功能设计及仿真

2.1 CLOCK模块

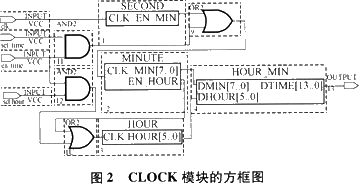

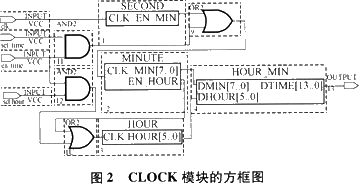

CLOCK模块内部整体框图如图2所示。

其中:SECOND为60进制秒计数器,MINUTE为60进制分钟计数器,HOUR为24进制小时计数器;clk为标准的1Hz时钟信号作为秒计数输入,秒计数器的进位输出作为分钟MINUTE的计数时钟,而MINUTE进位输出作为小时HOUR模块的时钟输入;输入端set_rain、set_hour和en_time分别为校分、校时和时间设置控制信号。模块HOUR_MIN把小时和分钟输出合成时间输出信号time[13..0](小时采用24进制,只需6位二进制表示,分钟用8位二进制表示)。

2.2 TIME_SET模块

开启时问模块主要设置定时器歼启时间,可以设定具体几时几分,而关闭时间则设定定时器关闭时间,起始时间设定模块与结束时间设定模块功能相同,采用同一个TIME_SET模块。该模块由一个24进制小时计数器和一个60进制分钟计数器组成,当控制端EN为高电平时,通过调节键set_hour和set_min分别设置小时和分钟信号,从而设置开启时问和关闭时间,并产生时间信号data[13..0]。仿真结果如图3所示。

2.3 COMPARE模块

COMPARE模块实现系统当前时间与设定的开启时间和关闭时间的比较,从而输出定时控制输出信号。由于系统时间的小时和分钟分别采用24进制和60进制方式,分3种情况讨论:

a)当系统设定的开启时间小于关闭时间时,只要当前系统时间大于等于开启时间而小于关闭时间,则输出端co的输出信号为高电平,否则为低电平。

b)当系统设定的开启时间大于关闭时间时,则当系统时间大于等于关闭时间而小于开启时间时,输出端co为低电平,否则为高电平。

c)如果开启时间等于关闭时间,则输出端co为低电平,仿真结果如图4。

该模块部分VHDL源程序如下:

2.4 FUNC_CTRL模块

利用功能转换键(fun)使系统处在不同的功能状态:系统时间校对状态、开启时间设定状态、关闭时间设定状态、正常显示状态。利用功能转换键实现4个功能状态之间循环变化,并产生相应的控制信号(en_time、en_on、en_off)去控制CLOCK模块、TIME_SET、模块和DISP_CTRL模块等。在调整过程中,只有被选择到的功能状态指示灯被点亮,其他灯不亮,在正常模式状态下,状态灯都不亮。

其部分源程序如下:

2.5 显示控制模块

1)DISP_CTRL模块

该模块根据功能控制模块输出的控制信号en_on、en_off的值来选择输出信号,当en_on=l时,输出值为定时器的开启时问信号,当en_off=1时,输出值为定时器的关闭时间信号,en_time=1时,输出值为系统时间校对信号,其他情况则输出系统时间。

2)SELTIME模块及DELED模块

时间显示的4个数码管采用动态扫描输出,一般只要每个扫描频率超过人的眼睛视觉暂留频率24 Hz以上就可以达到点亮单个显示而不闪烁,扫描频率采用1 kHz信号。动态扫描输出信号通过BCD-七段显示译码器(DELED)连接到数码管显示具体数字。

动态扫描的部分程序如下(其中clk1为扫描时钟输入信号,sel为数码管片选信号):

2.6 1 Hz标准时钟产生模块

系统时钟输入信号CLK1K为1 kHz信号,它可作为动态扫描时钟信号,如果把1 kHz信号经过3个10分频器FEN10便可得到标准的1 Hz时钟信号,作为系统时间模块的标准秒输入信号。

本文介绍一种以CPLD为核心、以VHDL为开发工具的时间控制器,该控制器不仅具有时间功能,而且具有定时器功能,能在00:00~23:59之间任意设定开启时间和关闭时间,其设置方便、灵活,广泛应用于路灯、广告灯箱、霓虹灯等处的定时控制。

1 系统设计方案

1.1 系统总体结构

时间控制器主要由CLOCK(数字时钟)、TIMESET(定时器开启时间和关闭时间设置)、COMPARE(比较输出)、FUNC-CTRL(功能控制模块)和显示输出控制模块等组成。

系统方框图如图l所示。

FUNC-CTRL模块控制系统处于不同的功能状态,并产生不同的控制信号分别控制TIME-SET模块和CLOCK模块,而这3个模块的输出连接到COMPARE模块,当系统时间处在开启时间和关闭时间段时,则定时器输出端done输出控制信号,DISP_CTRL(输出选择模块)根据功能模块的控制信号选择不同功能状态的时间输出,通过SELTIME(动态扫描模块)和DELED(七段译码模块)驱动七段数码管显示相应的时间。

1.2 系统功能要求

a)具有数字时钟功能,用4个数码管分别显示小时、分钟,并且具有时间校对功能。

b)能方便地设定定时器的开启时间和关闭时间,通过比较器输出时间控制信号。

c)具有4种功能状态:系统时间校对状态、开启时间设定状态、关闭时间设定状态、时钟正常显示状态,通过功能转换键(fun)可以使系统在这4种状态之间循环变化,并且可以通过指示灯LED显示当前系统功能状态,数码管显示相应功能状态的时间,如当前在开启时间设定状态下,开启时间设置指示灯ledon会亮,数码管同时显示当前设置的时间。

d)开启时间设定、关闭时间设定和时间校对采用共同的时调节键set_hour和分调节键set_min;每按一下set_hour键,小时就会自动加1,采用24进制计数,当计数到23时又会恢复为00;每按一下set_min键,分钟会自动加1;采用60进制计数,当计数到59时,又会恢复为00。

2 子模块功能设计及仿真

2.1 CLOCK模块

CLOCK模块内部整体框图如图2所示。

其中:SECOND为60进制秒计数器,MINUTE为60进制分钟计数器,HOUR为24进制小时计数器;clk为标准的1Hz时钟信号作为秒计数输入,秒计数器的进位输出作为分钟MINUTE的计数时钟,而MINUTE进位输出作为小时HOUR模块的时钟输入;输入端set_rain、set_hour和en_time分别为校分、校时和时间设置控制信号。模块HOUR_MIN把小时和分钟输出合成时间输出信号time[13..0](小时采用24进制,只需6位二进制表示,分钟用8位二进制表示)。

2.2 TIME_SET模块

开启时问模块主要设置定时器歼启时间,可以设定具体几时几分,而关闭时间则设定定时器关闭时间,起始时间设定模块与结束时间设定模块功能相同,采用同一个TIME_SET模块。该模块由一个24进制小时计数器和一个60进制分钟计数器组成,当控制端EN为高电平时,通过调节键set_hour和set_min分别设置小时和分钟信号,从而设置开启时问和关闭时间,并产生时间信号data[13..0]。仿真结果如图3所示。

2.3 COMPARE模块

COMPARE模块实现系统当前时间与设定的开启时间和关闭时间的比较,从而输出定时控制输出信号。由于系统时间的小时和分钟分别采用24进制和60进制方式,分3种情况讨论:

a)当系统设定的开启时间小于关闭时间时,只要当前系统时间大于等于开启时间而小于关闭时间,则输出端co的输出信号为高电平,否则为低电平。

b)当系统设定的开启时间大于关闭时间时,则当系统时间大于等于关闭时间而小于开启时间时,输出端co为低电平,否则为高电平。

c)如果开启时间等于关闭时间,则输出端co为低电平,仿真结果如图4。

该模块部分VHDL源程序如下:

2.4 FUNC_CTRL模块

利用功能转换键(fun)使系统处在不同的功能状态:系统时间校对状态、开启时间设定状态、关闭时间设定状态、正常显示状态。利用功能转换键实现4个功能状态之间循环变化,并产生相应的控制信号(en_time、en_on、en_off)去控制CLOCK模块、TIME_SET、模块和DISP_CTRL模块等。在调整过程中,只有被选择到的功能状态指示灯被点亮,其他灯不亮,在正常模式状态下,状态灯都不亮。

其部分源程序如下:

2.5 显示控制模块

1)DISP_CTRL模块

该模块根据功能控制模块输出的控制信号en_on、en_off的值来选择输出信号,当en_on=l时,输出值为定时器的开启时问信号,当en_off=1时,输出值为定时器的关闭时间信号,en_time=1时,输出值为系统时间校对信号,其他情况则输出系统时间。

2)SELTIME模块及DELED模块

时间显示的4个数码管采用动态扫描输出,一般只要每个扫描频率超过人的眼睛视觉暂留频率24 Hz以上就可以达到点亮单个显示而不闪烁,扫描频率采用1 kHz信号。动态扫描输出信号通过BCD-七段显示译码器(DELED)连接到数码管显示具体数字。

动态扫描的部分程序如下(其中clk1为扫描时钟输入信号,sel为数码管片选信号):

2.6 1 Hz标准时钟产生模块

系统时钟输入信号CLK1K为1 kHz信号,它可作为动态扫描时钟信号,如果把1 kHz信号经过3个10分频器FEN10便可得到标准的1 Hz时钟信号,作为系统时间模块的标准秒输入信号。

CPLD 电子 VHDL LED 比较器 仿真 Altera EDA 电路 相关文章:

- 基于DSP高精度伺服位置环设计(06-21)

- 双目三维定位的视频运动检测控制系统设计(01-21)

- 图像采集系统的Camera Link标准接口设计(01-16)

- 激光微加工系统及基于DSP+FPGA的控制单元的研究(03-05)

- 基于USB2.0技术的高速双路数据采集系统(03-07)

- 基于MATLAB用于谐波检测的数字低通滤波器的设计(03-11)