工业现场CAN总线技术在航天领域的应用

时间:12-07

来源:互联网

点击:

4星载计算机中的双冗余容错can总线设计

图1描述了基于can的双冗余总线结构。基于can总线的双冗余系统通信总线的基本设计思想是在卫星各功能模块之间布下两条基于can的系统通信总线,即用两套can总线控制模块分别连接到总线bus0和bus1上。正常情况下优先在一条总线上通信,这条总线出现故障时通过另一条进行通信并重新初始化出错的总线以备将来再用。这样即使一条通信通道故障后不会影响整个系统的数据交换,大大提高了通信的可靠性。

图1 基于can的双冗余总线结构

图2 can总线硬件设计原理简图

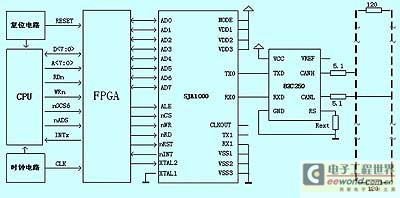

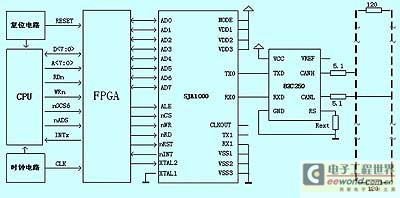

图2为星载计算机中can总线硬件设计原理框图。 can总线协议控制芯片选用philip的工业级器件sja1000,收发器选用philip的pca82c250。cpu与sja1000的接口控制逻辑通过actel的反熔丝fpga实现。sja1000工作在intel模式,工作时钟为7.3728mhz。复位信号通过max708产生。为了有更好的emc/emi性能和抑制比较器的噪声,vdd通过rc滤波器退耦。

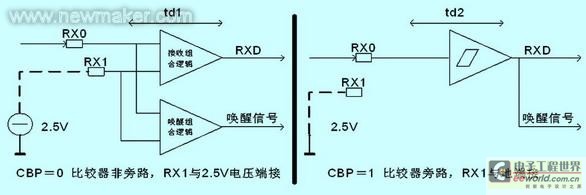

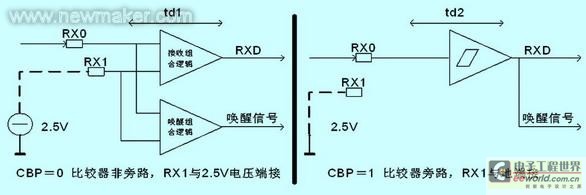

SJA1000的RX1信号处理非常关键。如果使用外部集成收发器电路而且没有在时钟分频寄存器里使能比较器旁路功能,RX1输出要被连接到2.5V的参考电压(82C250的Vref输出)。图3显示了CBP的两种设置所对应的电路。对于使用82C250集成的收发器电路,SJA1000的相关数据手册建议使用旁路功能,即CBP设置为1,在这种情况下,SJA1000的比较器旁路功能有效,减少了内部传播延迟,即td2[td]

图3 SJA1000的接收输入比较器旁路设计

82C250的RS信号通过电阻Rext接地。RS管脚的电流决定了传输介质上传输信号的信号沿的陡峭程度,Rext阻值的大小必须根据CAN总线的工作速度及其工作环境进行设计和选择,具体可参见SJA1000的数据手册或者应用文档。

5 CPU与SJA1000的接口逻辑设计

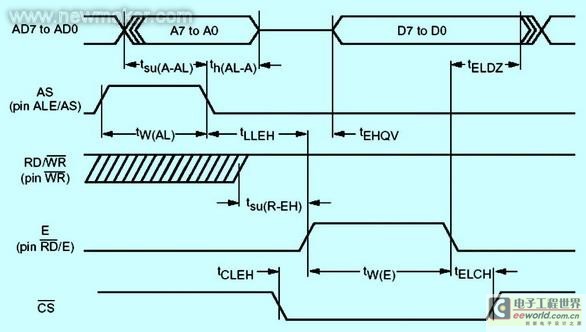

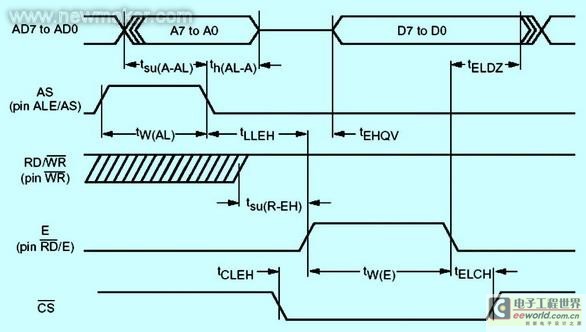

星载计算机的CPU不同于8086,采用的是独立地址和数据总线。CAN总线控制器SJA1000采用地址/数据总线复用方式,需要将CPU的总线信号经过适当逻辑处理后才能够满足CAN总线控制器的时序要求。图4和图5是SJA1000在Intel模式下的读写时序。

图4 SJA1000读时序(Intel模式)

图5 SJA1000写时序(Intel模式)

按照SJA1000的数据手册,确保SJA1000的读写正确,如下的时序参数必须满足:

l tW(AL):必须保证ALE的时间,最小不能小于8ns;

l tLLRL/tLLWL:读写时ALE无效到读写信号有效的时间,最小不能小于10ns;

l tLCRL/tLCWL:片选信号有效后读写信号有效的时间,最小不能小于0,即片选有效必须出现在读写信号有效前;

l tW(R):读信号有效宽度,最小不能小于40ns;

l tW(R):写信号有效宽度,最小不能小于20ns;

l tWHLH:写信号无效到下一次ALE有效的时间,最小不能小于15ns;

l th(AL-A):在ALE为低电平后地址应该保持时间,最小不能小于2ns。

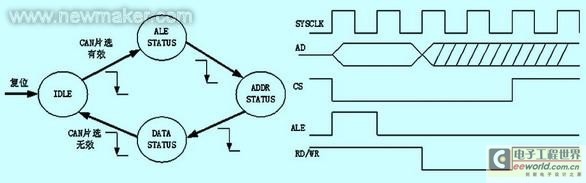

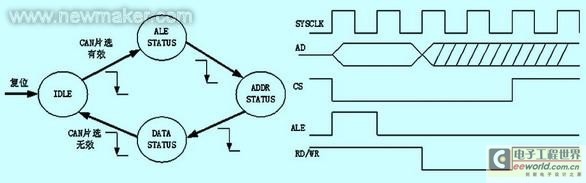

CPU和CAN总线接口采用地址直接映射。接口时序设计重点是接口控制逻辑必须产生符合上述关键参数的读写时序。如果简单的按照ALE<=not nADS方法处理,不满足要求时序关系,这在调试过程中已经得到验证。为此,在设计中采用了FPGA技术,以求很好地解决CAN总线与CPU的接口问题。图6描述了通过VHDL编写实现接口电路的状态转移图和FPGA设计产生的读写CAN总线时序,其中时钟周期不低于67ns,该时序满足SJA1000要求。

图6 CAN总线接口时序设计的状态转移和时序

6 CAN总线通讯软件的设计

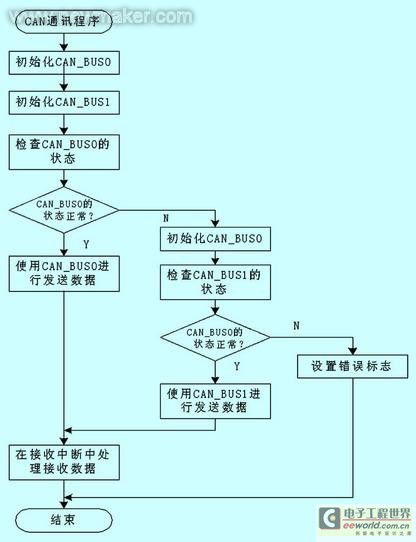

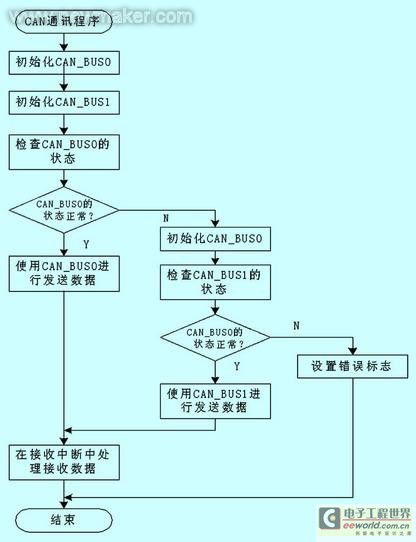

双冗余总线结构的通讯软件主要由初始化、接收和发送三个模块组成,控制流图见图7。在程序设计时采用了SJA1000的Basic模式,初始化中需要对BUS0和BUS1分别进行初始化,包括SJA1000的控制寄存器、接收代码寄存器、接收屏蔽寄存器、总线时序寄存器等。

图 7 CAN总线通讯软件的控制流图

发送模块采用主动发送方式,BUS0为优先通讯通道,若BUS0通道状态不正常,则启动BUS1通道进行通讯,并对BUS0通道进行初始化以备下次通讯时使用。

接收模块采用中断接收方式,为了保证接收到的数据被实时处理,CAN总线的接收中断被设置为高优先级中断。在接收中断中首先判断接收通道是BUS0还是BUS1,然后从接收通道按数据长度进行数据接收。

7 结束语

CAN总线技术的诸多优点如实时性好,通信速率高,抗干扰能力强,低廉的价格等使它不仅广泛应用于工业控制领域,而且开始向航天领域进军。其COTS工业级器件SJA1000经过飞行也得到了验证,CAN总线适宜航天应用的特点得到了充分的展示和飞行验证。

图1描述了基于can的双冗余总线结构。基于can总线的双冗余系统通信总线的基本设计思想是在卫星各功能模块之间布下两条基于can的系统通信总线,即用两套can总线控制模块分别连接到总线bus0和bus1上。正常情况下优先在一条总线上通信,这条总线出现故障时通过另一条进行通信并重新初始化出错的总线以备将来再用。这样即使一条通信通道故障后不会影响整个系统的数据交换,大大提高了通信的可靠性。

图1 基于can的双冗余总线结构

图2 can总线硬件设计原理简图

图2为星载计算机中can总线硬件设计原理框图。 can总线协议控制芯片选用philip的工业级器件sja1000,收发器选用philip的pca82c250。cpu与sja1000的接口控制逻辑通过actel的反熔丝fpga实现。sja1000工作在intel模式,工作时钟为7.3728mhz。复位信号通过max708产生。为了有更好的emc/emi性能和抑制比较器的噪声,vdd通过rc滤波器退耦。

SJA1000的RX1信号处理非常关键。如果使用外部集成收发器电路而且没有在时钟分频寄存器里使能比较器旁路功能,RX1输出要被连接到2.5V的参考电压(82C250的Vref输出)。图3显示了CBP的两种设置所对应的电路。对于使用82C250集成的收发器电路,SJA1000的相关数据手册建议使用旁路功能,即CBP设置为1,在这种情况下,SJA1000的比较器旁路功能有效,减少了内部传播延迟,即td2[td]

图3 SJA1000的接收输入比较器旁路设计

82C250的RS信号通过电阻Rext接地。RS管脚的电流决定了传输介质上传输信号的信号沿的陡峭程度,Rext阻值的大小必须根据CAN总线的工作速度及其工作环境进行设计和选择,具体可参见SJA1000的数据手册或者应用文档。

5 CPU与SJA1000的接口逻辑设计

星载计算机的CPU不同于8086,采用的是独立地址和数据总线。CAN总线控制器SJA1000采用地址/数据总线复用方式,需要将CPU的总线信号经过适当逻辑处理后才能够满足CAN总线控制器的时序要求。图4和图5是SJA1000在Intel模式下的读写时序。

图4 SJA1000读时序(Intel模式)

图5 SJA1000写时序(Intel模式)

按照SJA1000的数据手册,确保SJA1000的读写正确,如下的时序参数必须满足:

l tW(AL):必须保证ALE的时间,最小不能小于8ns;

l tLLRL/tLLWL:读写时ALE无效到读写信号有效的时间,最小不能小于10ns;

l tLCRL/tLCWL:片选信号有效后读写信号有效的时间,最小不能小于0,即片选有效必须出现在读写信号有效前;

l tW(R):读信号有效宽度,最小不能小于40ns;

l tW(R):写信号有效宽度,最小不能小于20ns;

l tWHLH:写信号无效到下一次ALE有效的时间,最小不能小于15ns;

l th(AL-A):在ALE为低电平后地址应该保持时间,最小不能小于2ns。

CPU和CAN总线接口采用地址直接映射。接口时序设计重点是接口控制逻辑必须产生符合上述关键参数的读写时序。如果简单的按照ALE<=not nADS方法处理,不满足要求时序关系,这在调试过程中已经得到验证。为此,在设计中采用了FPGA技术,以求很好地解决CAN总线与CPU的接口问题。图6描述了通过VHDL编写实现接口电路的状态转移图和FPGA设计产生的读写CAN总线时序,其中时钟周期不低于67ns,该时序满足SJA1000要求。

图6 CAN总线接口时序设计的状态转移和时序

6 CAN总线通讯软件的设计

双冗余总线结构的通讯软件主要由初始化、接收和发送三个模块组成,控制流图见图7。在程序设计时采用了SJA1000的Basic模式,初始化中需要对BUS0和BUS1分别进行初始化,包括SJA1000的控制寄存器、接收代码寄存器、接收屏蔽寄存器、总线时序寄存器等。

图 7 CAN总线通讯软件的控制流图

发送模块采用主动发送方式,BUS0为优先通讯通道,若BUS0通道状态不正常,则启动BUS1通道进行通讯,并对BUS0通道进行初始化以备下次通讯时使用。

接收模块采用中断接收方式,为了保证接收到的数据被实时处理,CAN总线的接收中断被设置为高优先级中断。在接收中断中首先判断接收通道是BUS0还是BUS1,然后从接收通道按数据长度进行数据接收。

7 结束语

CAN总线技术的诸多优点如实时性好,通信速率高,抗干扰能力强,低廉的价格等使它不仅广泛应用于工业控制领域,而且开始向航天领域进军。其COTS工业级器件SJA1000经过飞行也得到了验证,CAN总线适宜航天应用的特点得到了充分的展示和飞行验证。

总线 自动化 电子 传感器 滤波器 收发器 比较器 电路 电压 电阻 电流 CAN总线 FPGA VHDL 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 基于FPGA安全封装的身份认证模型研究(05-27)

- 高精度压力测控系统的试验研究(04-08)