基于DSP的嵌入式视觉客流检测系统的设计

时间:11-27

来源:互联网

点击:

近些年来,随着电子元器件价格的不断降低和数字信号处理器(Digital Signal Processor,DSP)性能的不断提升,以DSP为核心的嵌入式实时图像处理技术在目标跟踪、机器人导航、辅助驾驶、智能交通监控等领域获得了越来越广泛的应用。由于图像的实时处理与图像数据的实时采集、存储和传输密切相关,因而各模块间的无缝连接与高效配合是嵌入式图像处理系统设计过程中的关键问题。综合考虑系统的实现成本、实时性以及实际应用,在嵌入式图像处理技术的许多应用领域中,如视频监控以及视觉客流检测等,由于对图像质量要求不是很高,处理算法相对简单,采用低端DSP(如Ti公司的C5000系列等)就可以完成相应的图像处理任务,面向这些实际应用领域的嵌入式图像处理系统完全可以采用低端DSP作为系统的处理核心,因此将以低端DSP为核心构建面向客流检测实际应用的嵌入式图像处理系统。另外,与其他图像数据传输方式(如串口、并口和USB等)相比,以太网接口具有传输速度快,成本低廉,开发简便以及可以实现远程控制等一系列优点,因而提出的嵌入式图像处理系统的图像传输部分将采用基于TCP/IP协议的以太网传输技术实现系统图像数据的远程传输功能。

1 系统构成

这里提出的基于DSP的嵌入式图像处理系统由图像采集与存储、图像处理和图像传输3部分组成,组成框图如图1所示。选用CMOS图像传感器OV7141完成系统的图像采集功能,选用TMS320VC5416DSP完成系统的图像处理与分析,采用FIFO存储器IDT72V04作为图像存储的缓冲区,采用10兆/lOO兆自适应网络控制器LAN9115实现图像数据的以太网传输功能,系统各模块间的逻辑控制由CPLI)EPM3064A实现。

2 系统的硬件实现

2.1 芯片介绍

考虑到视觉客流检测应用中的图像处理只涉及灰度图像,因而提出的嵌入式图像处理系统可以直接采用黑白图像传感器。这里选用Omnivision公司的黑白CMOS图像传感器OV7141作为图像采集芯片。该芯片工作电压为2.5 V,分辨率为640×480,工作频率为27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式),内部整合模数转换(A/D),自动增益控制(AGC),SCCB总线控制端口等,可直接输出8 b图像数据。

图像处理芯片采用TI公司的TMS320VC5416定点DSP,其内部采用一种改进型的哈佛总线结构(1条程序总线、3条数据总线和4条地址总线),数据总线宽度为16 b,最大寻址空间为64 K×16 b。程序总线宽度为23 b,最大寻址空间为8 M×16 b。片内有128 M×16 b的RAM(其中包括64 M×16 b的单周期双访问DARAM和64 M×16 b的单周期单访问SARAM),6通道DMA传输控制器,3个带缓冲器的串行通信接口(McBSP)。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160 MIPSE。

FIFO采用IDT公司的IDT72V04,它是异步的先进先出缓存器,容量为4096×9 b。供电电压为3.3 V,它有3个状态输出信号可用于图像数据存储与读取控制,即全满信号/FF、半满信号/HF和空信号/EF。CPLD采用ALTERA公司的MAX3064A,可使用门数1250个;宏单元64个;逻辑阵列块(LAB)4个;最大可使用输入输出(I/O)管脚数64个;最大工作时钟频率为222.2 MHz;核供电和I/O供电都为3.3 V。LAN9115是SMSC公司的第二代10兆/100兆非PCI以太网控制器,LAN9115设计有大容量的存储器缓冲器,快速总线周期时间和内置的流控制支持,LAN9115支持高的数据速率,几乎没有包的损失,支持多种高清晰度视频。LAN9115的主要性能:功率管理;支持LAN叫醒,使网络能把消费类电子产品从睡眠状态中叫醒;多种低功耗模式;能防止接收存储器溢出;内置支持流控制;简单SRAM系统接口;能与任何的嵌入处理器接口。

2.2 DSP与FIFO存储器的无缝连接与图像采集的实现

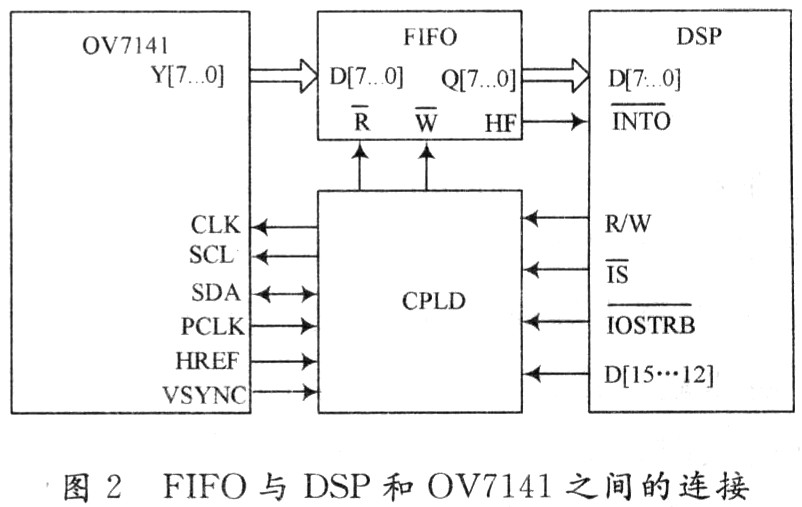

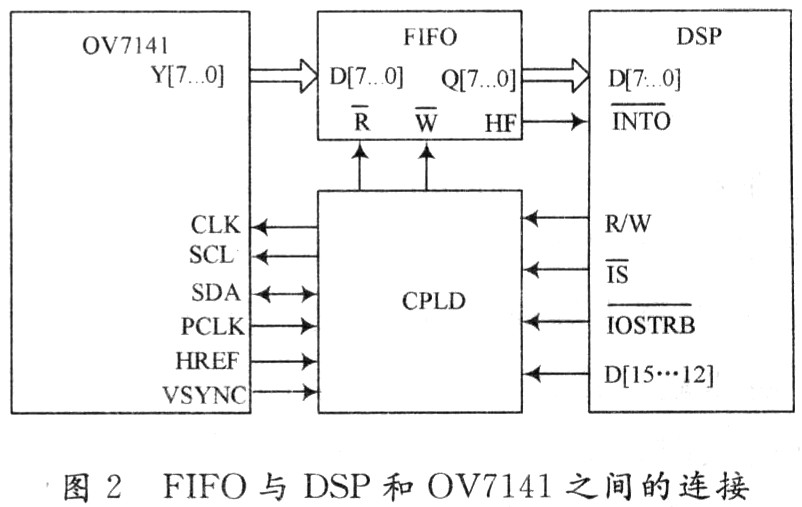

FIFO与DSP和OV7141的无缝连接如图2所示。OV7141的工作频率是27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式)。由于DSP性能有限,而且实际上很多情况下也不需要如此高的帧率,因此并不是所有采集到的图像数据都需要DSP进行处理(例如在视觉客流检测系统的实际应用中只要求每秒钟能处理5帧即可),但是必须保证DSF进行处理的图像为一幅完整的图像。可以利用OV7141的3个输出信号来完成这个功能,分别是PCLK(像素时钟信号)、VSYNC(场同步信号)和HREF(行有效信号)。并且OV7141可通过改变片内控制寄存器的值来调整输出图像的窗口大小,窗口可在4×2到652×482像素之间任意选择。HREF、只在所选择窗口内的像素信号输出时才置高电平,这使得图像的非完整模式下的处理也变为了可能。另外,0V7141的片内控制寄存器配置功能由SCCB总线实现,由于DSP不具有SCCB总线接口,因而为了通过DSP实现对0V7141的寄存器配置,利用DSP的2根数据线DO和D1借助CPLD实现sCcB总线时钟线SCL和数据线SDA的模拟以实现虚拟SCCB总线。

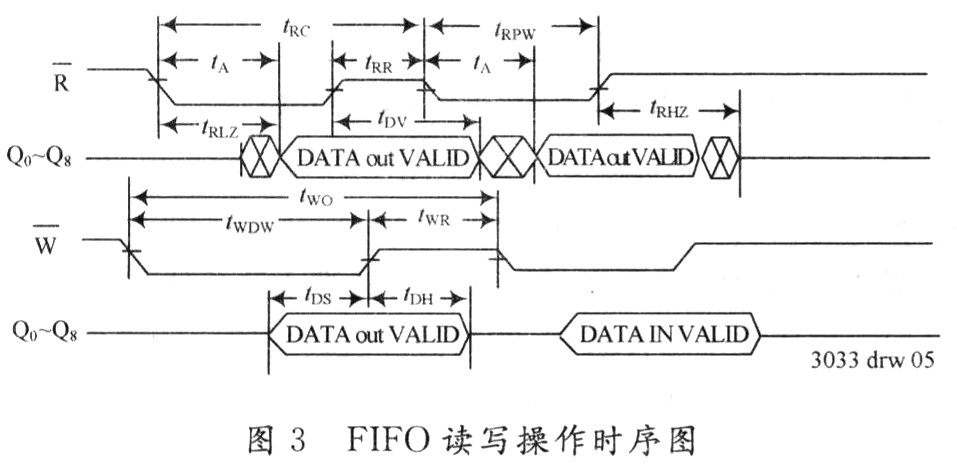

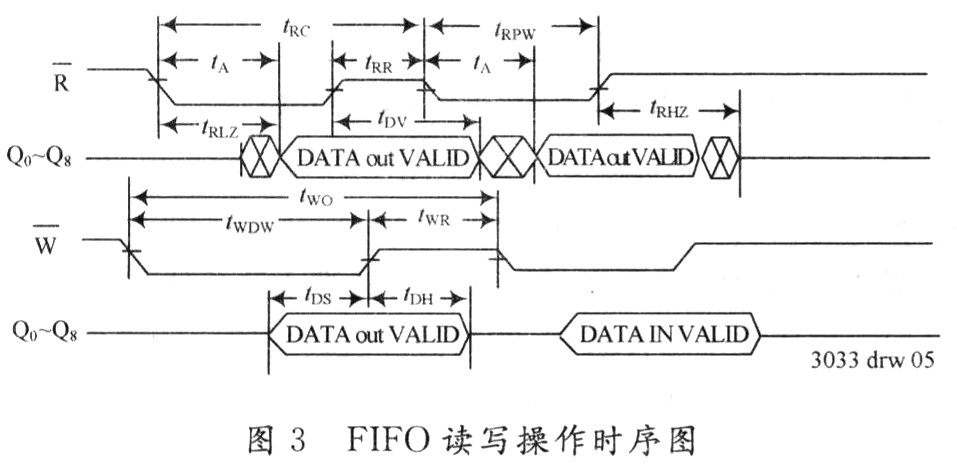

控制FIF0的信号主要是写信号和读信号,它们都由DSP根据FIF0的状态信号及DSP对图像的处理结果来控制对FIFO的读/写。读/写操作时序如图3所示。CM0s图像传感器采集获得的图像数据在CPLD控制下逐行写入FIFO,当FIFO的存储容量达到半满时,FIFO的半满标志位以外部中断方式通知DSP,DSP,检测到外部中断后开启DMA,利用DMA通道将FIFo中的图像数据搬移到DSP的片内图像缓冲区中。需要注意的是,在DMA从FIFO搬运图像数据的过程中CMOS图像传感器并没有停止向FIFO写入图像数据,由于CMOS写入FIFO速度Vw。比DMA从FIFO中读出数据的速度Vr慢(Vw=(1/2)Vr),使得CMOS和DMA在对FIFO进行双向访问时FIFO的实际存储容量始终保持在0和最大存储量之间,既不会上溢也不会下溢;从而保证一帧完整的图像可以被DMA控制器顺利的转移至DSP的片内图像缓冲区中。当一帧完整的图像搬运完成后,DMA会开启处理使能标志,当DSP发现处理使能标志开启后将从片内图像缓冲区中获得图像数据以完成图像处理算法,在DSP进行图像处理的同时,DMA控制器可以同时进行下一帧图像数据的搬移工作以提升系统的并行处理能力。DSP对于当前帧图像处理完成后将等待处理使能标志的再次开启以继续下一帧图像的处理。DSP对于当前帧图像的处理结果将在当前帧处理完成后采用以太网传输至接收终端。

此外,DMA在执行图像数据搬移功能时,为了保证数据搬移过程与DSP图像处理的并行性,通常需要在DSP片内开辟2块图像数据缓冲区。由于5416DSP片内DARAM在速度上优于SARAM,因而通常重要的程序代码以及算法的堆栈都放在DARAM中,为了节省DARAM资源并充分利用SARAM,在DSP程序空间所在的SARAM和数据空间所在的DARAM中各开辟1块作为图像数据缓冲区。SARAM中的缓冲区用于DMA通道0从FIF0中读取当前帧图像数据,DMA通道1从SARAM缓冲区中读取上一帧图像数据,两个DMA通道的数据搬移功能都可以在DSP完成某个子算法的过程中并行实现。

1 系统构成

这里提出的基于DSP的嵌入式图像处理系统由图像采集与存储、图像处理和图像传输3部分组成,组成框图如图1所示。选用CMOS图像传感器OV7141完成系统的图像采集功能,选用TMS320VC5416DSP完成系统的图像处理与分析,采用FIFO存储器IDT72V04作为图像存储的缓冲区,采用10兆/lOO兆自适应网络控制器LAN9115实现图像数据的以太网传输功能,系统各模块间的逻辑控制由CPLI)EPM3064A实现。

2 系统的硬件实现

2.1 芯片介绍

考虑到视觉客流检测应用中的图像处理只涉及灰度图像,因而提出的嵌入式图像处理系统可以直接采用黑白图像传感器。这里选用Omnivision公司的黑白CMOS图像传感器OV7141作为图像采集芯片。该芯片工作电压为2.5 V,分辨率为640×480,工作频率为27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式),内部整合模数转换(A/D),自动增益控制(AGC),SCCB总线控制端口等,可直接输出8 b图像数据。

图像处理芯片采用TI公司的TMS320VC5416定点DSP,其内部采用一种改进型的哈佛总线结构(1条程序总线、3条数据总线和4条地址总线),数据总线宽度为16 b,最大寻址空间为64 K×16 b。程序总线宽度为23 b,最大寻址空间为8 M×16 b。片内有128 M×16 b的RAM(其中包括64 M×16 b的单周期双访问DARAM和64 M×16 b的单周期单访问SARAM),6通道DMA传输控制器,3个带缓冲器的串行通信接口(McBSP)。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160 MIPSE。

FIFO采用IDT公司的IDT72V04,它是异步的先进先出缓存器,容量为4096×9 b。供电电压为3.3 V,它有3个状态输出信号可用于图像数据存储与读取控制,即全满信号/FF、半满信号/HF和空信号/EF。CPLD采用ALTERA公司的MAX3064A,可使用门数1250个;宏单元64个;逻辑阵列块(LAB)4个;最大可使用输入输出(I/O)管脚数64个;最大工作时钟频率为222.2 MHz;核供电和I/O供电都为3.3 V。LAN9115是SMSC公司的第二代10兆/100兆非PCI以太网控制器,LAN9115设计有大容量的存储器缓冲器,快速总线周期时间和内置的流控制支持,LAN9115支持高的数据速率,几乎没有包的损失,支持多种高清晰度视频。LAN9115的主要性能:功率管理;支持LAN叫醒,使网络能把消费类电子产品从睡眠状态中叫醒;多种低功耗模式;能防止接收存储器溢出;内置支持流控制;简单SRAM系统接口;能与任何的嵌入处理器接口。

2.2 DSP与FIFO存储器的无缝连接与图像采集的实现

FIFO与DSP和OV7141的无缝连接如图2所示。OV7141的工作频率是27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式)。由于DSP性能有限,而且实际上很多情况下也不需要如此高的帧率,因此并不是所有采集到的图像数据都需要DSP进行处理(例如在视觉客流检测系统的实际应用中只要求每秒钟能处理5帧即可),但是必须保证DSF进行处理的图像为一幅完整的图像。可以利用OV7141的3个输出信号来完成这个功能,分别是PCLK(像素时钟信号)、VSYNC(场同步信号)和HREF(行有效信号)。并且OV7141可通过改变片内控制寄存器的值来调整输出图像的窗口大小,窗口可在4×2到652×482像素之间任意选择。HREF、只在所选择窗口内的像素信号输出时才置高电平,这使得图像的非完整模式下的处理也变为了可能。另外,0V7141的片内控制寄存器配置功能由SCCB总线实现,由于DSP不具有SCCB总线接口,因而为了通过DSP实现对0V7141的寄存器配置,利用DSP的2根数据线DO和D1借助CPLD实现sCcB总线时钟线SCL和数据线SDA的模拟以实现虚拟SCCB总线。

控制FIF0的信号主要是写信号和读信号,它们都由DSP根据FIF0的状态信号及DSP对图像的处理结果来控制对FIFO的读/写。读/写操作时序如图3所示。CM0s图像传感器采集获得的图像数据在CPLD控制下逐行写入FIFO,当FIFO的存储容量达到半满时,FIFO的半满标志位以外部中断方式通知DSP,DSP,检测到外部中断后开启DMA,利用DMA通道将FIFo中的图像数据搬移到DSP的片内图像缓冲区中。需要注意的是,在DMA从FIFO搬运图像数据的过程中CMOS图像传感器并没有停止向FIFO写入图像数据,由于CMOS写入FIFO速度Vw。比DMA从FIFO中读出数据的速度Vr慢(Vw=(1/2)Vr),使得CMOS和DMA在对FIFO进行双向访问时FIFO的实际存储容量始终保持在0和最大存储量之间,既不会上溢也不会下溢;从而保证一帧完整的图像可以被DMA控制器顺利的转移至DSP的片内图像缓冲区中。当一帧完整的图像搬运完成后,DMA会开启处理使能标志,当DSP发现处理使能标志开启后将从片内图像缓冲区中获得图像数据以完成图像处理算法,在DSP进行图像处理的同时,DMA控制器可以同时进行下一帧图像数据的搬移工作以提升系统的并行处理能力。DSP对于当前帧图像处理完成后将等待处理使能标志的再次开启以继续下一帧图像的处理。DSP对于当前帧图像的处理结果将在当前帧处理完成后采用以太网传输至接收终端。

此外,DMA在执行图像数据搬移功能时,为了保证数据搬移过程与DSP图像处理的并行性,通常需要在DSP片内开辟2块图像数据缓冲区。由于5416DSP片内DARAM在速度上优于SARAM,因而通常重要的程序代码以及算法的堆栈都放在DARAM中,为了节省DARAM资源并充分利用SARAM,在DSP程序空间所在的SARAM和数据空间所在的DARAM中各开辟1块作为图像数据缓冲区。SARAM中的缓冲区用于DMA通道0从FIF0中读取当前帧图像数据,DMA通道1从SARAM缓冲区中读取上一帧图像数据,两个DMA通道的数据搬移功能都可以在DSP完成某个子算法的过程中并行实现。

电子 DSP 嵌入式 机器人 视频监控 USB CMOS 传感器 IDT 电压 总线 MIPS CPLD LTE 红外 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 我国科学家人脸与笔迹识别领域获突破(04-29)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)