嵌入声纹特征的个人证件识读器

时间:09-15

来源:互联网

点击:

软件流程

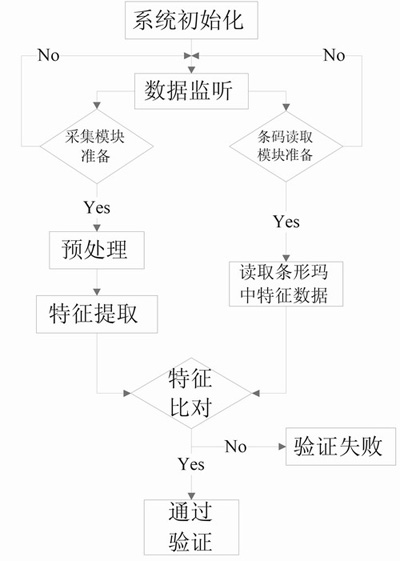

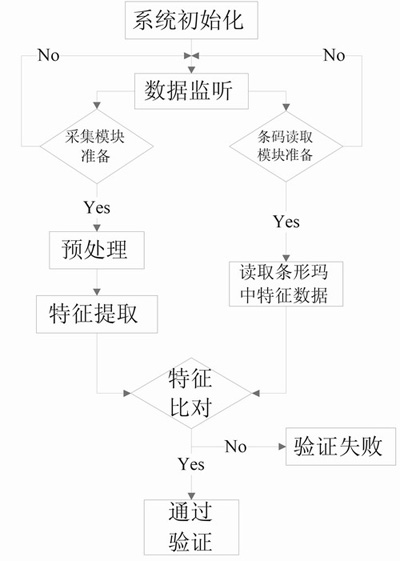

个人证件的验证流程如图3所示。验证分为两个基本过程,首先要读取条码中的数据,即用户登录;然后采集用户语音,即用户身份输入。经过特征比对,给出验证结果,由此可以说明用户现场所持证件是否属于其个人。

图3 验证过程软件流程图

C2H硬件加速

Nios II C2H加速器可以将ANSI C源程序代码转换成用户自定义的硬件加速模块。利用C2H工具,开发人员首先在Altera Nios II处理器中开发和调试C语言算法,而后将分析出的C程序瓶颈代码转换成硬件加速模块。硬件加速模块被挂到Avalon总线上,作为用户外设来使用。由此实现了从软件运行算法到硬件加速处理的转换过程。需要注意的是,并不是所有的C代码都可以转换成硬件加速模块。C2H编译器的特点如下:

①支持大部分的ANSI C代码和C语言结构,如指针、堆栈、结构体、全局和局部变量、循环、函数调用等;

②C2H编译器可以将C语言的语法成分映射为硬件结构,而且用户可以控制这些硬件加速结构;

③由于IDE6.0整合了C2H工具,用户无需学习新的开发环境;

④C2H可以利用SOPC Builder将加速好的硬件结构自动连接到Avalon总线上,无需用户手动处理;

⑤C2H可以产生硬件结构、资源利用率等详细报告。

本设计中规定用户采集语音的时长约为1s,内容为“你好”。在这样的条件下,利用计时器计算从预处理到给出识别结果的程序运行时间。系统时钟频率设置为50MHz。通过试验,得出运行时间约为5s,这显然不能满足实际需求。对实验结果进行分析,发现程序运行耗时主要集中在预处理和特征提取这部分,将其称为“前端”。经过分析前端的代码运行情况,设计师发现程序运行时间较长的主要原因是该部分包含了大量的矩阵运算和循环运算。下一步工作就是分析程序的运行瓶颈。经过分析研究发现,本设计算法中的瓶颈主要集中在加窗、FFT和DCT等部分,它们的耗时一般占到整个程序运行的60%以上。若将这些环节加速成功,性能将有较大提升。

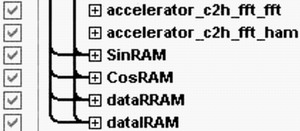

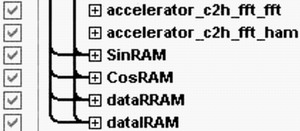

图4中显示了在SOPC Builder中向Avalon总线加载C2H加速器和片内RAM的情况。图中显示了两个加速器:accelerator_ c2h_fft_fft和 accelerator_ c2h_fft_ham,分别对应FFT和加窗(汉明窗)的硬件加速运算过程,SOPC Builder并没有为这两个模块分配基地址。图4中最下方的4个片内RAM可以起到数据缓存的作用。SinRAM与CosRAM为FFT加速运算提供正弦和余弦的查找表数据,dataRRAM与dataIRAM分别用于存储FFT运算后生成数据的实部和虚部。

图4 C2H加速器和添加的片内RAM

本设计中FFT采用256点的运算。软件FFT与硬件加速FFT计算时间的比较其中V1、V2、V3是设计中同一用户注册时的3段语音(内容相同)。通过表1可以看出,完全软件计算时,FFT耗时大约为2s;利用C2H工具加速后,耗时仅约为0.01s,提速效果良好。而后再将算法程序中其它环节进行加速,则设计的整体性能是可以满足实际需求的。因此,C2H对运行在SOPC系统上软件算法的加速处理是十分有效的。

结语

本文阐述了一种基于FPGA平台的应用设计实例,不仅能充分体现SOPC设计理念,而且与生物特征技术有机结合,发挥了二者的优势,具有广阔的应用前景。另外,本设计采用了Altera的C2H加速工具对软件算法进行硬件加速,实验结果表明利用这种方法进行设计效果明显。由于使用C2H工具对算法有一定的限制,因此某些情况下,用户自定义指令和用户外设仍然是不可或缺的设计方法。这几种设计手段的有机结合是FPGA设计的主要方向。

个人证件的验证流程如图3所示。验证分为两个基本过程,首先要读取条码中的数据,即用户登录;然后采集用户语音,即用户身份输入。经过特征比对,给出验证结果,由此可以说明用户现场所持证件是否属于其个人。

图3 验证过程软件流程图

C2H硬件加速

Nios II C2H加速器可以将ANSI C源程序代码转换成用户自定义的硬件加速模块。利用C2H工具,开发人员首先在Altera Nios II处理器中开发和调试C语言算法,而后将分析出的C程序瓶颈代码转换成硬件加速模块。硬件加速模块被挂到Avalon总线上,作为用户外设来使用。由此实现了从软件运行算法到硬件加速处理的转换过程。需要注意的是,并不是所有的C代码都可以转换成硬件加速模块。C2H编译器的特点如下:

①支持大部分的ANSI C代码和C语言结构,如指针、堆栈、结构体、全局和局部变量、循环、函数调用等;

②C2H编译器可以将C语言的语法成分映射为硬件结构,而且用户可以控制这些硬件加速结构;

③由于IDE6.0整合了C2H工具,用户无需学习新的开发环境;

④C2H可以利用SOPC Builder将加速好的硬件结构自动连接到Avalon总线上,无需用户手动处理;

⑤C2H可以产生硬件结构、资源利用率等详细报告。

本设计中规定用户采集语音的时长约为1s,内容为“你好”。在这样的条件下,利用计时器计算从预处理到给出识别结果的程序运行时间。系统时钟频率设置为50MHz。通过试验,得出运行时间约为5s,这显然不能满足实际需求。对实验结果进行分析,发现程序运行耗时主要集中在预处理和特征提取这部分,将其称为“前端”。经过分析前端的代码运行情况,设计师发现程序运行时间较长的主要原因是该部分包含了大量的矩阵运算和循环运算。下一步工作就是分析程序的运行瓶颈。经过分析研究发现,本设计算法中的瓶颈主要集中在加窗、FFT和DCT等部分,它们的耗时一般占到整个程序运行的60%以上。若将这些环节加速成功,性能将有较大提升。

图4中显示了在SOPC Builder中向Avalon总线加载C2H加速器和片内RAM的情况。图中显示了两个加速器:accelerator_ c2h_fft_fft和 accelerator_ c2h_fft_ham,分别对应FFT和加窗(汉明窗)的硬件加速运算过程,SOPC Builder并没有为这两个模块分配基地址。图4中最下方的4个片内RAM可以起到数据缓存的作用。SinRAM与CosRAM为FFT加速运算提供正弦和余弦的查找表数据,dataRRAM与dataIRAM分别用于存储FFT运算后生成数据的实部和虚部。

图4 C2H加速器和添加的片内RAM

本设计中FFT采用256点的运算。软件FFT与硬件加速FFT计算时间的比较其中V1、V2、V3是设计中同一用户注册时的3段语音(内容相同)。通过表1可以看出,完全软件计算时,FFT耗时大约为2s;利用C2H工具加速后,耗时仅约为0.01s,提速效果良好。而后再将算法程序中其它环节进行加速,则设计的整体性能是可以满足实际需求的。因此,C2H对运行在SOPC系统上软件算法的加速处理是十分有效的。

结语

本文阐述了一种基于FPGA平台的应用设计实例,不仅能充分体现SOPC设计理念,而且与生物特征技术有机结合,发挥了二者的优势,具有广阔的应用前景。另外,本设计采用了Altera的C2H加速工具对软件算法进行硬件加速,实验结果表明利用这种方法进行设计效果明显。由于使用C2H工具对算法有一定的限制,因此某些情况下,用户自定义指令和用户外设仍然是不可或缺的设计方法。这几种设计手段的有机结合是FPGA设计的主要方向。

嵌入式 SoC FPGA Altera Quartus 总线 LCD Verilog C语言 相关文章:

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 多核及虚拟化技术在工业和安全领域的应用(05-23)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于FPGA安全封装的身份认证模型研究(05-27)

- 基于nRF2401智能无线火灾监控系统设计(04-01)

- 智能视频多媒体技术的应用(05-31)