嵌入声纹特征的个人证件识读器

时间:09-15

来源:互联网

点击:

SOPC可编程片上系统是一种独特的嵌入式微处理系统。首先,它是SoC,即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,以FPGA为硬件基础,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件系统在线可编程的能力。

本系统采用了Altera公司的Cyclone II FPGA开发平台和相应的开发工具Quartus II进行系统硬件部分的开发;利用Nios II IDE实现了语音识别算法的编译、链接、调试和运行;同时还应用了Altera公司独具特色的C2H加速工具,实现了语音算法程序的硬件加速,使系统性能得到了明显的提升。

此次设计采用了二维条形码进行语音特征的存储,一方面是考虑到二维条形码的成本很低,市场应用潜力巨大;另一方面,正因为在个人证件上拥有了二维条形码,系统可以脱离数据库的支持,变得更加灵活实用。

系统结构

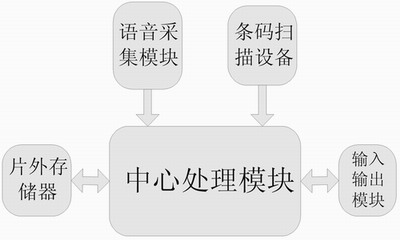

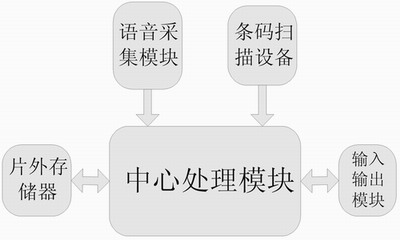

本设计采用SOPC的可编程设计思想,以Cyclone II中实现的Nios II处理器为核心,系统架构如图1所示。

图1 系统结构框图

中心处理模块可以接收其他模块的数据,并进行处理,再将处理结果送到外部设备进行显示和报告。语音采集模块在用户注册和认证时采集用户口令(即语音),其中包含A/D采样、量化、编码等,并会将数字形式的数据送到中心处理模块等待处理。系统以串口扫描枪做为条码扫描设备,用于读取个人证件上嵌入声纹特征的二维条形码中的数据,这些数据是在用户注册时生成的。

本设计将SOPC设计与二维条形码数据存储相结合,不仅发挥了各自的特点,而且扩宽了应用领域。

系统工作流程分为注册和验证两个阶段。注册过程需要采集同一用户的多个语音,通过注册算法生成个人的生物特征,将其嵌入到二维条码中,再打印条码到此用户的个人证件上。这样的证件具备了唯一、不易复制等特点,从而提高了证件的安全性能。对证件进行验证时,先用条码扫描设备读取条码中的特征数据,然后现场采集证件持有人的语音,进行比对,给出验证结果。

硬件的具体实现

本设计以32位Nios II软核处理器为系统的核心部分,负责执行指令和数据运算。各种IP都可以通过SOPC Builder连接到Avalon总线上,其中包含用户自定义的外设。用户外设的编写需要符合Avalon总线的规范。

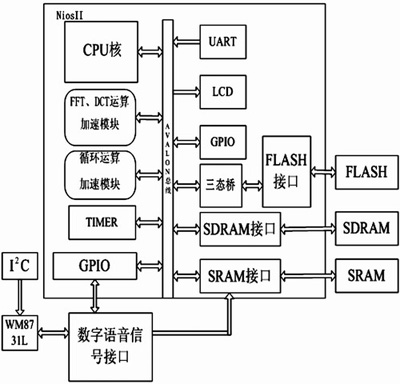

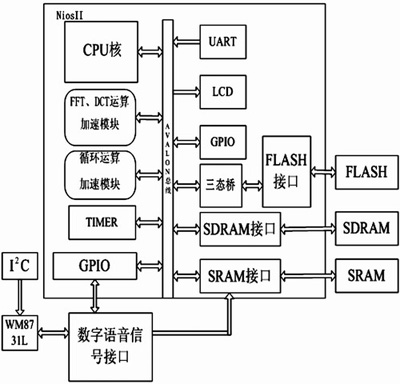

系统硬件结构如图2所示,包括CPU、UART、LCD、三态桥、片外存储器控制,以及各种输入/输出控制,这些IP都可以直接复用。这样的系统设计方法不仅模块化,而且大大缩短了系统设计周期。FFT运算模块不仅可以直接使用IP,还可以用C2H加速工具来提高系统性能。在此次设计中,FFT、DCT以及数据量较大的循环运算都采用C2H完成了硬件加速,效果较为明显。

图2 系统硬件结构

Nios II软核处理器

Nios II是32位软核处理器,具有较高的性能。本设计在Altera的Cyclone II上实现了处理器的配置,可以通过添加用户自定义指令来增强系统设计性能,同时可以添加多个片内存储器来提高数据的处理能力。

串口通信

本设计用到的扫描枪通过串口(UART)连接到开发平台上,目的是对二维条形码中包含语音特征的数据进行读取,通过Avalon总线将数据传送到相应的片外存储器中等待处理。

Timer

本设计利用SOPC Builder工具将两个Timer挂到Avalon总线上。其中一个设置为在IDE中运行C程序时的系统时钟,另外一个用作计时器。算法程序中设置了多个时间戳(Timestamp),相邻两个时间戳内程序段的运行时间可以用这两个时间戳的差值来表示。时间戳的设置对程序运行没有影响。设置计时器的最终目的是:将完全的软件实现与用C2H加速后的程序运行时间进行比较。

语音采集和语音报告验证结果

系统中,语音采集和语音报告验证结果部分均由Wolfson公司的WM8731L完成。WM8731L可以独立于Nios II软核处理器单独工作,其控制模块可按照I2C总线的时序编写。WM8731L内部含有A/D、D/A模块,同时具备较高的采样率和量化精度。本设计采用了8kHz的采样率,16位的量化精度。

在语音采集部分,由于A/D是串行数据输出,因此编写了串行到并行数据转换以及写SRAM控制的Verilog模块。语音报告结果部分通过GPIO与CPU进行数据、地址通信,将不同的语音按照不同的验证结果播放出来,这些语音的数据已经事先烧写进FLASH中。GPIO的控制可以通过Nios IDE来完成。类似地,播放语音部分由于从FLASH读出的数据是并行的,因此编写了并行到串行数据转换的Verilog模块。

加速模块

首先,在Nios IDE下运行算法C语言程序,利用计时器找出程序运行的瓶颈环节。而后对瓶颈部分利用C2H工具进行硬件加速,从而提高系统性能。这部分主要包括FFT运算加速和循环运算加速模块。

本系统采用了Altera公司的Cyclone II FPGA开发平台和相应的开发工具Quartus II进行系统硬件部分的开发;利用Nios II IDE实现了语音识别算法的编译、链接、调试和运行;同时还应用了Altera公司独具特色的C2H加速工具,实现了语音算法程序的硬件加速,使系统性能得到了明显的提升。

此次设计采用了二维条形码进行语音特征的存储,一方面是考虑到二维条形码的成本很低,市场应用潜力巨大;另一方面,正因为在个人证件上拥有了二维条形码,系统可以脱离数据库的支持,变得更加灵活实用。

系统结构

本设计采用SOPC的可编程设计思想,以Cyclone II中实现的Nios II处理器为核心,系统架构如图1所示。

图1 系统结构框图

中心处理模块可以接收其他模块的数据,并进行处理,再将处理结果送到外部设备进行显示和报告。语音采集模块在用户注册和认证时采集用户口令(即语音),其中包含A/D采样、量化、编码等,并会将数字形式的数据送到中心处理模块等待处理。系统以串口扫描枪做为条码扫描设备,用于读取个人证件上嵌入声纹特征的二维条形码中的数据,这些数据是在用户注册时生成的。

本设计将SOPC设计与二维条形码数据存储相结合,不仅发挥了各自的特点,而且扩宽了应用领域。

系统工作流程分为注册和验证两个阶段。注册过程需要采集同一用户的多个语音,通过注册算法生成个人的生物特征,将其嵌入到二维条码中,再打印条码到此用户的个人证件上。这样的证件具备了唯一、不易复制等特点,从而提高了证件的安全性能。对证件进行验证时,先用条码扫描设备读取条码中的特征数据,然后现场采集证件持有人的语音,进行比对,给出验证结果。

硬件的具体实现

本设计以32位Nios II软核处理器为系统的核心部分,负责执行指令和数据运算。各种IP都可以通过SOPC Builder连接到Avalon总线上,其中包含用户自定义的外设。用户外设的编写需要符合Avalon总线的规范。

系统硬件结构如图2所示,包括CPU、UART、LCD、三态桥、片外存储器控制,以及各种输入/输出控制,这些IP都可以直接复用。这样的系统设计方法不仅模块化,而且大大缩短了系统设计周期。FFT运算模块不仅可以直接使用IP,还可以用C2H加速工具来提高系统性能。在此次设计中,FFT、DCT以及数据量较大的循环运算都采用C2H完成了硬件加速,效果较为明显。

图2 系统硬件结构

Nios II软核处理器

Nios II是32位软核处理器,具有较高的性能。本设计在Altera的Cyclone II上实现了处理器的配置,可以通过添加用户自定义指令来增强系统设计性能,同时可以添加多个片内存储器来提高数据的处理能力。

串口通信

本设计用到的扫描枪通过串口(UART)连接到开发平台上,目的是对二维条形码中包含语音特征的数据进行读取,通过Avalon总线将数据传送到相应的片外存储器中等待处理。

Timer

本设计利用SOPC Builder工具将两个Timer挂到Avalon总线上。其中一个设置为在IDE中运行C程序时的系统时钟,另外一个用作计时器。算法程序中设置了多个时间戳(Timestamp),相邻两个时间戳内程序段的运行时间可以用这两个时间戳的差值来表示。时间戳的设置对程序运行没有影响。设置计时器的最终目的是:将完全的软件实现与用C2H加速后的程序运行时间进行比较。

语音采集和语音报告验证结果

系统中,语音采集和语音报告验证结果部分均由Wolfson公司的WM8731L完成。WM8731L可以独立于Nios II软核处理器单独工作,其控制模块可按照I2C总线的时序编写。WM8731L内部含有A/D、D/A模块,同时具备较高的采样率和量化精度。本设计采用了8kHz的采样率,16位的量化精度。

在语音采集部分,由于A/D是串行数据输出,因此编写了串行到并行数据转换以及写SRAM控制的Verilog模块。语音报告结果部分通过GPIO与CPU进行数据、地址通信,将不同的语音按照不同的验证结果播放出来,这些语音的数据已经事先烧写进FLASH中。GPIO的控制可以通过Nios IDE来完成。类似地,播放语音部分由于从FLASH读出的数据是并行的,因此编写了并行到串行数据转换的Verilog模块。

加速模块

首先,在Nios IDE下运行算法C语言程序,利用计时器找出程序运行的瓶颈环节。而后对瓶颈部分利用C2H工具进行硬件加速,从而提高系统性能。这部分主要包括FFT运算加速和循环运算加速模块。

嵌入式 SoC FPGA Altera Quartus 总线 LCD Verilog C语言 相关文章:

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 多核及虚拟化技术在工业和安全领域的应用(05-23)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于FPGA安全封装的身份认证模型研究(05-27)

- 基于nRF2401智能无线火灾监控系统设计(04-01)

- 智能视频多媒体技术的应用(05-31)