级联PLL超低噪声精密时钟抖动滤除技术研究

时间:09-01

来源:收集整理

点击:

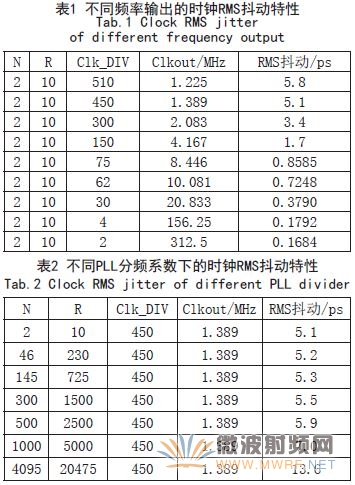

逐渐减小,当频率为312.5MHz时,抖动为168.4fs,而用与提供基准的参考时钟的0.5pf相比有了极大的提高与改进。表2为不同分频系数下输出时钟RMS抖动情况,可以很明显得看到抖动随系数的增加在呈现指数的增长。

3.结论

由仿真和研究可知,双级联PLL架构时钟发生设计,在实现抖动滤除低于300fs的同时,亦可实现多路频率合成及极低相位噪声(RMS抖动低至1.8ps@10KHz~5MHz)。超低抖动、低功耗的时钟发生技术满足了信号路径设计的模数转换采样及时钟和信号保证条件,同时,此类设计也可以被应用于无线基站、微波通信和100GE数据通信领域等。

- 精密频率合成技术助力多通道频率合成器的应用(06-08)

- 采用PLL技术的合成频率源设计(08-27)

- 如何使用部分PLL创建调制波形(10-22)

- 如何设计并调试锁相环PLL(03-19)

- 微型高稳定锁相时钟频率源(08-28)