改进型CMOS电荷泵锁相环电路的应用设计

时间:08-10

来源:mwrf

点击:

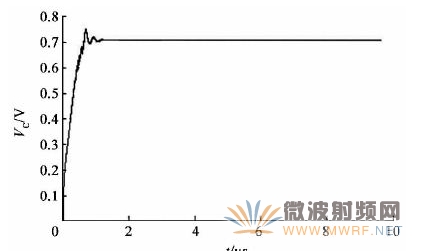

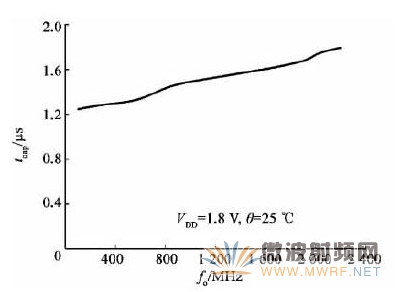

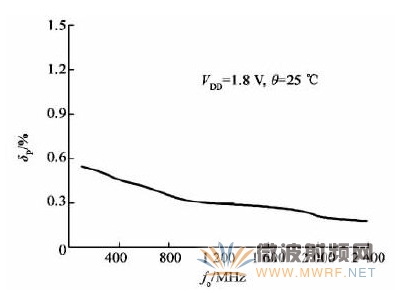

图10给出了锁相环建立过程的仿真波形,图中给出的是VCO控制电压的波形,在输入参考频率为31.5 MHz、频率反馈设置为32分频时,系统锁定时间约为1.5μs.MFC模块的采用和压控振荡器分段线性的处理有效扩展了锁频范围,输出频率在25 MHz~2.2 GHz内可调。在实际应用中,可以通过选择常用晶振频率和整数分频倍数获得更多的输出频率。图11和图12分别给出了输出频率在100 MHz~2.2 GHz变化时,锁相环的捕获时间tcap和稳态相对相位误差δp的变化曲线。结果表明,在100MHz~2.2GHz的输出频率范围内,锁相环的捕获时间小于2μs,相位相位误差小于0.6%.

图10 锁相环建立过程的瞬态仿真波形

图11 捕获时间(tcap)与输出频率的对应关系曲线

图12 稳态相对相位误差(δp)与输出频率的对应关系曲线

5、结论

在整个电荷泵锁相环系统中,电荷泵电路起着非常关键的作用。传统的电荷泵电路,其内部存在的一些非理想因素直接影响着整个环路的工作性能,如存在电荷泄漏、电流失配、电荷共享、时钟馈通等问题,会导致压控振荡器输出频率产生抖动和相位发生偏差。

本文设计的高性能CMOS电荷泵锁相环电路,通过对传统电荷泵电路的改进,提高了充放电电流的匹配性,有效抑制了锁相环输出的相位偏差,提高了环路的稳定性。同时在环路中增加了倍频控制模块MFC和压控振荡器分段处理,有效扩展了锁频范围。该电路基于Dongbu HiTek 0.18μm CMOS工艺设计,并进行了全面的仿真验证,结果表明:输出频率在100 MHz~2.2 GHz内变化时,频率锁定时间和相位误差都得到了有效控制,验证了设计的有效性。

CMOS 相关文章:

- 将RF信号转换为数字信号的CMOS转换器(12-10)

- 基于CMOS工艺的高性能射频滤波器:体声波滤波器BAW(12-15)