CMOS图像传感器中时问延迟积分的实现与优化

时间:08-02

来源:互联网

点击:

4 信噪比

积分器输出信噪比可以表示为

图26 其中Vsig为积分器输出信号

,Vnopa、Vnsc和Vnpixel分别为运放、开关电容电路和像素单元在积分器输出端的等效噪声。假设像素单元每次读m的信号是相等的,读出的噪声也是相等的,如果忽略运放和开关电容电路引入的噪声,则

即经n级TDI后输出信噪比为单级时的

倍,其中n为积分器的级数。对于CMOS电路,器件噪声是不可避免的,因此低噪声的电路设计是提高该电路信噪比的关键。

5 仿真结果

5.1 积分器仿真结果

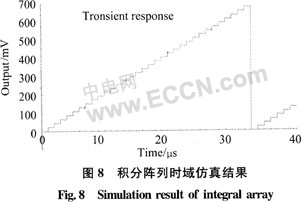

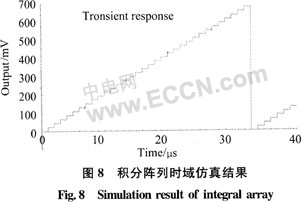

在标准CMOS工艺下,通过合理的时序关系,TPI电路可由积分阵列来实现。图8为-32级TDl电路的仿真结果,积分阵列对32行的像素信号进行积分累加,实现了TDI功能。

5.2 运算放大器仿真结果

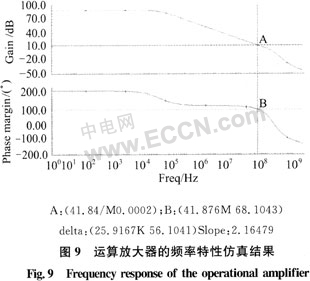

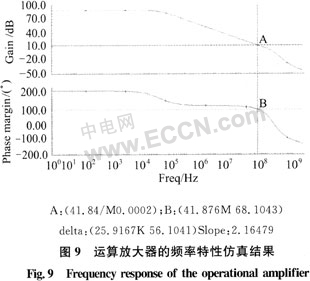

采用SMIC O.35μm CMOS工艺,本文设计的运放可以达到大约80 dH的直流增益,40 MHz的单位增益带宽,65°的相位裕度。图9为spectra仿真的运放频率特性区线。

5.3 积分器输出端噪声汇总

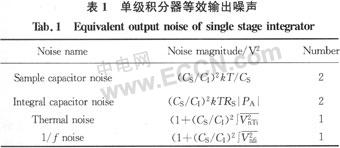

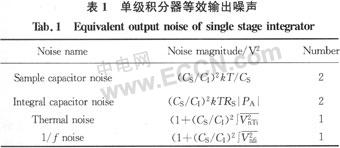

表1列出了单级积分器各部分产生的等效输出噪声,其中,VnTi、Vnfi为运算放大器等效输入的热噪声和1/f噪声。在带宽范围内对运放输入噪声谱密度进行积分,得到运放等效输入噪声,本设计运放带宽为40 MHz,积分得到运放等效输入噪声为36.1μV,乘以增益即得到运放器件噪声在积分器输出端的等效噪声,其余各部分噪声可以根据所选取的采样电容和积分电容值计算得到。

6 结 论

提出了在标准CMOS工艺下TDI电路的实现方法,并详细分析了电路的噪声,给出了器件级噪声的优化方法。采用SMIC 0.35μm工艺对电路进行了仿真验证,仿真结果表明,该电路能够实现TDI功能,并且具有低噪声特性。

积分器输出信噪比可以表示为

图26 其中Vsig为积分器输出信号

,Vnopa、Vnsc和Vnpixel分别为运放、开关电容电路和像素单元在积分器输出端的等效噪声。假设像素单元每次读m的信号是相等的,读出的噪声也是相等的,如果忽略运放和开关电容电路引入的噪声,则

即经n级TDI后输出信噪比为单级时的

倍,其中n为积分器的级数。对于CMOS电路,器件噪声是不可避免的,因此低噪声的电路设计是提高该电路信噪比的关键。

5 仿真结果

5.1 积分器仿真结果

在标准CMOS工艺下,通过合理的时序关系,TPI电路可由积分阵列来实现。图8为-32级TDl电路的仿真结果,积分阵列对32行的像素信号进行积分累加,实现了TDI功能。

5.2 运算放大器仿真结果

采用SMIC O.35μm CMOS工艺,本文设计的运放可以达到大约80 dH的直流增益,40 MHz的单位增益带宽,65°的相位裕度。图9为spectra仿真的运放频率特性区线。

5.3 积分器输出端噪声汇总

表1列出了单级积分器各部分产生的等效输出噪声,其中,VnTi、Vnfi为运算放大器等效输入的热噪声和1/f噪声。在带宽范围内对运放输入噪声谱密度进行积分,得到运放等效输入噪声,本设计运放带宽为40 MHz,积分得到运放等效输入噪声为36.1μV,乘以增益即得到运放器件噪声在积分器输出端的等效噪声,其余各部分噪声可以根据所选取的采样电容和积分电容值计算得到。

6 结 论

提出了在标准CMOS工艺下TDI电路的实现方法,并详细分析了电路的噪声,给出了器件级噪声的优化方法。采用SMIC 0.35μm工艺对电路进行了仿真验证,仿真结果表明,该电路能够实现TDI功能,并且具有低噪声特性。

电路 传感器 电压 集成电路 CMOS 电容 仿真 ADC 二极管 电阻 放大器 运算放大器 电流 电子 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 卫星电源分系统可靠性设计与研究(02-12)