高增益高线性度CMOS偶次谐波混频器设计

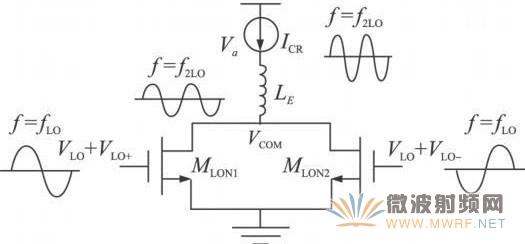

图3、倍频电路

1. 4、其他设计考虑

根据参考文献,我们在电路设计过程中做了以下考虑。从转换增益考虑,△VLO必须较小,而βRFN和βRFP必须较大。当βRFN和βRFP大到一定程度时,MRFN 和MRFP 将进入弱反型区,当MRFN和MRFP都处于弱反型区时,转换增益将会急速增加,但是同时,线性度将急剧恶化。幸运的是,我们可以通过增加LO 的功率来同时提高转换增益和线性度。

这与吉尔伯特混频器有所不同,对于吉尔伯特结构来说,增加LO功率只能使转换增益增加,但是线性度会恶化。所以在设计过程中,必须考虑使用适当的LO 功率和△VLO,电流复用对晶体管的尺寸和偏置要折中。我们可以设置偏置,使△VLO处于弱反型区来得到低功耗,同时从电流复用对上补偿线性度,并通过设置合适的LO功率得到适当的转换增益。

2、电路仿真

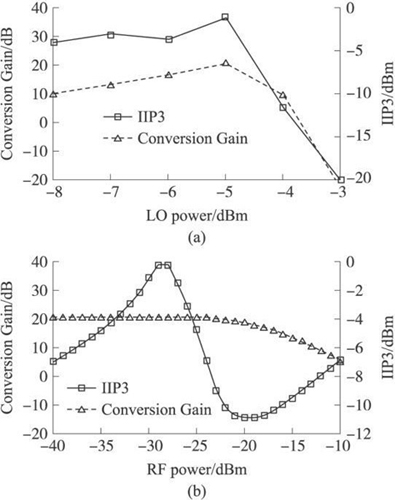

本文混频器电路设计基于SM IC0. 18 m 标准CMOS工艺库,运用ADS进行了仿真。混频器工作在1. 8 V 电源电压下,射频输入频率1. 575 GHz,功率为- 30 dBm;本振频率789. 5 MH z,功率为- 5 dBm。图4给出了转换增益和三阶交调截至点( IIP3)随本振信号功率和射频信号功率变化曲线。图4( a)显示了固定射频信号为- 30 dBm,本振信号功率为- 5 dBm时转换增益达最大为20. 848 dB;本振信号功率从- 8 dBm到- 5 dBm,IIP3缓慢增加到- 3 dBm,然后开始下降。图4 ( b) 显示了固定本振信号功率为- 5 dBm,转换增益在射频输入信号大于- 20 dBm 时开始下降,IIP3在- 11 dBm 到- 2. 297 dBm 波动。仿真结果显示,该混频器具有高增益、高线性度的优点。

图4、增益和IIP3随本振功率和射频功率变化的曲线

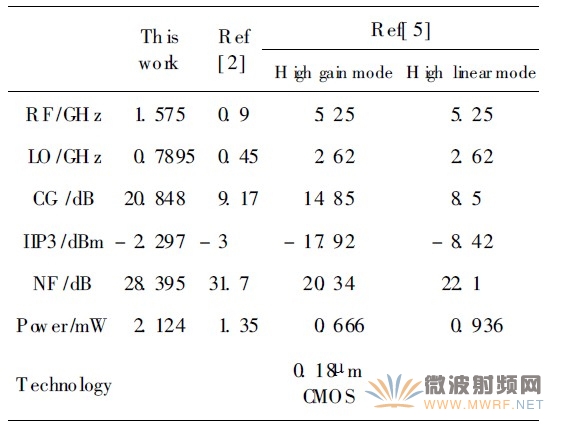

表1给出了本设计的仿真结果与近期发表的论文中混频器电路结果的比较,可以看到,该混频器电路在转换增益和线性度上具有一定的优势。

表1、混频器性能总结与比较

设计的混频器版图用C adence进行了绘制,如图5所示。面积为0. 751mm 0. 88mm。

图5、混频器版图设计

3、总结

本文采用电流复用和偶次谐波技术设计了CMOS偶次谐波混频器,经过对电路优化设计,仿真结果表明,该拓扑结构具有高转换增益、高线性度、低功耗的优点,在便携式无线通信系统中具有较好的应用前景。

混频器 相关文章:

- 高速通信领域的混频器和调制器分析(06-27)

- 高输入IP3混频器实现坚固型VHF接收器的设计要点(05-30)

- 低失真有源混频器AD831的工作原理及应用(08-28)

- 宽带镜频抑制混频器设计及实现(02-25)

- 通过微波混频器实现频率转换(05-03)

- 采用CMRC结构的Ka波段 四次谐波混频器设计(07-28)