CMOS触发器在CP边沿的工作特性研究

时间:06-18

来源:互联网

点击:

|

2.3.2 在CP下降沿的工作特性

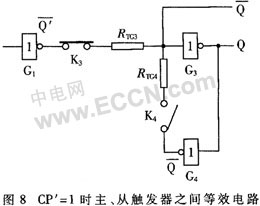

在CP′=1,CP′=0时,TG3导通,TG4截止,主、从触发器之间工作的等效电路如图8所示。这时G4的输出总是等于G3的输入,即截止的传输门TG4输出端与输入端之间的信号相等。所以在CP下降沿,传输门TG4开始导通(图中K4闭合)时,会使G3的输出锁定,而TG3的继续导通对输出不产生影响。这就是说,在CP下降沿,传输门的共同导通状态不会引起触发器输出状态的异常变化。

|

2.3.3 触发器对CP边沿时间的要求

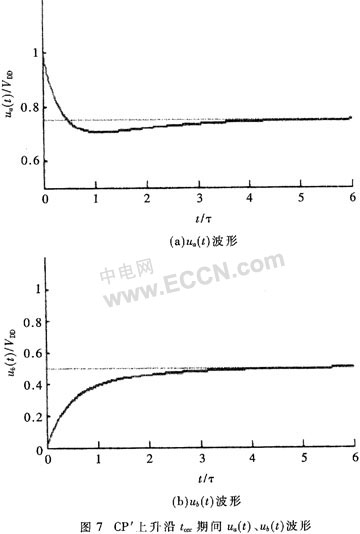

要使触发器在CP上升沿不出现异变现象,则要求G3的输入电压ub(t)变化到转换区之前,传输门TG4必须截止。测试表明,转换区电压△V=(0.01~0.05)VDD,这就要求ub(t)变化到稳态值0.5VDD的95%~99%之前,传输门共同导通时间结束,TG4截止。在式(4)ub(t)表达式中,第二项指数函数的时间常数比第三项小得多,故在ub(t)趋向转换区时,其变化规律主要由第三项指数函数的时剧常数1.39T决定。所以要求传输门的共同导通时间tonr为:

|

本实验测得tr应小于010.2μs,理论计算与实验测试取得了比较吻合的结果。

对于有效触发沿是CP下降沿的CNOS触发器,同样分析可得要求CP下降时间tf为:

|

3 结论与说明

(1) CMOS触发器在CP边沿会出现传输门共同导通的工作状态,这种工作状态会导致触发器在CP有效触发沿产生输出状态振荡的异变现象。

(2) 为了使触发器在CP触发沿不产生异变现象,保证其正常的工作状态,应对CP触发沿提出时间要求,它除与器件自身参数有关外,还与工作电源电压VDD有关,式(8)、式(9)表明了这种关系。

(3) 触发器在CP信号无效触发沿不会出现输出状态的异变现象,从这个角度讲,对CP信号无效触发沿不存在时间要求,但CP边沿时间大,电路的功耗也大,所以也应同样加以限制。

- 卫星电源分系统可靠性设计与研究(02-12)

- 新型锁相环芯片全面提升红外无线麦克风产品性能(05-04)

- 基于EPA与IEEE802.15.4两用手抄器的设计(06-01)

- 提高实时系统数据采集质量的研究(04-09)

- ARM在数字化远程视频监控系统的应用(05-20)

- 2009视频监控:网络化及其推动的几大趋势(06-03)