基于ARM的嵌入式安防系统

时间:04-28

来源:互联网

点击:

1 引言

随着社会经济的发展和人民生活水平的不断提高.同时引发入室抢劫、盗窃等暴力事件频频发生.不法分子的作案手段也是越来越向高科技化、高智能化发展。同时,智能家居内部的安防系统通常价格不低.因此必须有一种价格适中且工作稳定的智能安防系统来最大限度的减小损失。本文主要针对前述现象设计基于ARM技术的智能安防系统,该系统主要采用ARM系列芯片中的LPC2210嵌入式微处理器.选用可同时处理多任务的ucos-Ⅱ操作系统。

2 系统的总体设计方案

系统的总体设计体系图如图1所示.本系统主要由物业管理中心机、公用电话网、以太网、RS485网、室内嵌入式安防控制器、报警检测和可视对讲设备组成。其中485网构成室内网络,以太网和公用电话网构成外部通信网。整个系统分防盗、防灾报警和可视对讲三大部分。其中防盗部分主要防盗报警、紧急呼救系统等;防灾部分主要包括防火灾发生、防煤气(可燃气体)泄露。系统一旦有任何异常情况发生,则通过485网将预先设计好的指令发送到嵌入式安防控制器上,控制器对接收到的指令进行解析同时自身发出警戒信号然后可以通过公用电话网远程报警给用户,也可以通过以太网远程报警给物管中心报警.同时物业管理中心的主机将会记录下这些信息;可视对讲部分包括门口机、电控门、监视、监听设备等,主要完成对来访客人的身份确认和电控门的控制,以及与小区对讲主机、小区大门对讲主机进行对讲等功能。

图1 系统总体设计体系图

3 系统的硬件设计

LPC2210是基于支持实时仿真和嵌入式跟踪的16/32位ARM7TDMI-STM CPU.并带有16kB嵌入式RAM,1个128位宽度的外部存储器接口和1个独特的加速器架构,使得32位代码可在最大时钟频率下运行。同时,对代码规模有严格控制的应用.可选用16位Thumb TM模式和32位的ARM模式,ThumbTM下可减少代码30%,而性能的损失却很小。系统的结构图如图2所示。

图2 系统结构框图

3.1 系统时钟与复位电路

系统时钟使用11Mhz基准品振,连接LPC2100的X1和X2管脚。由于ARM芯片的高速、低功耗、低电压导致其噪声容限低。对电源的纹波、瞬态响应性能等方面要求更高,本系统采用带I2C存储器的电源监控芯片GAT1025JI-30以提高系统的可靠性。

3.2 JTAG接口电路与存储器接口电路

采用ARM公司提供的标准20脚JTAG防真调试接口。本系统扩展了2MB的NOR FLASH(SST39VF160)、8MBPSRAM(MT45W4MW 16)、16MB的NAND FLASH(K9F2808UOC)与一片带I2C的E2PROM存储器(CAT1025)。

3.3 LED与A/D接口

分别采用P2.28-P2.33作为前端探测器的信号指示,其中亮表示有警情,否则,灯灭。LPC2210具有4路lO位的A/D转换器.其参考电压为3.3V。

3.4 以太网接口电路

本系统设计以RTL8019AS芯片为核心的以太网接口电路.以16位总线的方式对RTL8019AS进行访问.

3.5 电话接口电路

选用接收发送集成芯片MT8880.MT8880是MITEL公司推出的DTMF发送接收器,分为振铃检测与模拟摘机电路、双音多频接收与发送电路.

3.6 485接口电路

通过LPC2210的UART口实现,具体电路如图3。在系统中选用SP3485来扩展RS485电路.SP3485是+3.3v低功耗半双工收发器件,完全满足RS 485标准的要求。这一芯片与SP485管脚完全兼容,并同时满足工业标准。SP3485的RE与DE脚与LPC2214的P0.10连接。当P0.10管脚为高电平时允许DI脚上的数据发送,DI脚与LPC2214的UARTI输出脚P0.8TXD连接。当P0.10管脚为低电平时.允许RD脚读取485线上的数据。RD脚与LPC2214的UARTI输入脚P0.9RXD连接。图中两个电阻R3、R4为偏置电阻.用于保证无连接的SP485芯片处于空闲状态,提供网络失效保护,以提高RS485节点与网络的可靠性。DWl、DW2是用来保护RS485总线的,避免RS485总线在受外界干扰时(雷击、浪涌)产生的高压,损坏RS485收发器。

图3 485接口电路

4 系统软件设计

本系统的软件设计主要包括ARM的应用程序设计和ucos-Ⅱ操作系统的移值。ARM的应用程序按照系统所要实现的功能。整个系统被划分为几个并行存在的任务,主要包括报警检测、电话报警、LED显示、485应用程序等,应用程序采用ANSI C语言编写。由于占先式操作系统埘任务的调度是按优先权的高低进行的,将系统的所有任务按其优先级从高到低顺序排列依次是:报警检测、LED显示、通信、数据分析等,由于多个任务可能会出现对共享资源的同时操作。从而造成数据的破坏或丢失,为了防止数据的破坏或丢失,出现使用信息出现互斥操作现

图4 系统主流程图

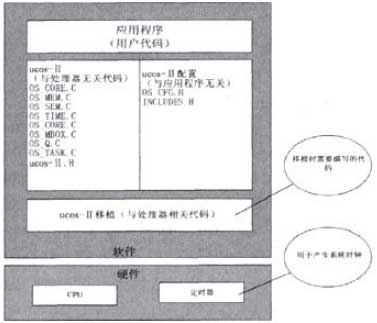

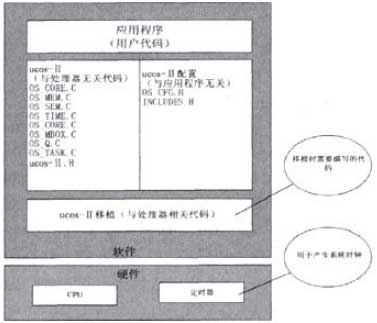

ucos-Ⅱ操作系统主要是协调LPC2210对程序的任务管理和调度.ucos-Ⅱ是源码公开的著名实时内核。是一个完整的、可移植的、可固化、可裁剪的占先式实时多任务内核,主要使用ANSI C语言编写程序,使用ADS编译和调试程序。操作系统的移植既是使实时内核在其他的微处理器或微控制器卜运行。因为ucos-Ⅱ大部分代码是用C语言编写的,所以其移植性较好,但是部分代码是用汇编编写的。ucos-Ⅱ的结构及与硬件的关系图见图5。

ucos-Ⅱ的移植需要满足下面五个条件:

* 处理器的C编译器能产生可重入型代码。

* 用c语言就可以打开和关闭中断。

* 处理器支持中断。并且能产生定时中断(通常在10至100Hz之M)。

* 处理器支持能够容纳一定量数据(可能是几千字节)的硬件堆栈。

* 处理器有将堆栈指针和其它CPU寄存器读出和存储到堆栈或内存中的指令。

ucos-Ⅱ的移植工作。主要与三个文件相关:处理器相关c文件(OS_CPU.H,os_CPU C.C)和汇编文件(OS_CPU_A.s)文件,其中在OS_CPU.H中需要针对处理器的字长重新定义一系列数据类型、设置常量来标志堆栈增长方向及声明用于开关中断和任务切换的宏。在OS_CPU C.C中需要对任务堆栈初始化,主要涉及到任务初始化时的一个堆栈设计,也就是在堆栈增长方向上如何定义每个需要保存的寄存器位置。OS_CPU_A.S主要涉及4个汇编语言.其中函数OSStartHighRdy()在OSStart()多任务启动之后.负责从最高优先级任务的TCB控制块中获得该任务的堆栈指针sp,通过sp依次将CPU现场恢复,这时系统就将控制权交给用户创建的该任务进程,直到该任务被阻塞或者被其他更高优先级的任务抢占;OSCtxsw()实现任务级的任务切换,它是当任务因为被阻塞而主动请求CPU调度时被执行.由于此时的任务切换都是在非异常模式下进行的,因此区别于中断级别的任务切换,它的工作是先将当前任务的cpu现场保存到该任务堆栈中然后获得最高优先级任务的堆栈指针,从该堆栈中恢复此任务的CPU现场.使之继续执行。这样就完成了一次任务切换;OSIntCtxSw()实现中断级的任务切换.它是在时钟中断ISR(中断服务例程)中发现有高优先级任务等待的时钟信号到来,则需要在中断退出后并不返回被中断任务.而是直接调度就绪的高优先级任务执行。这样做的目的主要是能够尽快地让高优先级的任务得到响应,保证系统的实时性能;OSTicklSR()是时钟中断处理函数,它的主要任务是负责处理时钟中断,调用系统实现的OSTimeTick函数,如果有等待时钟信号的高优先级任务,则需要在中断级别上调度其执行。完成上述工作以后,UCOS一Ⅱ就可以正常运行在ARM处理器了。

图5 ucos-Ⅱ的结构及与硬件的关系图

随着社会经济的发展和人民生活水平的不断提高.同时引发入室抢劫、盗窃等暴力事件频频发生.不法分子的作案手段也是越来越向高科技化、高智能化发展。同时,智能家居内部的安防系统通常价格不低.因此必须有一种价格适中且工作稳定的智能安防系统来最大限度的减小损失。本文主要针对前述现象设计基于ARM技术的智能安防系统,该系统主要采用ARM系列芯片中的LPC2210嵌入式微处理器.选用可同时处理多任务的ucos-Ⅱ操作系统。

2 系统的总体设计方案

系统的总体设计体系图如图1所示.本系统主要由物业管理中心机、公用电话网、以太网、RS485网、室内嵌入式安防控制器、报警检测和可视对讲设备组成。其中485网构成室内网络,以太网和公用电话网构成外部通信网。整个系统分防盗、防灾报警和可视对讲三大部分。其中防盗部分主要防盗报警、紧急呼救系统等;防灾部分主要包括防火灾发生、防煤气(可燃气体)泄露。系统一旦有任何异常情况发生,则通过485网将预先设计好的指令发送到嵌入式安防控制器上,控制器对接收到的指令进行解析同时自身发出警戒信号然后可以通过公用电话网远程报警给用户,也可以通过以太网远程报警给物管中心报警.同时物业管理中心的主机将会记录下这些信息;可视对讲部分包括门口机、电控门、监视、监听设备等,主要完成对来访客人的身份确认和电控门的控制,以及与小区对讲主机、小区大门对讲主机进行对讲等功能。

图1 系统总体设计体系图

3 系统的硬件设计

LPC2210是基于支持实时仿真和嵌入式跟踪的16/32位ARM7TDMI-STM CPU.并带有16kB嵌入式RAM,1个128位宽度的外部存储器接口和1个独特的加速器架构,使得32位代码可在最大时钟频率下运行。同时,对代码规模有严格控制的应用.可选用16位Thumb TM模式和32位的ARM模式,ThumbTM下可减少代码30%,而性能的损失却很小。系统的结构图如图2所示。

图2 系统结构框图

3.1 系统时钟与复位电路

系统时钟使用11Mhz基准品振,连接LPC2100的X1和X2管脚。由于ARM芯片的高速、低功耗、低电压导致其噪声容限低。对电源的纹波、瞬态响应性能等方面要求更高,本系统采用带I2C存储器的电源监控芯片GAT1025JI-30以提高系统的可靠性。

3.2 JTAG接口电路与存储器接口电路

采用ARM公司提供的标准20脚JTAG防真调试接口。本系统扩展了2MB的NOR FLASH(SST39VF160)、8MBPSRAM(MT45W4MW 16)、16MB的NAND FLASH(K9F2808UOC)与一片带I2C的E2PROM存储器(CAT1025)。

3.3 LED与A/D接口

分别采用P2.28-P2.33作为前端探测器的信号指示,其中亮表示有警情,否则,灯灭。LPC2210具有4路lO位的A/D转换器.其参考电压为3.3V。

3.4 以太网接口电路

本系统设计以RTL8019AS芯片为核心的以太网接口电路.以16位总线的方式对RTL8019AS进行访问.

3.5 电话接口电路

选用接收发送集成芯片MT8880.MT8880是MITEL公司推出的DTMF发送接收器,分为振铃检测与模拟摘机电路、双音多频接收与发送电路.

3.6 485接口电路

通过LPC2210的UART口实现,具体电路如图3。在系统中选用SP3485来扩展RS485电路.SP3485是+3.3v低功耗半双工收发器件,完全满足RS 485标准的要求。这一芯片与SP485管脚完全兼容,并同时满足工业标准。SP3485的RE与DE脚与LPC2214的P0.10连接。当P0.10管脚为高电平时允许DI脚上的数据发送,DI脚与LPC2214的UARTI输出脚P0.8TXD连接。当P0.10管脚为低电平时.允许RD脚读取485线上的数据。RD脚与LPC2214的UARTI输入脚P0.9RXD连接。图中两个电阻R3、R4为偏置电阻.用于保证无连接的SP485芯片处于空闲状态,提供网络失效保护,以提高RS485节点与网络的可靠性。DWl、DW2是用来保护RS485总线的,避免RS485总线在受外界干扰时(雷击、浪涌)产生的高压,损坏RS485收发器。

图3 485接口电路

4 系统软件设计

本系统的软件设计主要包括ARM的应用程序设计和ucos-Ⅱ操作系统的移值。ARM的应用程序按照系统所要实现的功能。整个系统被划分为几个并行存在的任务,主要包括报警检测、电话报警、LED显示、485应用程序等,应用程序采用ANSI C语言编写。由于占先式操作系统埘任务的调度是按优先权的高低进行的,将系统的所有任务按其优先级从高到低顺序排列依次是:报警检测、LED显示、通信、数据分析等,由于多个任务可能会出现对共享资源的同时操作。从而造成数据的破坏或丢失,为了防止数据的破坏或丢失,出现使用信息出现互斥操作现

图4 系统主流程图

ucos-Ⅱ操作系统主要是协调LPC2210对程序的任务管理和调度.ucos-Ⅱ是源码公开的著名实时内核。是一个完整的、可移植的、可固化、可裁剪的占先式实时多任务内核,主要使用ANSI C语言编写程序,使用ADS编译和调试程序。操作系统的移植既是使实时内核在其他的微处理器或微控制器卜运行。因为ucos-Ⅱ大部分代码是用C语言编写的,所以其移植性较好,但是部分代码是用汇编编写的。ucos-Ⅱ的结构及与硬件的关系图见图5。

ucos-Ⅱ的移植需要满足下面五个条件:

* 处理器的C编译器能产生可重入型代码。

* 用c语言就可以打开和关闭中断。

* 处理器支持中断。并且能产生定时中断(通常在10至100Hz之M)。

* 处理器支持能够容纳一定量数据(可能是几千字节)的硬件堆栈。

* 处理器有将堆栈指针和其它CPU寄存器读出和存储到堆栈或内存中的指令。

ucos-Ⅱ的移植工作。主要与三个文件相关:处理器相关c文件(OS_CPU.H,os_CPU C.C)和汇编文件(OS_CPU_A.s)文件,其中在OS_CPU.H中需要针对处理器的字长重新定义一系列数据类型、设置常量来标志堆栈增长方向及声明用于开关中断和任务切换的宏。在OS_CPU C.C中需要对任务堆栈初始化,主要涉及到任务初始化时的一个堆栈设计,也就是在堆栈增长方向上如何定义每个需要保存的寄存器位置。OS_CPU_A.S主要涉及4个汇编语言.其中函数OSStartHighRdy()在OSStart()多任务启动之后.负责从最高优先级任务的TCB控制块中获得该任务的堆栈指针sp,通过sp依次将CPU现场恢复,这时系统就将控制权交给用户创建的该任务进程,直到该任务被阻塞或者被其他更高优先级的任务抢占;OSCtxsw()实现任务级的任务切换,它是当任务因为被阻塞而主动请求CPU调度时被执行.由于此时的任务切换都是在非异常模式下进行的,因此区别于中断级别的任务切换,它的工作是先将当前任务的cpu现场保存到该任务堆栈中然后获得最高优先级任务的堆栈指针,从该堆栈中恢复此任务的CPU现场.使之继续执行。这样就完成了一次任务切换;OSIntCtxSw()实现中断级的任务切换.它是在时钟中断ISR(中断服务例程)中发现有高优先级任务等待的时钟信号到来,则需要在中断退出后并不返回被中断任务.而是直接调度就绪的高优先级任务执行。这样做的目的主要是能够尽快地让高优先级的任务得到响应,保证系统的实时性能;OSTicklSR()是时钟中断处理函数,它的主要任务是负责处理时钟中断,调用系统实现的OSTimeTick函数,如果有等待时钟信号的高优先级任务,则需要在中断级别上调度其执行。完成上述工作以后,UCOS一Ⅱ就可以正常运行在ARM处理器了。

图5 ucos-Ⅱ的结构及与硬件的关系图

ARM 嵌入式 仿真 电路 电压 LED 总线 收发器 电阻 C语言 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于EPA与IEEE802.15.4两用手抄器的设计(06-01)

- ARM在数字化远程视频监控系统的应用(05-20)

- FPGA在弹上信息处理机中的应用(04-15)