借助智能DAQ获得高级数据采集技术

时间:04-13

来源:互联网

点击:

同步

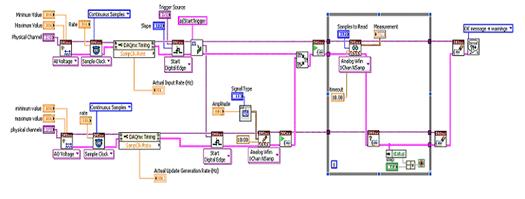

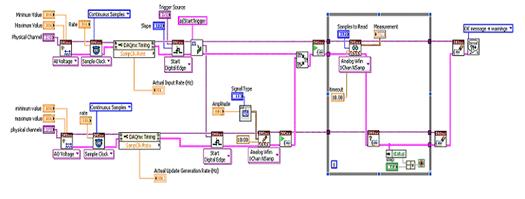

DAQmx驱动程序提供多种同步选择,帮助建立输入和输出的时间相关性。 在下方的程序框图中,模拟输入通道和模拟输出通道借助数字触发实现同步;过程中,需对模拟输入指定数字触发,并使用模拟输入的触发器信号触发产生模拟输出。

图7. 通过NI-DAQmx实现的同步模拟输入和输出

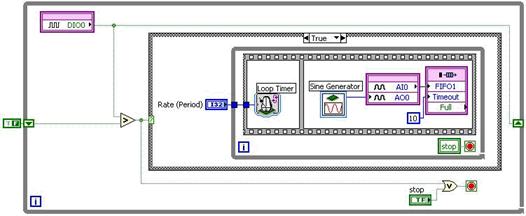

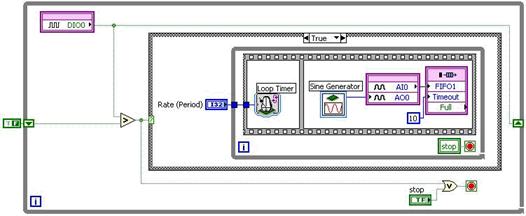

用户可通过智能DAQ硬件轻而易举地执行同步任务,而无需借助任务ID和板载信号路由。 本处即显示了NI LabVIEW FPGA中的内容。

图8. 通过智能DAQ实现的同步模拟输入和输出

此处,我们再次通过条件结构在FPGA芯片上执行硬件触发,而数字通道0上的上升沿则启用了真条件中的代码。 在顺序结构中,模拟输入与输出的节点在同时接受调用的过程中,几乎没有任何抖动;而我们只要简单地在各个独立的While循环内嵌入模拟I/O节点,即可 令其拥有独立的采样速率。 另外值得注意的是: 程序框图中显示的正弦发生器函数是1个Express VI,可帮助用户在查找表(LUT)中交互式地配置正弦值。

图8中的智能DAQ程序框图与图7中的DAQmx VI皆具有相同的功能,而唯有智能DAQ才能为自定义任务提供相应的灵活性。 举例为证:如需添加1个暂停触发,我们只消在内部While循环中添加1个条件结构,并通过另一个数字I/O节点选择真条件或假条件,即可轻松完成任务。 对硬件进行编程的强大功能,实现了各类I/O的定时与同步。

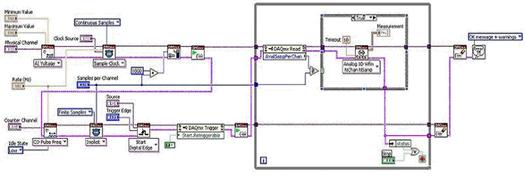

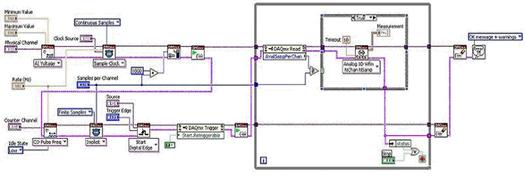

多功能同步的另一例证体现为:通过板载计数器产生有限脉冲并将计数器输出用作模拟输入的采样时钟。 该过程是进行可重触发式有限采样的常用手段。 下图显示了开展此类采集所必需的DAQmx代码。

图9. 通过NI-DAQmx实现的可重触发式有限模拟输入

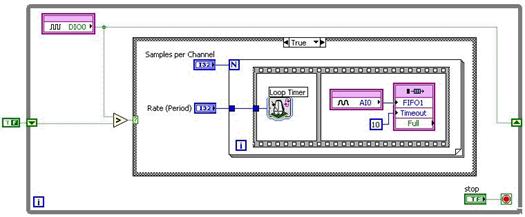

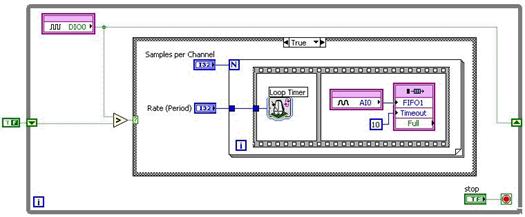

现在,让我们对下图内容和呈现相同功能的NI LabVIEW FPGA程序框图,加以比较。

图10. 通过智能DAQ和NI LabVIEW FPGA实现的可重触发式有限模拟输入

由于NI LabVIEW代码在硬件层运行,图10中的驱动配置步骤显然得到了极大精减。 我们已经借助简单的数字输入线和For循环结构,创建了硬件可重触发式有限采集。 图9中的程序框图使用2个板载计数器,创建出可重触发的有限脉冲序列;典型的多功能DAQ设备只有2个计数器。 而借助NI LabVIEW FPGA,智能DAQ硬件却能够将任意一条数字线配置成计数器。 我们将在之后的段落里,涉及更多“通过智能DAQ运行计数器/定时器”的内容。

我们能够借助由频率触发的采集,进一步地推进智能DAQ在硬件定时方面的灵活性特性。 用户可通过高速板载决策计算输入信号的频率,而后选择条件结构中所需的代码;这一点是使用典型多功能DAQ设备所无法企及的。 在多设备的同步进程中,智能DAQ还可提供用于PCI板卡的RTSI总线或是用于PXI模块的PXI触发总线。 这些外部定时和同步线还可通过程序框图上的I/O节点接受访问。

模拟波形的生成

不少多功能DAQ设备都配有模拟输出通道,能够为了生成连续的模拟波形而需要用到FIFO缓冲。 生成的波形可将FIFO用作循环缓冲区,且无需从主机处接受任何更新数据,即可连续不断地重新生成一系列的模拟值。 通信总线的有无对此影响不大,因为并没有针对设备的频繁数据读写。 而如果波形需要修改,就必须重新启动输出任务并向FIFO写入新数据。 另一个办法是向硬件FIFO设备连续读写数据,而这又会导致输出任务出现时滞。 借助智能DAQ,用户能够将波形输出结果存储于硬件,甚至能够通过硬件触发改变波形,进而创建任意波形发生器。

下方的函数发生器范例通过数字输入线,触发了输出波形中的改动。 通过组合数字I/O线0与1,我们取得了应用于模拟输出的4种不同状态或称条件。

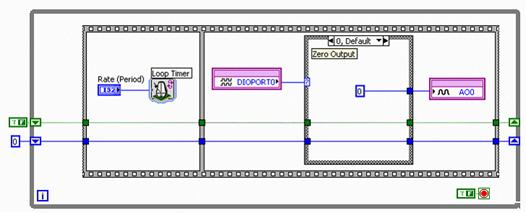

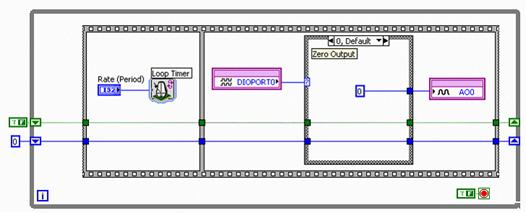

图11a. 配有智能DAQ条件0的函数发生器 – 零输出

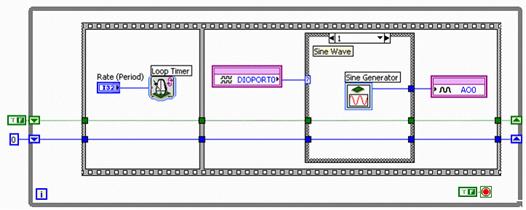

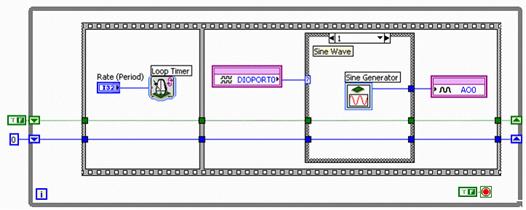

图11b. 配有智能DAQ条件1的函数发生器 – 正弦波

当两线皆呈现低电平时,执行条件0;如图11a所示,输出值为0 V常量。而当DIO线0呈现高电平而DIO线1呈现低电平时,条件1将在模拟输出0上执行并生成一个正弦波。用户可通过该正弦生成结构(图11b)中的正 弦发生器Express VI,配置NI LabVIEW FPGA必需的参数,交互地配置正弦波。

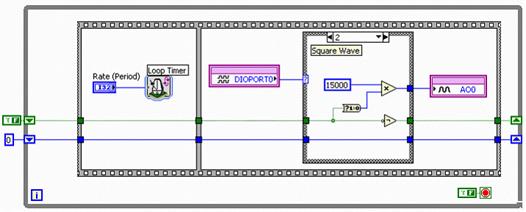

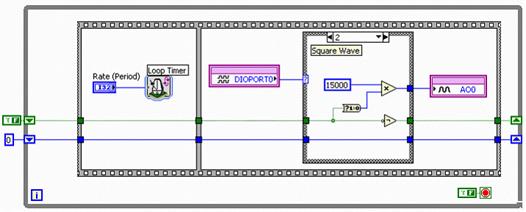

图11c. 配有智能DAQ条件2的函数发生器 – 方波

条件2(图11c)能够在While循环的每轮迭代中,轻松切换布尔值。 数值较低时,整数15000便被写入模拟输出AO0,以对应16位DAC内由输出寄存器存放的数值:15000。 16位有符号整数可以包含-32768到32767之间的数值。当输出电压范围介于-10 V和10 V时,向模拟输出AO0写入-32768会生成-10 V电压,而写入32767则生成10 V电压。该例中,因我们的写入值为15000,则生成的电压将低于5 V。(数学公式为: 15000/32767 * 10 V = 4.5778 V) 通常,条件2会输出一个在0 V和4.578 V之间变换的方波。

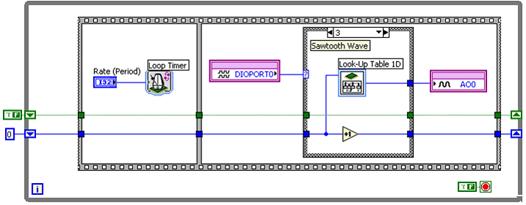

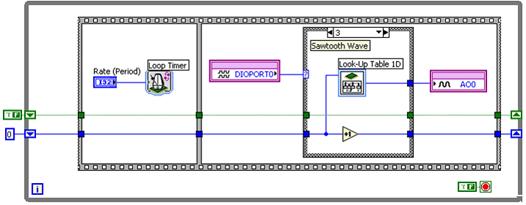

图11d. 配有智能DAQ条件3的函数发生器 – 锯齿波

当DIO 0和DIO 1均呈现高电平时,便执行最后一个条件(图11d);其间,须借助查找表(LUT)连续生成一个锯齿波。 作为另一类Express VI的查表VI,既能存储任意波形值,也能通过编程建立波形值的索引。 该例中,接受配置的锯齿波可在模拟输出通道0上生成。

通过将所有的值都存储在FPGA上,用户在降低总线依赖性的同时,也确保了波形更新时硬件定时的速度和可靠性。 之前各部分中所描述的模拟输入的触发和同步灵活性同样适用于模拟输出;借助智能DAQ,用户能够以不同速率,完全独立地更新各路模拟输出通道。 这意味着:用户可在不影响其他通道输出结果的前提下,修改单个周期性波形的频率。 请注意:大多数数据采集硬件均不具备此项功能。

DAQmx驱动程序提供多种同步选择,帮助建立输入和输出的时间相关性。 在下方的程序框图中,模拟输入通道和模拟输出通道借助数字触发实现同步;过程中,需对模拟输入指定数字触发,并使用模拟输入的触发器信号触发产生模拟输出。

图7. 通过NI-DAQmx实现的同步模拟输入和输出

用户可通过智能DAQ硬件轻而易举地执行同步任务,而无需借助任务ID和板载信号路由。 本处即显示了NI LabVIEW FPGA中的内容。

图8. 通过智能DAQ实现的同步模拟输入和输出

此处,我们再次通过条件结构在FPGA芯片上执行硬件触发,而数字通道0上的上升沿则启用了真条件中的代码。 在顺序结构中,模拟输入与输出的节点在同时接受调用的过程中,几乎没有任何抖动;而我们只要简单地在各个独立的While循环内嵌入模拟I/O节点,即可 令其拥有独立的采样速率。 另外值得注意的是: 程序框图中显示的正弦发生器函数是1个Express VI,可帮助用户在查找表(LUT)中交互式地配置正弦值。

图8中的智能DAQ程序框图与图7中的DAQmx VI皆具有相同的功能,而唯有智能DAQ才能为自定义任务提供相应的灵活性。 举例为证:如需添加1个暂停触发,我们只消在内部While循环中添加1个条件结构,并通过另一个数字I/O节点选择真条件或假条件,即可轻松完成任务。 对硬件进行编程的强大功能,实现了各类I/O的定时与同步。

多功能同步的另一例证体现为:通过板载计数器产生有限脉冲并将计数器输出用作模拟输入的采样时钟。 该过程是进行可重触发式有限采样的常用手段。 下图显示了开展此类采集所必需的DAQmx代码。

图9. 通过NI-DAQmx实现的可重触发式有限模拟输入

现在,让我们对下图内容和呈现相同功能的NI LabVIEW FPGA程序框图,加以比较。

图10. 通过智能DAQ和NI LabVIEW FPGA实现的可重触发式有限模拟输入

由于NI LabVIEW代码在硬件层运行,图10中的驱动配置步骤显然得到了极大精减。 我们已经借助简单的数字输入线和For循环结构,创建了硬件可重触发式有限采集。 图9中的程序框图使用2个板载计数器,创建出可重触发的有限脉冲序列;典型的多功能DAQ设备只有2个计数器。 而借助NI LabVIEW FPGA,智能DAQ硬件却能够将任意一条数字线配置成计数器。 我们将在之后的段落里,涉及更多“通过智能DAQ运行计数器/定时器”的内容。

我们能够借助由频率触发的采集,进一步地推进智能DAQ在硬件定时方面的灵活性特性。 用户可通过高速板载决策计算输入信号的频率,而后选择条件结构中所需的代码;这一点是使用典型多功能DAQ设备所无法企及的。 在多设备的同步进程中,智能DAQ还可提供用于PCI板卡的RTSI总线或是用于PXI模块的PXI触发总线。 这些外部定时和同步线还可通过程序框图上的I/O节点接受访问。

模拟波形的生成

不少多功能DAQ设备都配有模拟输出通道,能够为了生成连续的模拟波形而需要用到FIFO缓冲。 生成的波形可将FIFO用作循环缓冲区,且无需从主机处接受任何更新数据,即可连续不断地重新生成一系列的模拟值。 通信总线的有无对此影响不大,因为并没有针对设备的频繁数据读写。 而如果波形需要修改,就必须重新启动输出任务并向FIFO写入新数据。 另一个办法是向硬件FIFO设备连续读写数据,而这又会导致输出任务出现时滞。 借助智能DAQ,用户能够将波形输出结果存储于硬件,甚至能够通过硬件触发改变波形,进而创建任意波形发生器。

下方的函数发生器范例通过数字输入线,触发了输出波形中的改动。 通过组合数字I/O线0与1,我们取得了应用于模拟输出的4种不同状态或称条件。

图11a. 配有智能DAQ条件0的函数发生器 – 零输出

图11b. 配有智能DAQ条件1的函数发生器 – 正弦波

当两线皆呈现低电平时,执行条件0;如图11a所示,输出值为0 V常量。而当DIO线0呈现高电平而DIO线1呈现低电平时,条件1将在模拟输出0上执行并生成一个正弦波。用户可通过该正弦生成结构(图11b)中的正 弦发生器Express VI,配置NI LabVIEW FPGA必需的参数,交互地配置正弦波。

图11c. 配有智能DAQ条件2的函数发生器 – 方波

条件2(图11c)能够在While循环的每轮迭代中,轻松切换布尔值。 数值较低时,整数15000便被写入模拟输出AO0,以对应16位DAC内由输出寄存器存放的数值:15000。 16位有符号整数可以包含-32768到32767之间的数值。当输出电压范围介于-10 V和10 V时,向模拟输出AO0写入-32768会生成-10 V电压,而写入32767则生成10 V电压。该例中,因我们的写入值为15000,则生成的电压将低于5 V。(数学公式为: 15000/32767 * 10 V = 4.5778 V) 通常,条件2会输出一个在0 V和4.578 V之间变换的方波。

图11d. 配有智能DAQ条件3的函数发生器 – 锯齿波

当DIO 0和DIO 1均呈现高电平时,便执行最后一个条件(图11d);其间,须借助查找表(LUT)连续生成一个锯齿波。 作为另一类Express VI的查表VI,既能存储任意波形值,也能通过编程建立波形值的索引。 该例中,接受配置的锯齿波可在模拟输出通道0上生成。

通过将所有的值都存储在FPGA上,用户在降低总线依赖性的同时,也确保了波形更新时硬件定时的速度和可靠性。 之前各部分中所描述的模拟输入的触发和同步灵活性同样适用于模拟输出;借助智能DAQ,用户能够以不同速率,完全独立地更新各路模拟输出通道。 这意味着:用户可在不影响其他通道输出结果的前提下,修改单个周期性波形的频率。 请注意:大多数数据采集硬件均不具备此项功能。

FPGA LabVIEW VHDL ADC DAC 电压 总线 PXI 编码器 滤波器 相关文章:

- 基于FPGA安全封装的身份认证模型研究(05-27)

- ARM在数字化远程视频监控系统的应用(05-20)

- FPGA在弹上信息处理机中的应用(04-15)

- 如何充满信心地设计军用SDR产品(07-25)

- 关于安防应用中图像处理难点分析及处理器选择(07-14)

- 基于 SoPC 的震动信号采集设备设计(08-14)