基于TMS320C6416T的CPCI信号处理板设计

时间:12-01

来源:互联网

点击:

作者:中国电波传播研究所 高荣山 来源:电子设计应用2009年第11期

引言

CPCI规范是由PICMG制定的一种开放工业计算机标准,用于工业和嵌入式应用。CPCI系统背板和CPCI板卡采用标准的2mm高密度气密性针孔连接器,提高了系统可靠性。在电气、逻辑和软件功能等方面,其与PCI标准完全兼容,使得基于PCI技术的丰富软件工具同样可以在CPCI系统中使用。另外,CPCI可采用IEEE 1101.11后端输出方式,使系统维护更加便捷。

CPCI板卡的尺寸分3U(100mm×160mm)和6U(160mm×233mm)两种,3U系统只提供32位/64位的PCI系统总线,6U的系统除了提供32位/64位的PCI系统总线外,还通过连接器接口J3、J4、J5实现自定义总线,可用作高速数据通信或通用输入/输出线等,适用于数字化高速处理的模块化设计应用。

本文利用TMS320C6416T内部集成的32位、33MHz PCI主/从接口,给出了6U的CPCI信号处理板卡设计方案,并对其软件设计特别是DSP的二次引导程序做了说明。

硬件设计

CPCI板卡有J1~J5五个连接器接口,其中只有J1是必须有的,为32位PCI信号接口。J2为64位扩展PCI信号。对于主控板以外的CPCI板卡,J3、J4、J5可用作用户自定义接口。本文所设计的CPCI板卡使用J1、J4、J5接口,主要由DSP、FPGA、SDRAM、FLASH等组成。板卡以TMS320C6416T为核心,通过高性能FPGA实现AD数据采集后的预处理,然后经64位宽的EMIFA总线传入 TMS320C6416T中进行数字信号处理,处理数据可通过32位PCI总线、光收发器或CPCI自定义总线传输至外部设备。CPCI的J1接口为32 位、33M的PCI接口信号,与TMS320C6416T的PCI外设连接。DSP通过EMIFA的CE0存储空间连接4片SDRAM芯片 MT48LC32M16A2,扩展成64位宽度的128MB存储器,CE1、CE2空间连接FPGA,通过J4、J5扩展。EMIFB的CE1空间通过 FLASH芯片S29LV016D扩展2MB的FLASH,用于系统的自举。系统框图如图1所示。

图1 CPCI板卡框图

处理板通过高速16位ADC芯片LTC2206实现模数转换,然后将数据传输到FPGA进行数据预处理,包括数字下变频及缓存等,之后经64位EMIFA 总线通过EDMA传到DSP中进行数字信号处理,最后通过CPCI总线传输到主机。板卡通过带选择器的时钟分配器SY89464实现内外时钟的控制和单端时钟到差分时钟的转换。FPGA的配置芯片采用EPC16,配置方式为PS,EPC和FPGA通过JTAG链实现编程。

TMS320C6416T通过SDRAM扩展256MB存储空间,SDRAM采用512Mb芯片MT48LC32M16A2,位宽为16位,通过4个此芯片扩展为64位。

EMIFB的CE1空间通过FLASH扩展BOOTROM空间,采用FLASH芯片S29AL016D实现,S29AL016D有8位byte和16位word两种方式,通过引脚byte#设置,这里使用8位数据格式。

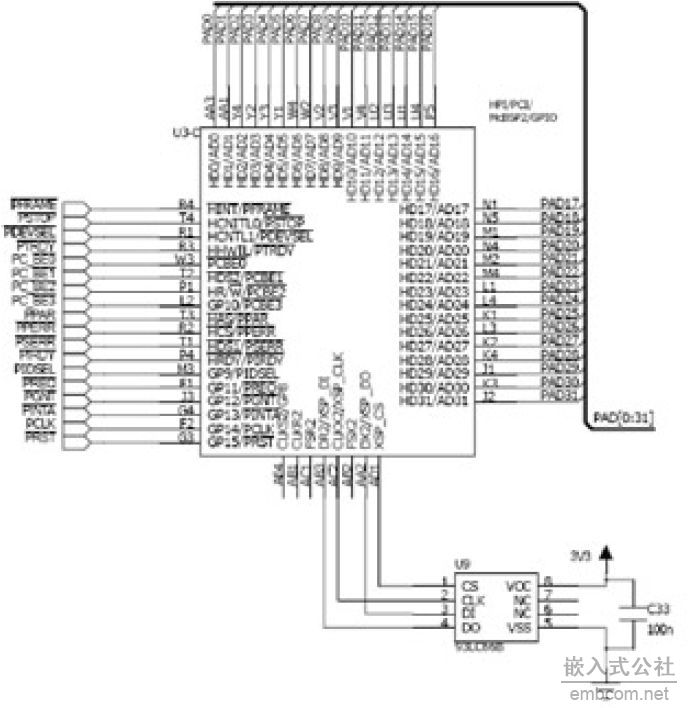

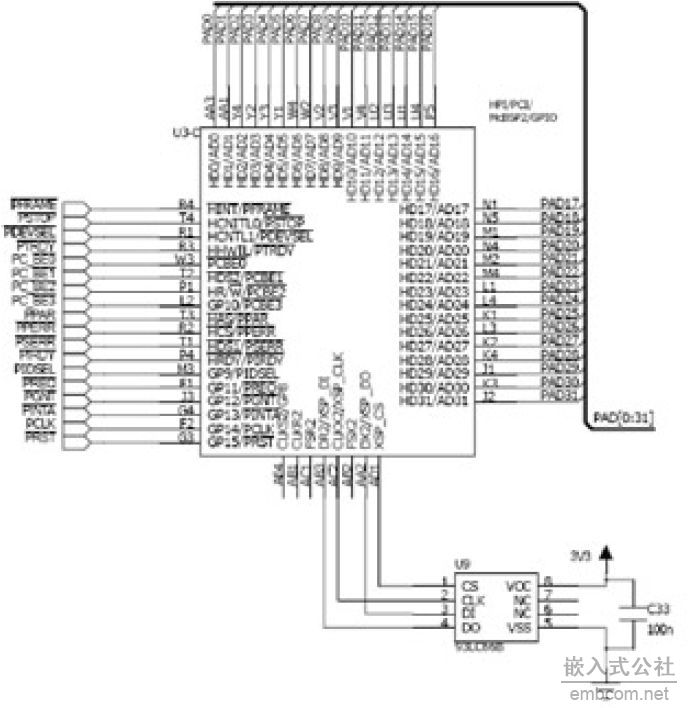

PCI接口信号的连接如图2所示,使能TMS320C6416T的PCI接口对应PCI_en引脚置高。该接口符合PCI 2.2规范,为33M、32位的PCI主/从接口。

图2 TMS320C6416T的PCI接口电路图

上电后DSP自动从4KB的EEPROM芯片93LC66B读取配置信息。DSP与上位机可通过EDMA进行数据传输。

这里,DSP的输入时钟采用50M晶振通过零延迟时钟缓冲分配器CY2308输出,DSP的EMIFA、EMIFB外接存储器时钟为100MHz,也通过晶体振荡器连接CY2308给出。

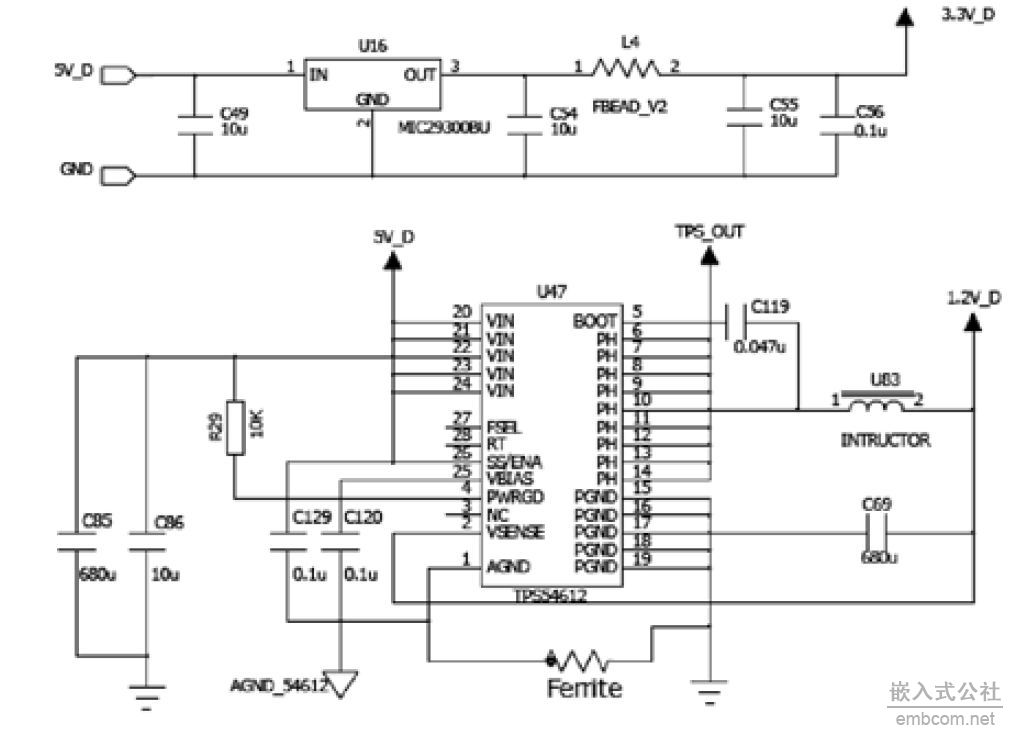

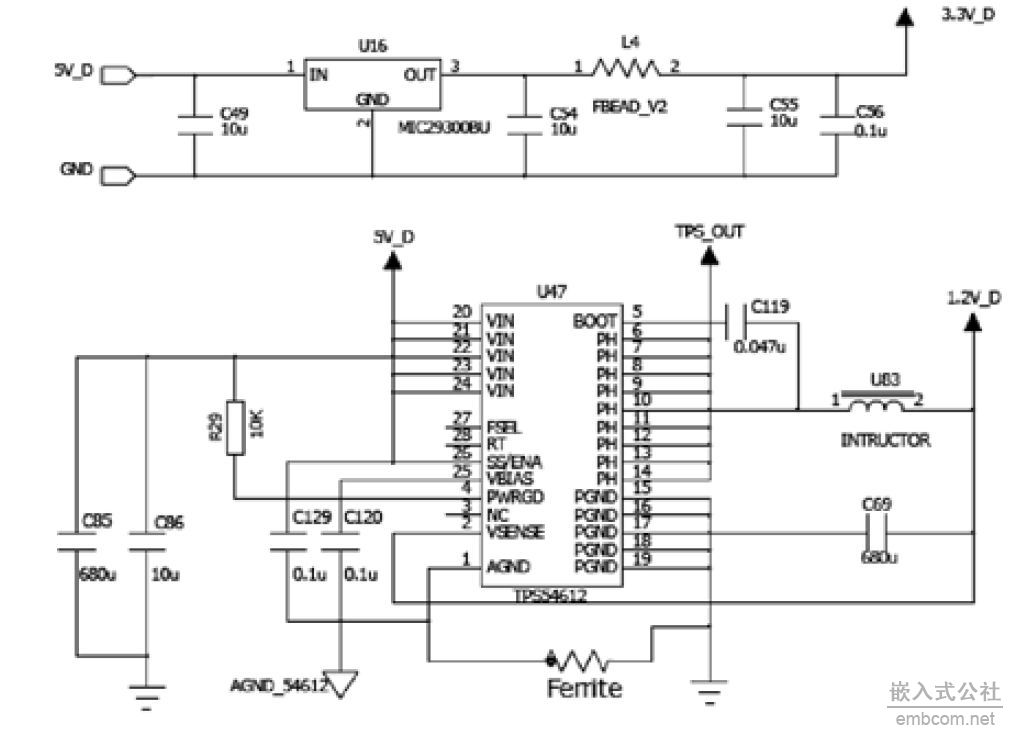

DSP和FPGA的核电压均为1.2V,I/O电压为3.3V,1.2V通过CPCI接口的5V电压经开关电源控制芯片TPS54612实现,3.3V经LDO芯片MIC29300实现。电路如图3所示。

图3 电源电路图

软件设计

板卡的软件设计包括DSP的Boot程序、上位机的驱动程序及信号处理板需要实现的专门算法程序。这里重点介绍TMS320C6416的二次Bootloader程序设计。

TMS320C6416T的程序加载方式有HPI、ROM、Noboot、JTAG等几种,通过上电时BEA[18:19]的值决定,板卡中可通过拨码开关进行设置。使用ROM加载可实现系统上电自动加载,其加载过程是:DSP内部Bootloader程序将保存于外部ROM(FLASH)中的前1K字节长度的程序自动搬到DSP内部RAM 0地址处,然后从0地址开始执行程序。由于应用程序一般都大于1K字节,所以必须用二次引导的方法。二次引导程序放在FLASH的前1K字节中,这样 DSP自动Boot完成后就从0地址开始执行二次引导程序。当所有的数据都搬运完毕后,DSP跳转到主程序的入口处,并开始执行主程序。为了实现这一引导过程,首先需要在验证好的算法程序工程文件中加入二次Boot的搬移文件,并修改CMD文件,通过CCS编译成out文件后,通过hex工具转换成.hex文件,再转变文件格式成bin二进制数据文件格式,最后通过另外的FLASH烧写工程文件写入到FLASH中。

TMS320C6416T只支持8位的ROM加载。ROM中的程序存储格式需要与芯片的大小端存储模式一致。

搬移文件Boot.asm采用汇编语言实现,实现1K代码的搬移。

CMD文件中应将Boot段分配为从地址0开始的1K空间,FLASH空间从0x64000000开始,长度也为1K,即分配为:

MEMORY

{

BOOT : origin = 0x00000000, len = 0x00000400

ISRAM : origin = 0x00000400, len = 0x000ffc00 ;DSP的内部L2空间

FLASH : origin = 0x64000000, len = 0x00000400

}

利用CCS经工程文件编译生成.out文件后,再利用其自带的Hex转换工具hex6x.exe转换成hex文件,转换时需要首先编写一个cmd命令文件, 说明需要转换的out文件名、存储器宽度、Flash起始地址和长度、hex输出文件名等。如cmd文件名为myHex_cmd,则调用格式为:

hex6x.exe myHex_Cmd.cmd

hex文件以行为单位。每行以字符 ‘:’ (0x3a)开头,以回车和换行符(0x0d、0x0a)为结束。每行开始和结束之间的所有内容都是以字符形式表现的。通过C程序将hex文件转换为 bin文件,在烧写FLASH的工程中以.h头文件保存定义为data数组。然后在CCS中通过FlashBurn的工程文件将data数据烧写到 FLASH中,即可实现DSP的上电自举。

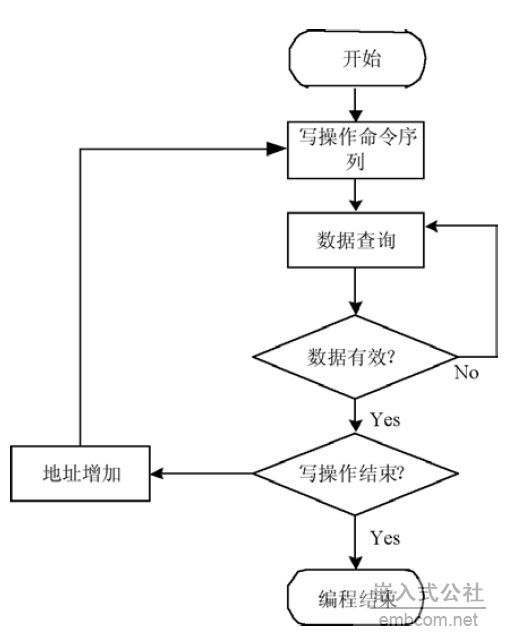

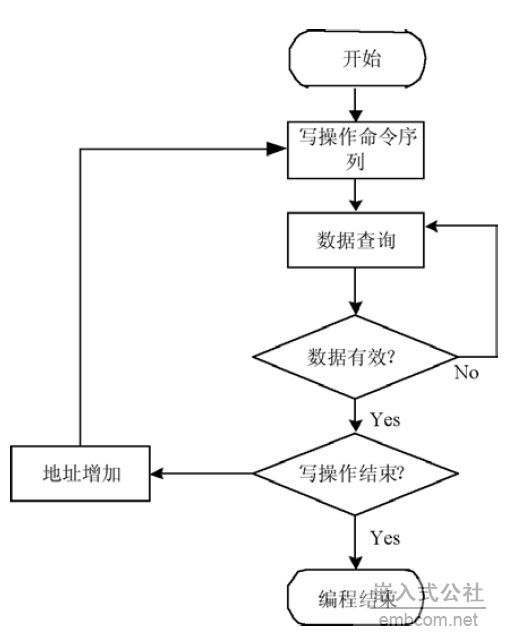

FlashBurn工程文件主要实现S29AL016D的编程。S29AL016D的编程流程图如图4所示。

图4 FLASH写操作流程图

按照S29AL016D的命令格式和程序流程,烧写FLASH子程序如下。其中,*data为要写入的数组,nByte为数据个数。

void BurnFlash(unsigned char *data, unsigned long nBytes)

{

unsigned short timeout;

unsigned char c;

while(nBytes--)

{

*(volatile char *)0x64000AAA = (char)0xaa;

*(volatile char *)0x64000555= (char)0x55;

*(volatile char *)0x64000AAA = (char)0xa0;

*flashnext = *data;

c = *data++;

timeout = 0;

do

timeout += 1;

while(*flashnext != c && timeout < (unsigned short)0xffff);

flashnext++;

}

}

对于上位机驱动程序,在Windows系统中,PCI设备需要专用的驱动程序,系统上电后会自动扫描PCI总线上的设备,本文通过WindRiver开发工具实现驱动程序。设置好DSP的PCI寄存器DSPP,即可直接访问DSP的预存取4M空间,设置DSP的寄存器RSTSRC的值,即可产生PCI中断。

引言

CPCI规范是由PICMG制定的一种开放工业计算机标准,用于工业和嵌入式应用。CPCI系统背板和CPCI板卡采用标准的2mm高密度气密性针孔连接器,提高了系统可靠性。在电气、逻辑和软件功能等方面,其与PCI标准完全兼容,使得基于PCI技术的丰富软件工具同样可以在CPCI系统中使用。另外,CPCI可采用IEEE 1101.11后端输出方式,使系统维护更加便捷。

CPCI板卡的尺寸分3U(100mm×160mm)和6U(160mm×233mm)两种,3U系统只提供32位/64位的PCI系统总线,6U的系统除了提供32位/64位的PCI系统总线外,还通过连接器接口J3、J4、J5实现自定义总线,可用作高速数据通信或通用输入/输出线等,适用于数字化高速处理的模块化设计应用。

本文利用TMS320C6416T内部集成的32位、33MHz PCI主/从接口,给出了6U的CPCI信号处理板卡设计方案,并对其软件设计特别是DSP的二次引导程序做了说明。

硬件设计

CPCI板卡有J1~J5五个连接器接口,其中只有J1是必须有的,为32位PCI信号接口。J2为64位扩展PCI信号。对于主控板以外的CPCI板卡,J3、J4、J5可用作用户自定义接口。本文所设计的CPCI板卡使用J1、J4、J5接口,主要由DSP、FPGA、SDRAM、FLASH等组成。板卡以TMS320C6416T为核心,通过高性能FPGA实现AD数据采集后的预处理,然后经64位宽的EMIFA总线传入 TMS320C6416T中进行数字信号处理,处理数据可通过32位PCI总线、光收发器或CPCI自定义总线传输至外部设备。CPCI的J1接口为32 位、33M的PCI接口信号,与TMS320C6416T的PCI外设连接。DSP通过EMIFA的CE0存储空间连接4片SDRAM芯片 MT48LC32M16A2,扩展成64位宽度的128MB存储器,CE1、CE2空间连接FPGA,通过J4、J5扩展。EMIFB的CE1空间通过 FLASH芯片S29LV016D扩展2MB的FLASH,用于系统的自举。系统框图如图1所示。

图1 CPCI板卡框图

处理板通过高速16位ADC芯片LTC2206实现模数转换,然后将数据传输到FPGA进行数据预处理,包括数字下变频及缓存等,之后经64位EMIFA 总线通过EDMA传到DSP中进行数字信号处理,最后通过CPCI总线传输到主机。板卡通过带选择器的时钟分配器SY89464实现内外时钟的控制和单端时钟到差分时钟的转换。FPGA的配置芯片采用EPC16,配置方式为PS,EPC和FPGA通过JTAG链实现编程。

TMS320C6416T通过SDRAM扩展256MB存储空间,SDRAM采用512Mb芯片MT48LC32M16A2,位宽为16位,通过4个此芯片扩展为64位。

EMIFB的CE1空间通过FLASH扩展BOOTROM空间,采用FLASH芯片S29AL016D实现,S29AL016D有8位byte和16位word两种方式,通过引脚byte#设置,这里使用8位数据格式。

PCI接口信号的连接如图2所示,使能TMS320C6416T的PCI接口对应PCI_en引脚置高。该接口符合PCI 2.2规范,为33M、32位的PCI主/从接口。

图2 TMS320C6416T的PCI接口电路图

上电后DSP自动从4KB的EEPROM芯片93LC66B读取配置信息。DSP与上位机可通过EDMA进行数据传输。

这里,DSP的输入时钟采用50M晶振通过零延迟时钟缓冲分配器CY2308输出,DSP的EMIFA、EMIFB外接存储器时钟为100MHz,也通过晶体振荡器连接CY2308给出。

DSP和FPGA的核电压均为1.2V,I/O电压为3.3V,1.2V通过CPCI接口的5V电压经开关电源控制芯片TPS54612实现,3.3V经LDO芯片MIC29300实现。电路如图3所示。

图3 电源电路图

软件设计

板卡的软件设计包括DSP的Boot程序、上位机的驱动程序及信号处理板需要实现的专门算法程序。这里重点介绍TMS320C6416的二次Bootloader程序设计。

TMS320C6416T的程序加载方式有HPI、ROM、Noboot、JTAG等几种,通过上电时BEA[18:19]的值决定,板卡中可通过拨码开关进行设置。使用ROM加载可实现系统上电自动加载,其加载过程是:DSP内部Bootloader程序将保存于外部ROM(FLASH)中的前1K字节长度的程序自动搬到DSP内部RAM 0地址处,然后从0地址开始执行程序。由于应用程序一般都大于1K字节,所以必须用二次引导的方法。二次引导程序放在FLASH的前1K字节中,这样 DSP自动Boot完成后就从0地址开始执行二次引导程序。当所有的数据都搬运完毕后,DSP跳转到主程序的入口处,并开始执行主程序。为了实现这一引导过程,首先需要在验证好的算法程序工程文件中加入二次Boot的搬移文件,并修改CMD文件,通过CCS编译成out文件后,通过hex工具转换成.hex文件,再转变文件格式成bin二进制数据文件格式,最后通过另外的FLASH烧写工程文件写入到FLASH中。

TMS320C6416T只支持8位的ROM加载。ROM中的程序存储格式需要与芯片的大小端存储模式一致。

搬移文件Boot.asm采用汇编语言实现,实现1K代码的搬移。

CMD文件中应将Boot段分配为从地址0开始的1K空间,FLASH空间从0x64000000开始,长度也为1K,即分配为:

MEMORY

{

BOOT : origin = 0x00000000, len = 0x00000400

ISRAM : origin = 0x00000400, len = 0x000ffc00 ;DSP的内部L2空间

FLASH : origin = 0x64000000, len = 0x00000400

}

利用CCS经工程文件编译生成.out文件后,再利用其自带的Hex转换工具hex6x.exe转换成hex文件,转换时需要首先编写一个cmd命令文件, 说明需要转换的out文件名、存储器宽度、Flash起始地址和长度、hex输出文件名等。如cmd文件名为myHex_cmd,则调用格式为:

hex6x.exe myHex_Cmd.cmd

hex文件以行为单位。每行以字符 ‘:’ (0x3a)开头,以回车和换行符(0x0d、0x0a)为结束。每行开始和结束之间的所有内容都是以字符形式表现的。通过C程序将hex文件转换为 bin文件,在烧写FLASH的工程中以.h头文件保存定义为data数组。然后在CCS中通过FlashBurn的工程文件将data数据烧写到 FLASH中,即可实现DSP的上电自举。

FlashBurn工程文件主要实现S29AL016D的编程。S29AL016D的编程流程图如图4所示。

图4 FLASH写操作流程图

按照S29AL016D的命令格式和程序流程,烧写FLASH子程序如下。其中,*data为要写入的数组,nByte为数据个数。

void BurnFlash(unsigned char *data, unsigned long nBytes)

{

unsigned short timeout;

unsigned char c;

while(nBytes--)

{

*(volatile char *)0x64000AAA = (char)0xaa;

*(volatile char *)0x64000555= (char)0x55;

*(volatile char *)0x64000AAA = (char)0xa0;

*flashnext = *data;

c = *data++;

timeout = 0;

do

timeout += 1;

while(*flashnext != c && timeout < (unsigned short)0xffff);

flashnext++;

}

}

对于上位机驱动程序,在Windows系统中,PCI设备需要专用的驱动程序,系统上电后会自动扫描PCI总线上的设备,本文通过WindRiver开发工具实现驱动程序。设置好DSP的PCI寄存器DSPP,即可直接访问DSP的预存取4M空间,设置DSP的寄存器RSTSRC的值,即可产生PCI中断。

电子 PIC 嵌入式 连接器 总线 DSP FPGA 收发器 ADC 电路图 振荡器 电压 开关电源 LDO 电路 555 Altera 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 我国科学家人脸与笔迹识别领域获突破(04-29)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)