从磁性随机存取存储器到磁性逻辑单元

时间:11-25

来源:互联网

点击:

作者:Bruno Mussard

磁性随机存取存储器(MRAM)是一种非易失性存储器技术,正在作为一种主流的数据存储技术被业界所广泛接受。它集成了一个磁阻器件和一个硅基选择矩阵。MRAM的关键属性有非易失性、低电压工作、无限次读写的耐用性、快速读写操作,并且作为后端技术而容易集成。这些特性使得MRAM有可能替代各种应用中的许多类型存储器。

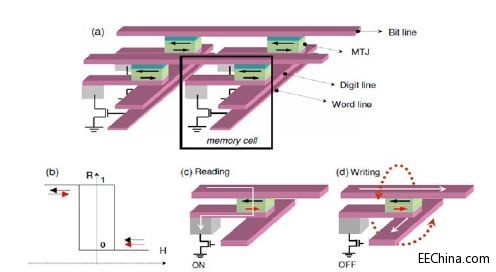

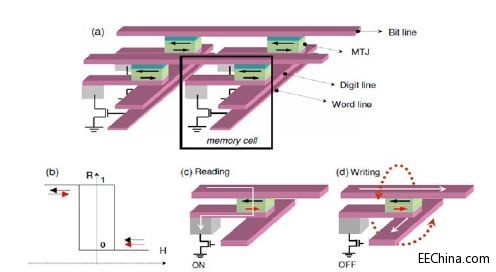

在最简单的实现中,一个MRAM单元由连接着一个选择晶体管的磁性隧道结(MTJ)组成。磁性隧道结有两个磁层组成,中间用一个很薄的氧化隧道势垒隔开。其中一个磁层有固定的磁方向,被称为参考层(FR),另一个称为存储层(SL),它可以从一个方向切换到另一个方向。存储比特的阻抗是低是高取决于存储层相对于固定参考层的磁方向,即平行或反平行。要读取一个比特时,选择晶体管导通,有个小的读取电流流经隧道结,如图1所示。然后将结点阻抗的值与位于高低阻抗值之间一半的参考阻抗进行比较。

图1:(a)第一代MRAM中使用的传统架构在正交写入线的交叉点和选择晶体管顶部包含MTJ单元。(b)最小磁滞回线的原理图显示存储层的反转和两个对应的阻值:高“1”和低“0”。传统MRAM架构中使用的读取(c)和写入机制(d)。在读取时,选择晶体管处于导通状态,有个小的电流流经MTJ堆栈,允许其阻抗的测量。在写入时,选择晶体管处于断开状态,2个正交磁场的组合确保了选择性。

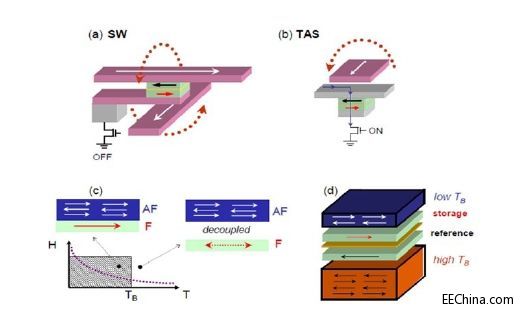

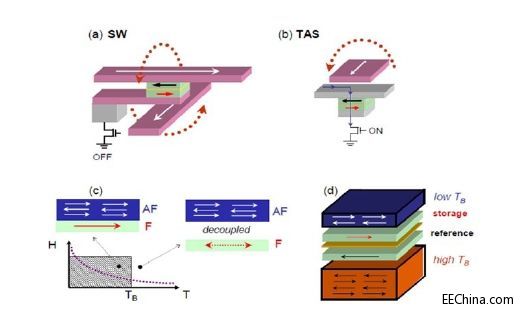

图2:传统MRAM架构(a)和TAS-MRAM架构(b)中的写入过程。在TAS-MRAbM写入方法(c)中,存储单元的写入只有在克服反铁磁性物质的阻塞温度后才有可能,而这种物质能阻止存储层(当两个层被磁性退耦时)。(d)TA-MRAM堆栈总览,其中存储层和参考层都受到反铁磁性层的牵制。

区分不同MRAM主要靠写入存储层的方法。所有这些传统方法都存在一个共同的问题,即它们的可缩放性。随着MTJ尺寸的缩小,长时间保持写入的数据状态的能力也会降低。虽然业界尝试用了各种方法来抵消这种效应,但它们都存在着使用高得多的功率写入数据的问题,从应用角度看使得这种存储器缺乏吸引力,从而限制了市场的普及。

TAS-MRAM概念

为了打破低功耗可写入能力与数据保持能力之间的恶性循环,业界推出了一种被称为热辅助开关(TAS-MRAM)的新方法。这种简单方法使用温度来区分数据存储和低写入功耗要求的属性。CEA/Spintec实验室发明的TAS-MRAM机制对磁存储层进行了改进,增加了一个反铁磁性层,这个层可以在读取操作时“阻塞”存储层的方向。图2所示的写入过程因而包含了局部加热结点到一个足够高的温度以解除这个“阻塞”属性,从而允许存储层在低磁场中被重新定向。这种机制因而支持完全可缩放的比特单元、低功耗的写入和卓越的数据保持能力。

从MRAM到磁性逻辑单元(MLU)

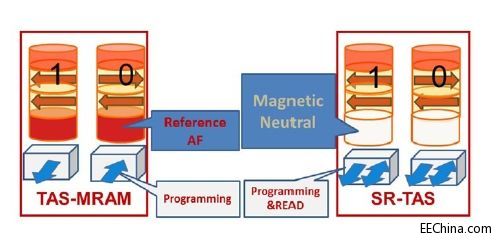

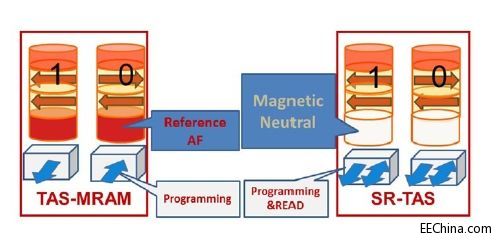

使用TAS-MRAM概念获得的存储信息的优异稳定性激励Crocus Technology公司开发出了一种名为磁性逻辑单元(MLU)的新概念。位于MLU核心的是一个自我参考(SR)的磁单元,这个单元是用无磁层直接取代固定参考层(FR)并重命名为传感层实现的,见图3。如前所述,SR比特单元的阻抗取决于传感层和存储器的磁方向是平行还是反平行的。然而,由于传感层方向可以用磁力线进行控制,因此这个单元变成了真正的3端逻辑单元,其输出值是存储数据的方向和传感层方向的比较结果,定义为输入比磁力线。这个单元用作XOR(异或)逻辑器件。

图3:比较带固定参考(FR)层的TAS-MRAM与带传感参考层(SR)的SR-TAS。

磁单元现在可以排列成链形,这样除了传统的NOR存储器架构外还能实现NAND类架构(Lcell)。在存储器应用中会用到差分读取方式,即在读取过程中传感层会被切换。只有阻抗变化标记定义存储数据的状态,不再需要外部参考阻抗值。MLU不仅可以实现耐用、完全可缩放的存储器解决方案,还能实现新的安全功能,比如传统的“仅存储器”架构不可能实现的位置匹配(Match-in-Place)。

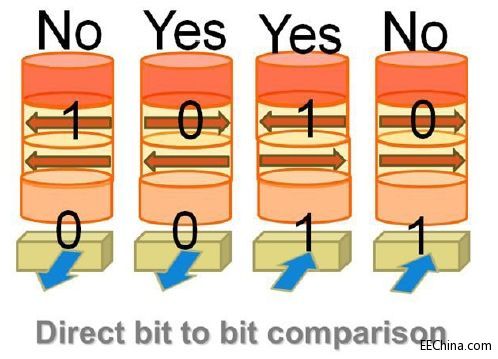

位置匹配

Crocus Technology公司开发出了一种名为位置匹配(Match-in-Place)的创新功能,它在实现用户认证的同时不会向安全黑客暴露任何机密数据。

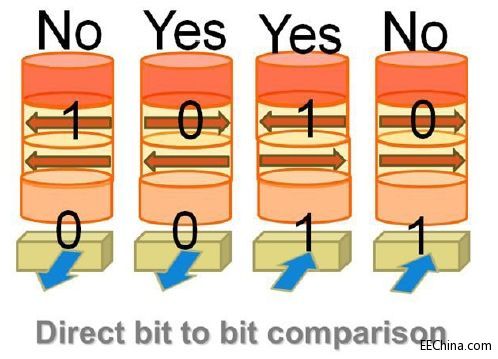

图4:位置匹配。

位置匹配架构的每个单元都是由一个非易失存储器单元和虚拟的MLU异或门组成。多个单元串连在一起形成一条NAND链路,机密数据就存储在这里。用户数据随即施加于磁力线,最终形成的链路阻抗要么正确要么错误。如果输入数据是错误的(即不匹配存储的数据),那就不会有任何信息离开存储器,并提供哪些比特错误的信息。这是线性位置匹配引擎的基本原理。如果多条位置匹配NAND链路以平行方式放置,它们就能同时用来比较某个图案与许多存储图案的差异。

在图4所示例子中,一组4个MLU单元串联在一起形成一条NAND链,并成功创建了一个线性的位置匹配引擎。输入的二进制图案0011与存储的二进制图案1010进行比较。每个存储的比特都要与同组的比特进行逐一比较。敏感的存储数据永远不会被读取并暴露给黑客,匹配周期在速度和功耗上要比现有解决方案高出几个数量级。位置匹配引擎可以用作硬件加速器,进而简化IC架构,降低总体成本。这种新架构的应用领域非常广泛,包括安全微控制器、生物学设备和相关的存储器件。

磁性随机存取存储器(MRAM)是一种非易失性存储器技术,正在作为一种主流的数据存储技术被业界所广泛接受。它集成了一个磁阻器件和一个硅基选择矩阵。MRAM的关键属性有非易失性、低电压工作、无限次读写的耐用性、快速读写操作,并且作为后端技术而容易集成。这些特性使得MRAM有可能替代各种应用中的许多类型存储器。

在最简单的实现中,一个MRAM单元由连接着一个选择晶体管的磁性隧道结(MTJ)组成。磁性隧道结有两个磁层组成,中间用一个很薄的氧化隧道势垒隔开。其中一个磁层有固定的磁方向,被称为参考层(FR),另一个称为存储层(SL),它可以从一个方向切换到另一个方向。存储比特的阻抗是低是高取决于存储层相对于固定参考层的磁方向,即平行或反平行。要读取一个比特时,选择晶体管导通,有个小的读取电流流经隧道结,如图1所示。然后将结点阻抗的值与位于高低阻抗值之间一半的参考阻抗进行比较。

图1:(a)第一代MRAM中使用的传统架构在正交写入线的交叉点和选择晶体管顶部包含MTJ单元。(b)最小磁滞回线的原理图显示存储层的反转和两个对应的阻值:高“1”和低“0”。传统MRAM架构中使用的读取(c)和写入机制(d)。在读取时,选择晶体管处于导通状态,有个小的电流流经MTJ堆栈,允许其阻抗的测量。在写入时,选择晶体管处于断开状态,2个正交磁场的组合确保了选择性。

图2:传统MRAM架构(a)和TAS-MRAM架构(b)中的写入过程。在TAS-MRAbM写入方法(c)中,存储单元的写入只有在克服反铁磁性物质的阻塞温度后才有可能,而这种物质能阻止存储层(当两个层被磁性退耦时)。(d)TA-MRAM堆栈总览,其中存储层和参考层都受到反铁磁性层的牵制。

区分不同MRAM主要靠写入存储层的方法。所有这些传统方法都存在一个共同的问题,即它们的可缩放性。随着MTJ尺寸的缩小,长时间保持写入的数据状态的能力也会降低。虽然业界尝试用了各种方法来抵消这种效应,但它们都存在着使用高得多的功率写入数据的问题,从应用角度看使得这种存储器缺乏吸引力,从而限制了市场的普及。

TAS-MRAM概念

为了打破低功耗可写入能力与数据保持能力之间的恶性循环,业界推出了一种被称为热辅助开关(TAS-MRAM)的新方法。这种简单方法使用温度来区分数据存储和低写入功耗要求的属性。CEA/Spintec实验室发明的TAS-MRAM机制对磁存储层进行了改进,增加了一个反铁磁性层,这个层可以在读取操作时“阻塞”存储层的方向。图2所示的写入过程因而包含了局部加热结点到一个足够高的温度以解除这个“阻塞”属性,从而允许存储层在低磁场中被重新定向。这种机制因而支持完全可缩放的比特单元、低功耗的写入和卓越的数据保持能力。

从MRAM到磁性逻辑单元(MLU)

使用TAS-MRAM概念获得的存储信息的优异稳定性激励Crocus Technology公司开发出了一种名为磁性逻辑单元(MLU)的新概念。位于MLU核心的是一个自我参考(SR)的磁单元,这个单元是用无磁层直接取代固定参考层(FR)并重命名为传感层实现的,见图3。如前所述,SR比特单元的阻抗取决于传感层和存储器的磁方向是平行还是反平行的。然而,由于传感层方向可以用磁力线进行控制,因此这个单元变成了真正的3端逻辑单元,其输出值是存储数据的方向和传感层方向的比较结果,定义为输入比磁力线。这个单元用作XOR(异或)逻辑器件。

图3:比较带固定参考(FR)层的TAS-MRAM与带传感参考层(SR)的SR-TAS。

磁单元现在可以排列成链形,这样除了传统的NOR存储器架构外还能实现NAND类架构(Lcell)。在存储器应用中会用到差分读取方式,即在读取过程中传感层会被切换。只有阻抗变化标记定义存储数据的状态,不再需要外部参考阻抗值。MLU不仅可以实现耐用、完全可缩放的存储器解决方案,还能实现新的安全功能,比如传统的“仅存储器”架构不可能实现的位置匹配(Match-in-Place)。

位置匹配

Crocus Technology公司开发出了一种名为位置匹配(Match-in-Place)的创新功能,它在实现用户认证的同时不会向安全黑客暴露任何机密数据。

图4:位置匹配。

位置匹配架构的每个单元都是由一个非易失存储器单元和虚拟的MLU异或门组成。多个单元串连在一起形成一条NAND链路,机密数据就存储在这里。用户数据随即施加于磁力线,最终形成的链路阻抗要么正确要么错误。如果输入数据是错误的(即不匹配存储的数据),那就不会有任何信息离开存储器,并提供哪些比特错误的信息。这是线性位置匹配引擎的基本原理。如果多条位置匹配NAND链路以平行方式放置,它们就能同时用来比较某个图案与许多存储图案的差异。

在图4所示例子中,一组4个MLU单元串联在一起形成一条NAND链,并成功创建了一个线性的位置匹配引擎。输入的二进制图案0011与存储的二进制图案1010进行比较。每个存储的比特都要与同组的比特进行逐一比较。敏感的存储数据永远不会被读取并暴露给黑客,匹配周期在速度和功耗上要比现有解决方案高出几个数量级。位置匹配引擎可以用作硬件加速器,进而简化IC架构,降低总体成本。这种新架构的应用领域非常广泛,包括安全微控制器、生物学设备和相关的存储器件。

- 基于ARM7的LCD显示电压示波系统的设计(07-27)

- 隔离技术在嵌入式系统接口中的应用(05-30)

- 嵌入式系统电源监控模块设计(06-21)

- 基于STC89C51单片机的数字电压表设计(10-10)

- 数字电路中△I噪声的危害(11-13)

- 基于PIC单片机的空间电压矢量PWM控制方法研究(03-13)