Motion JPEG视频压缩IP核的设计与实现

时间:03-02

来源:互联网

点击:

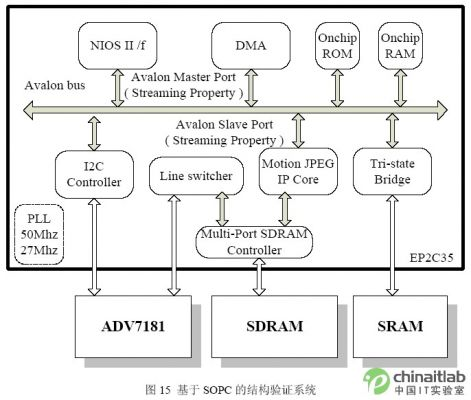

- 3.基于SOPC结构的实际验证系统

经验证,Motion JPEG IP核可以实时处理由NTSC制式摄像头采集经ADV7181处理后输出的CCIR656标准数据,完成对连续视频帧的实时压缩。

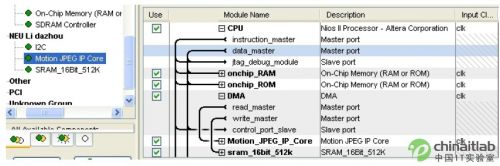

验证系统结构如图15所示,lineswitcher模块把CCIR656标准数据的亮度分量以跳址写入的方式通过Multi-Port SDRAM Controller模块写入到SDRAM中,亮度分量数据从隔行扫描变为逐行存贮。Multi-Port SDRAM Controller模块是一个工业级的SDRAM控制器,可以将一个SDRAM数据端口仿真成四个虚拟的数据端口(两个写端口+两个读端口)。SDRAM在存储空间使用上划分为4个区块,在lineswitcher模块写入一个区块的同时,Motion JPEG IP核读出前一个已写入亮度分量的区块。Motion JPEG IP核输出端是一个Avalon总线上的具有流控制属性从端口。DMA控制器与Motion JPEG IP核以流控制的方式进行数据传输,并把数据转移到SRAM中。整个过程无需NIOSII处理器干预,只须等DMA控制器写满SRAM后以中断的方式通知NIOSII处理器以使其挂起Motion JPEG IP核,防止存入SRAM中数据被覆盖。最后使用DE2_Control_Panel传输SRAM中压缩后的数据到PC中,便可看到采集后图像经压缩后的效果。NIOSII处理器的作用是初始化DMA控制器和通过I2C总线设置ADV7181。

考虑到芯片上的资源,验证时只对ADV7181输出的亮度分量进行压缩,舍弃了色差分量。虽然没有了色差分量,但是仍然可以得到清晰直观的验证效果。

4.结论

本设计主要有以下几个特点。

1:以全流水线结构来实现Motion JPEG视频压缩IP核。

虽然流水线技术已经是一种众所周知的技术,但是现有的Motion JPEG视频压缩IP核仍未实现全部流水线结构,一般多以状态控制模块为核心来协调各个子模块。这就导致系统中最慢的子模块在处理数据时,其它子模块只能等待,对数据块访问的效率低下。同时由于数据块的被多个子模块所使用而又需要复杂的仲裁机制。本文提出的全流水线结构把整个处理过程分解为198个小操作,每个时钟周期内由一阶流水线完成一个小操作。当整个流水线铺满之后,整个数据处理过程中没有等待延迟,没有仲裁协议,大幅提高了系统的运行效率并降低了系统的复杂度。

2:并行矩阵转置结构的提出及基于并行矩阵转置的并行二维离散余弦变换结构。

并行矩阵转置结构较之以往的串行矩阵转置在处理8×8矩阵上至少节省了100个时钟周期。二维离散余弦变换在采用了并行矩阵转置之后,也实现了全部并行处理,43个时钟周期完成了一次二维离散余弦变换,效率提高显著。

3:因采用全流水线结构而取得的较高的运行频率。

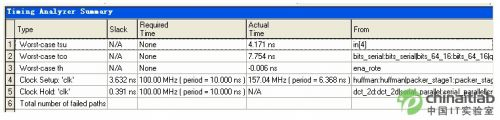

本文设计的Motion JPEG视频压缩IP核在Quartus II 6.0中进行静态时序分析,得到的最高运行频率是150Mhz。

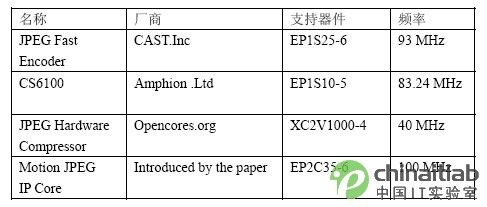

现有IP核与本文设计的IP核的运行频率比较

实际验证时不仅对处理CCIR656标准数据的能力给予验证,同时也为100Mhz的运行频率进行了验证,结果证明IP核可以在100Mhz的运行频率下正常工作。验证方法是把7帧952×568的亮度分量文件存入SDRAM中作为原始数据,整个验证系统以100Mhz频率运行,经过0.05秒完成7帧的压缩,帧率可达147 frame/s。压缩后图像的大小为原来亮度图像的十分之一。

4:可以在低成本,低功耗,高密度的CycloneII系列FPGA芯片上运行,通过Avalon总线与NIOSII处理器构成SOPC系统,为将来实际产品的设计搭建了一个良好的平台。- 3.基于SOPC结构的实际验证系统

嵌入式 集成电路 Altera 总线 FPGA 电路 ModelSim 仿真 Quartus 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)