Motion JPEG视频压缩IP核的设计与实现

时间:03-02

来源:互联网

点击:

0

1

5

6

14

15

27

28

2

4

7

13

16

26

29

42

3

8

12

17

25

30

41

43

9

11

18

24

31

40

44

53

10

19

23

32

39

45

52

54

20

22

33

38

46

51

55

60

21

34

37

47

50

56

59

61

35

36

48

49

57

58

62

63

2.4熵编码模块

熵编码与前面介绍的量化都是数据压缩的手段,但二者有所不同,熵编码利用信号的统计特征来降低位率,理论上不会丢失信息,量化会丢失信息。实现熵编码有多种方式,本文根据ISO/IEC10918协议,使用了游程编码和霍夫曼编码两种方式。游程编码的原理是把沿一定方向排列的等大小量化值的离散余弦变换系数作为连续的整体,用特定码字替代这种连续的整体就会达到数据量减少的效果。霍夫曼编码是一种变长编码,将多次出现的代码用较短的码字代表,很少出现的代码用较长的码字代表。产生哈夫曼编码要求扫描两遍原始数据,第一遍扫描是为了在原始数据中精确地统计每个值出现的频率,第二遍利用构造的哈夫曼树得到编码,两次扫描耗时巨大,因此数据压缩难以满足实时性要求。ISO/IEC10918协议中在对大量8位精度图像的平均统计基础上,给出了4个合适大多数应用的个哈夫曼码表。在实现硬件电路时把哈夫曼码表存储在片上ROM中,使用时直接查找。因为离散余弦变换中直流系数和交流系数分别使用不同的码表,且直流系数不需要进行游程编码,所以直流系数和交流系数使用不同的模块来处理。

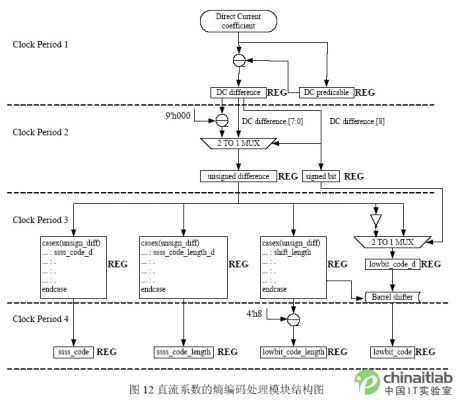

2.4.1直流系数处理模块

直流系数是8×8矩阵内64个像素均值的度量,是包含了整个图像能量的重要部分。利用相邻的8×8矩阵的直流系数具有很强的相关性,对直流系数使用差分压缩编码。前一个8×8矩阵的直流系数作为当前矩阵的直流系数的预测值,求出现实值和预测值之间的差值后,再对差值做霍夫曼编码。在硬件实现时,直流系数只有一个值,所以不需要做游程编码,对其处理的第一步就是求得其与预测值之间的差值。根据差值的大小和正负查找存储在片上ROM的标准霍夫曼码表,得出前缀代码和前缀代码长度,同时根据ISO/IEC10918协议中提出的尾码产生方式得到对应的尾码代码及尾码代码长度。上述处理完成之后再经过合并前缀代码与尾码代码为霍夫曼代码,则直流系数的熵编码完成,之后等待被变长编码模块封装。具体的实现电路由4阶流水线组成,直流系数的熵编码处理过程耗时4个时钟周期。

2.4.2交流系数处理模块

交流系数首先要现经过游程编码处理。在游程编码中非零交流系数前的零交流系数的个数是游程长度,前缀代码及尾码代码的含义与直流系数中的一致,只不过在交流系数处理中游程长度和前缀代码重新组合为一个新的查找索引来查找新的前缀代码。ISO/IEC10918协议中给出的交流系数标准霍夫曼码表里有两个特殊的代码。

一个特殊代码ZRL,ZRL代表游程编码中游程长度大于16,如果游程长度大于32,48,56,分别用1个ZRL,2个ZRL,3个ZRL表示,盈余的游程长度加入下一个游程长度计算中。ZRL代码只有前缀代码,没有尾码代码。为了方便实现,直接把ZRL的尾码代码长度设为零,起到屏蔽尾码的作用。另一个特殊代码EOB,EOB代表最后一个零行程中只有零元素直接代表当前矩阵的游程编码已经扫描结束,若当前矩阵的最后一个交流系数是非零数的则以正常结束一个游程长度的计数作为当前矩阵游程编码的结束。同ZRL类似,EOB也没有尾码代码,所以使用同样的处理手段。具体的实现电路由4阶流水线组成,交流系数的熵编码处理耗时4个时钟周期。

2.4.3交织模块和冗余ZRL消除模块

交织模块的作用是把前缀代码和尾码代码合并为一个霍夫曼代码,合并后的代码易于进行下一阶段的变长编码操作,变长编码操作过程需要的移位位数由前缀代码长度加上尾码代码长度做和得到,这个求和过程也在交织模块中实现。该模块具体实现电路由2阶流水线组成。

冗余ZRL消除模块不是ISO/IEC10918协议的一部分,但它源于标准协议里对EOB的定义。从EOB之前直到最近一个的非零交流系数出现,中间产生的ZRL都是可以消除的。基于全流水线结构的电路设计一般很难满足这一要求,原因是全流水线结构的电路每级产生的结果都会直接传递给下一级,不对结果作保留。唯一的方法就是构造一个同步FIFO来缓存前几个时钟周期内产生的结果,根据之前输入的数据量和当前输入的数据量是否满足ZRL的冗余条件而选择性的对FIFO输出的结果做屏蔽。屏蔽的手段就是把FIFO输出数据的对应的霍夫曼代码长度清零。这样在下一步的变长编码中会因ZRL的霍夫曼代码长度为零而消除冗余的ZRL。

2.4.4变长编码模块

变长编码的作用是把交织编码输出的含有不等长有效位的霍夫曼码字,提取其中的有效位并将其组合为一个连续的32位码流。

编码原理是把交织编码输出的含有不等长有效位的霍夫曼码字向右位,移动的位数是前一个霍夫曼码字的代码长度。移位完成后的当前霍夫曼码字与提供移动的位数的前一个霍夫曼码字做或运算,同时累加两个霍夫曼码字的代码长度。累加和大于24时表明变长编码的第一步完成。第二步是检查前一步产生的24位封装结果中是否有FF字节,若有则直接在FF字节后面添加00字节。并不是所有的24位封装结果都需要在FF字节后面添加00字节,所以在第二步处理中还有移位处理。移位处理采用的方法与第一步移位处理的方法相同的,把24位封装结果和添加00字节后的32位封装结果,统一封装为32位结果输出。这个32位数据也是整个IP核输出的最终压缩结果。

嵌入式 集成电路 Altera 总线 FPGA 电路 ModelSim 仿真 Quartus 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)