AVR IP核复用的FSPLC微处理器SOC设计

时间:03-02

来源:互联网

点击:

4 FSPLC微处理器核SOC设计

4.1 SOC硬件结构

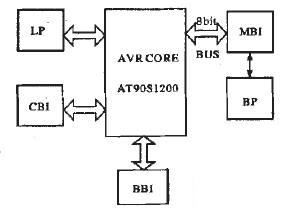

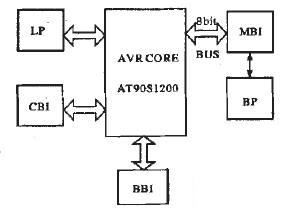

根据FSPLCSOC系统功能定义,设计完成FSPLC微处理器硬件结构,如图4所示。

图4 FSPLCSOC硬件结构框图

FSPLCSOC由AT90S1200、布尔处理器BP、存储器位接口MBI、逻辑处理器LP,CAN总线1。0接口CBI、底板总线接口BBI等6个模块组成。AT90S1200模块是SOC的核心,实现PLC指令的执行;BP模块由两个位累加器和一个位逻辑堆浅BLS组成,该结构可以有效处理IEC61131-3(国际电工委员会制订的基于Windows编程语言标准)PLC指令表语句中复杂的嵌套逻辑运算,使运行频率最高的位指令达到最大的执行速度;存储器位接口模块由一个存储器位寻址接口逻辑和一个8选1选择器组成,为布尔处理器和数据存储器之间的位访间接口;CAN总线1。0接口CBI模块和外部基于Atmega8515的USB-CAN适配器相连,通过此适配器FSPLC可以和其他带有CAN接口的PLC实现CAN通讯;通过底板总线接口BBI模块可以在FSPLC片外扩展模块,最多可以达到8个,包括I/0扩展模块、AID模块、D/A模块、计数模块等。其中AT90S1200,MBI,LP,CBI,BBI模块通过内部总线连接,BP通过MBI模块转换实现和其他模块的连接。

4.2 FSPLCSOC仿真、综合、验证

由于SOC设计是一种面向IP核集成的设计,整合后的SOC模块同第三方IP核复用一样需要进行模块的仿真、综合和验证。FSPLC SOC同复用AT90SI200核一样借助ModelSim进行功能仿真和验证后时序仿真,借助Synplify Pro进行综合。

下面具体描述FSPLCSOC的验证,SOC设计中包含了系统设计和模块设计,因此SOC验证一般包含了模块验证、芯片验证和系统验证三个部分。由于FSPLCSOC涉及到的主要是数字IP核,文中采用Altera NioslI开发板作为设计的验证平台,该开发板带有一个20多万门的Altera EP20K200EFC484-2的FPGA芯片、拨码开关、数码显示器等,用一个实际PLC应用程序在此开发板上对FSPLCSOC进行了可行性验证,同时通过对AVR编译器Avral。0的编译代码变量中增加PLC指令代码,使之能够对PL(:指令进行编译。图5,图6分别为PLC控制程序的梯形图及其汇编程序。

图5 PLC控制程序的梯形图

开发板的拨码开关SWl的1、2、3、4来模拟上述开关的闭合,观察数码显示器Dl数码段明暗,验证设计的可行性。FSPLCSOC在Altera Nios开发板的FPGA芯片上进行了可行性验证,获得了理想的运行效果:在33MHz晶振下,执行基本逻辑指令速度为0。09μ/条,达到了国际上大中型PLC的处理速度。

图6 PSPLC汇编程序

5 结束语

目前IC产业中,SOC已成为最主要的集成电路设计方法8位RISC微处理器芯片设计正在向SOC化发展,通过IP核复用方法以缩短周期、降低成本、提高效率。文中基于IP核复用和SOC技术借助ModelSim、Synplify Pro、QuartusⅡ等EDA软件设计了拥有自主知识产权的专用PLC微处理器SOC模块FSPLC,在复用了第三方AVRAT90SI200IP核基础上集成了自行设计的LP、BP、MBI、CBI、BBI等模块,具有快速处理PLC梯形图程序、快速处理IL语句表中复杂的嵌套逻辑运算、PLC之间CAN总线通讯等优点。最后采用Altera NiosII作为验证平台,对实际的PLC应用程序做了可行性验证,获得了理想的效果。

4.1 SOC硬件结构

根据FSPLCSOC系统功能定义,设计完成FSPLC微处理器硬件结构,如图4所示。

图4 FSPLCSOC硬件结构框图

FSPLCSOC由AT90S1200、布尔处理器BP、存储器位接口MBI、逻辑处理器LP,CAN总线1。0接口CBI、底板总线接口BBI等6个模块组成。AT90S1200模块是SOC的核心,实现PLC指令的执行;BP模块由两个位累加器和一个位逻辑堆浅BLS组成,该结构可以有效处理IEC61131-3(国际电工委员会制订的基于Windows编程语言标准)PLC指令表语句中复杂的嵌套逻辑运算,使运行频率最高的位指令达到最大的执行速度;存储器位接口模块由一个存储器位寻址接口逻辑和一个8选1选择器组成,为布尔处理器和数据存储器之间的位访间接口;CAN总线1。0接口CBI模块和外部基于Atmega8515的USB-CAN适配器相连,通过此适配器FSPLC可以和其他带有CAN接口的PLC实现CAN通讯;通过底板总线接口BBI模块可以在FSPLC片外扩展模块,最多可以达到8个,包括I/0扩展模块、AID模块、D/A模块、计数模块等。其中AT90S1200,MBI,LP,CBI,BBI模块通过内部总线连接,BP通过MBI模块转换实现和其他模块的连接。

4.2 FSPLCSOC仿真、综合、验证

由于SOC设计是一种面向IP核集成的设计,整合后的SOC模块同第三方IP核复用一样需要进行模块的仿真、综合和验证。FSPLC SOC同复用AT90SI200核一样借助ModelSim进行功能仿真和验证后时序仿真,借助Synplify Pro进行综合。

下面具体描述FSPLCSOC的验证,SOC设计中包含了系统设计和模块设计,因此SOC验证一般包含了模块验证、芯片验证和系统验证三个部分。由于FSPLCSOC涉及到的主要是数字IP核,文中采用Altera NioslI开发板作为设计的验证平台,该开发板带有一个20多万门的Altera EP20K200EFC484-2的FPGA芯片、拨码开关、数码显示器等,用一个实际PLC应用程序在此开发板上对FSPLCSOC进行了可行性验证,同时通过对AVR编译器Avral。0的编译代码变量中增加PLC指令代码,使之能够对PL(:指令进行编译。图5,图6分别为PLC控制程序的梯形图及其汇编程序。

图5 PLC控制程序的梯形图

开发板的拨码开关SWl的1、2、3、4来模拟上述开关的闭合,观察数码显示器Dl数码段明暗,验证设计的可行性。FSPLCSOC在Altera Nios开发板的FPGA芯片上进行了可行性验证,获得了理想的运行效果:在33MHz晶振下,执行基本逻辑指令速度为0。09μ/条,达到了国际上大中型PLC的处理速度。

图6 PSPLC汇编程序

5 结束语

目前IC产业中,SOC已成为最主要的集成电路设计方法8位RISC微处理器芯片设计正在向SOC化发展,通过IP核复用方法以缩短周期、降低成本、提高效率。文中基于IP核复用和SOC技术借助ModelSim、Synplify Pro、QuartusⅡ等EDA软件设计了拥有自主知识产权的专用PLC微处理器SOC模块FSPLC,在复用了第三方AVRAT90SI200IP核基础上集成了自行设计的LP、BP、MBI、CBI、BBI等模块,具有快速处理PLC梯形图程序、快速处理IL语句表中复杂的嵌套逻辑运算、PLC之间CAN总线通讯等优点。最后采用Altera NiosII作为验证平台,对实际的PLC应用程序做了可行性验证,获得了理想的效果。

电子 EDA 半导体 AVR PLC 集成电路 电路 ADC 滤波器 仿真 Verilog ModelSim Quartus VHDL FPGA 总线 CAN总线 USB Altera 显示器 相关文章:

- 利用蓝牙技术和远程信息控制单元实现汽车诊断(11-13)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)

- 汽车网络的分类及发展趋向(11-13)

- 多核嵌入式处理技术推动汽车技术发展(11-18)

- CAN总线的客车轻便换档系统设计与实现(02-13)

- 高性能嵌入式ARM MPU在医疗电子系统中的设计应用(05-12)