Лљгк56F8O13 DSPЕФFIRТЫВЈЦїЕФЩшМЦ

ЪБМфЃК11-27

РДдДЃКЛЅСЊЭј

ЕуЛїЃК

Ъ§зжТЫВЈЦїЪЧвЛжжгУРДЙ§ТЫЪБМфРыЩЂаХКХЕФЪ§зжЯЕЭГЃЌЭЈЙ§ЖдГщбљЪ§ОнНјааЪ§бЇДІРэРДДяЕНЦЕгђЁЃТЫВЈЕФФПЕФЁЃИљОнЦфЕЅЮЛГхМЄЯьгІКЏЪ§ЕФЪБгђЬиадПЩЗжЮЊСНРрЃКЮоЯоГхМЄЯьгІ(IIR)ТЫВЈЦїКЭгаЯоГхМЄЯьгІ(FIR)ТЫВЈЦїЁЃгыIIRТЫВЈЦїЯрБШЃЌFIRТЫВЈЦїжЛгаСуЕуЃЌГ§дЕуЭтЃЎдкzЦНУцЩЯУЛгаМЋЕуЃЌвђДЫзмЪЧЮШЖЈЕФКЭПЩЪЕЯжЕФЃЛИќживЊЕФЪЧЃЌFIRТЫВЈЦїдкТњзувЛЖЈЕФЖдГЦЬѕМўЯТЃЌПЩвдЛёЕУбЯИёЕФЯпадЯрЮЛЬиадЃЌетвЛЕуЪЧIIRТЫВЈЦїФбвдЪЕЯжЕФЁЃвђДЫЁЃЫќдкИпБЃецЕФаХКХДІРэЃЎШчЪ§зжвєЦЕЁЂЭМЯёДІРэЁЂЪ§ОнДЋЪфЁЂЩњЮявНбЇЕШСьгђЕУЕНЙуЗКгІгУЁЃ

1 FIRТЫВЈЦїЛљБОНсЙЙ

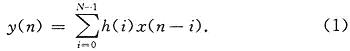

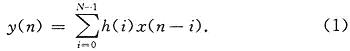

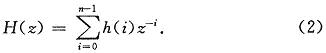

FIRТЫВЈЦїЕФЪ§бЇБэДяЪНЮЊЃК

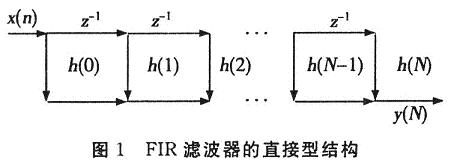

ЪНжаЃКNЮЊFIRТЫВЈЦїЕФГщЭЗЪ§ЃЛx(n)ЮЊЕкnЪБПЬЕФЪфШыбљБОЃЛh(i)ЮЊFIRТЫВЈЦїЕкiМЖГщЭЗЯЕЪ§ЁЃ

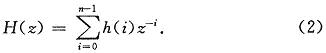

ЦфЯргІЕФzБфЛЛЮЊЃК

ЪНжаЃКz-iЮЊN-1НзЖрЯюЪНЁЃ

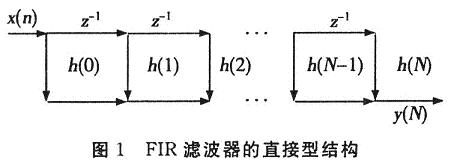

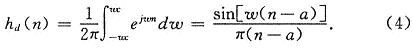

ЦеЭЈЕФжБНгаЭFIRТЫВЈЦїНсЙЙШчЭМ1ЫљЪОЁЃ

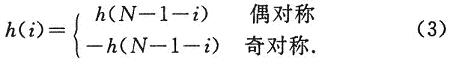

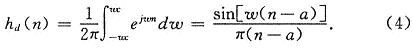

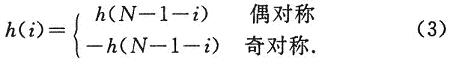

дкздЪЪгІДІРэЁЂЪ§ОнЭЈаХЕШСьгђжаЭљЭљвЊЧѓаХКХдкДЋЪфЙ§ГЬжаВЛФмгаУїЯдЕФЯрЮЛЪЇецЃЌFIRТЫВЈЦїПЩвдзіЕНЯпадЯрЮЛТњзуДЫвЊЧѓЁЃF1RТЫВЈЦїЪЕжЪЩЯЪЧвЛИіЗжНкЕФбгГйЯпЃЌАбУПвЛНкЕФЪфГіМгШЈРлМгЃЌЕУЕНТЫВЈЦїЕФЪфГіЁЃЖдгкFIRТЫВЈЦїЕФЕЅЮЛТіГхЯьгІh(i)жЛвЊТњзувдЯТ2ИіЬѕМўжЎвЛЃЌдђЮЊЯпадЯрЮЛТЫВЈЦїЁЃ

ЯпадЯрЮЛЕФFIRТЫВЈЦїОпгажааФЖдГЦЕФЬиадЃЌЦфЖдГЦжааФдкNЃЏ2ДІЁЃ

(2)гЩадФмжИБъШЗЖЈДАКЏЪ§w(n)КЭДАПкГЄЖШN

(3)ЧѓЕУЪЕМЪТЫВЈЦїЕФЕЅЮЛТіГхЯьгІh(n)

(4)МьбщТЫВЈЦїадФмЁЃ

ЩшМЦГЃгУЕФДАКЏЪ§гаОиаЮДАЁЂККФўДАЁЂКЃУїДАЁЂПШіДАЕШЁЃЦфжаЃККЃУїДАЕФХдАъЗхжЕаЁгкжїАъЗхжЕЕФ1ЃЅЃЌ99ЃЎ963ЃЅЕФФмСПМЏжадкжїАъФкЃЎЧвЭЈЙ§КЃУїДАЩшМЦЕФFIRТЫВЈЦїдкНЯЩйЕФНзЪ§ЯТПЩвдЕУЕННЯаЁЭЈДјЮЦВЈЃЌЗЧГЃЪЪКЯЙЄГЬЩшМЦЃЌЫљвдБОЩшМЦбЁдёКЃУїДАЪЕЯжЁЃ

3 РћгУQEDesign LiteЩшМЦFIRТЫВЈЦї

ИљОнДАКЏЪ§ЩшМЦЕФFIRТЫВЈЦїЕФЕЅЮЛТіГхЯьгІЃЎh(n)гаЖржжИЈжњЙЄОпНјааЧѓШЁЃЌШчЃКMATLABЕФFDAToolЁЂSPToolКЭNIЕФDigital Fliter Design ToolkitЕШЃЌдкДЫЃЎЮвУЧЪЙгУСЫFreeScaleDSPПЊЗЂЛЗОГCodewarrior8ЃЎOздДјЕФQEDesignliteТЫВЈЦїЩшМЦЙЄОпЯфНјааFIRТЫВЈЦїЕЅЮЛТіГхЯьгІh(n)ЕФЧѓНтЁЃ

РћгУQE Design liteТЫВЈЦїЩшМЦЙЄОпЯфЃЌПЩПьЫйНјааIIRТЫВЈЦїЁЂЛљгкДАКЏЪ§FIRТЫВЈЦїКЭЕШЮЦВЈFIRТЫВЈЦїЕФЕЭЭЈЁЂИпЭЈЁЂДјЭЈКЭДјзшЩшМЦЁЃВЂИљОнЩшМЦВЮЪ§ЃЌздЖЏЩњГЩТЫВЈЦїЕФЗљЦЕЯьгІЁЂЯрЦЕЯьгІЁЂШКбгЪБЁЂГхЛїЯьгІКЭЕЅЮЛНздОЯьгІЃЌвдМАЩњГЩЕЅЮЛТіГхЯьгІh(n)ЕФ*ЃЎhЮФМўКЭИУFIRТЫВЈЦїЪЙгУЪОР§CЮФМўЃЌвдЗНБуКѓајЩшМЦЁЃЦфжївЊЩшМЦВНжшШчЯТЃК

(1)дЫааГЬађQEDesign liteЃЌбЁдёВЫЕЅЯюЁАDesignI FIRWindows DesignЁЁЁБЃК

(2)дкЕЏГіЕФЁАFIR(Windows)DesignЁБДАЬхжаЃЌбЁдёЁАlowpassЁБбЁЯюЃЛ

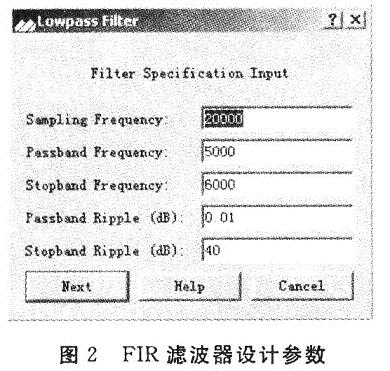

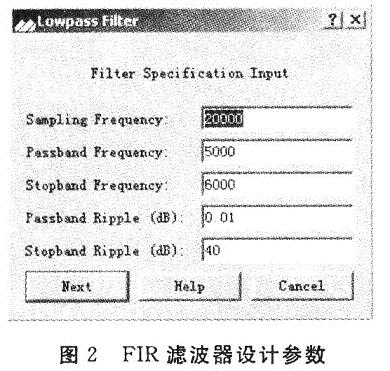

(3)дкЁАLowpass FilterЁБДАЬхжаЃЌЪфШыFIRТЫВЈЦїЕФЩшМЦжИБъЃКВЩбљЦЕТЪ=20000 HzЁЂЭЈДјЦЕТЪ=5000 HzЁЂзшДјЦЕТЪ=6000 HzЁЂЭЈДјЮЦВЈ=OЃЎ01 dBКЭзшДјЮЦВЈ=40 dBЃЎШчЭМ2ЫљЪОЃЛ

(4)ШЗЖЈВЩгУЕФДАКЏЪ§РраЭМАНзЪ§(БОР§ВЩгУhammingДАЃЎНзЪ§ЮЊ27Нз)ЃЛ

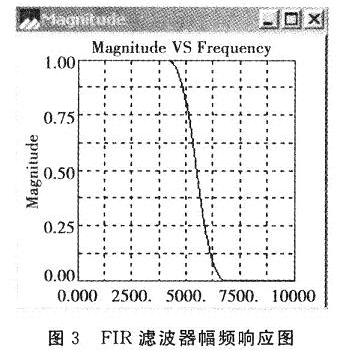

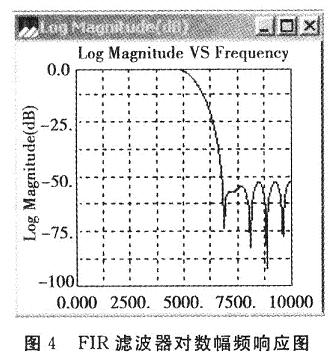

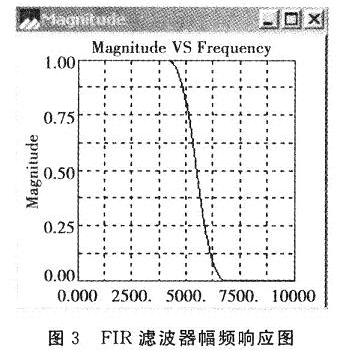

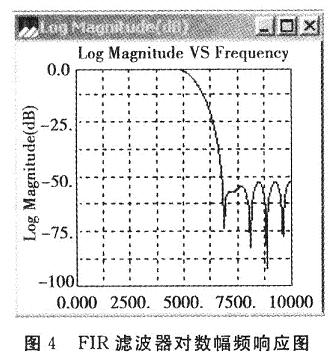

(5)ИљОнЩшЖЈЕФFIRТЫВЈЦїВЮЪ§ЃЌМДПЩЕУЕНИУFIRТЫВЈЦїЕФЗљЦЕЯьгІЭМЁЂЖдЪ§ЗљЦЕЯьгІЭМЁЂЯрЦЕЯьгІЭМЁЂШКбгЪБЭМЁЂГхЛїЯьгІЭМКЭЕЅЮЛНздОЯьгІЭМЃЌПЩжБЙлЕФЙлВьЩшМЦЪЧЗёТњзувЊЧѓЃЎШчЙћВЛТњзуЩшМЦвЊЧѓЃЌПЩжиИДВНжш3)ЁЂ4)ЃЌжБжСТњзуЩшМЦвЊЧѓЮЊжЙЁЃБОFIRТЫВЈЦїЕФЗљЦЕЯьгІЭМЁЂЖдЪ§ЗљЦЕЯьгІЭММћЭМ3ЁЂЭМ4ЃЛ

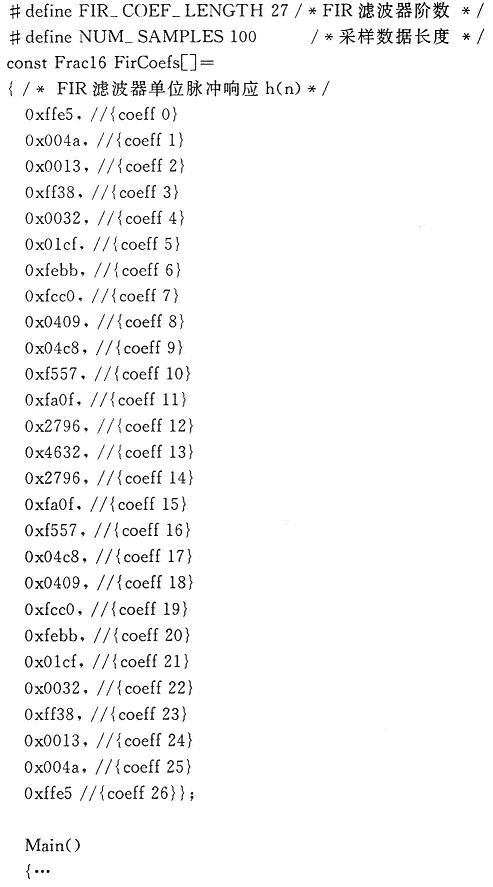

(6)ЩшМЦЕФFIRТЫВЈЦїТњзувЊЧѓКѓЃЌбЁдёВЫЕЅЯюЁАCode-Gen|FreeScale|DPS56800ЃЏDPS56800EЁБЃЌЕМГіЛљгк16ЮЛЖЈЕуЪ§ЕФЕЅЮЛТіГхЯьгІh(n)ЕФ*ЃЎhЮФМўЃЌгУгкКѓајЕФЙЄГЬЩшМЦЁЃ

4 Лљгк56F8013 DSPЕФЩшМЦЪЕЯж

56F8013ЪЧFreeScaleЭЦГіЕФЛљгк56F800EФкКЫЕФЕЭМлЮЛЁЂЕЭЙІКФЕФ16ЮЛDSPЃЌЫќОпгаI2CЁЂSPIЁЂUARTЁЂADCЁЂQEIЕШЭтВПНгПкЃЌОпгадкЦЌгВМўЕїЪдНгПкЃЌПЩНјаа32ЮЛећЪ§ЁЂ36ЮЛећЪ§МгЗжЪ§дЫЫуЃЌХфКЯCodeWarriorПЊЗЂЛЗОГЗЧГЃЪЪКЯгкЧЖШыЪНПЊЗЂЁЃ

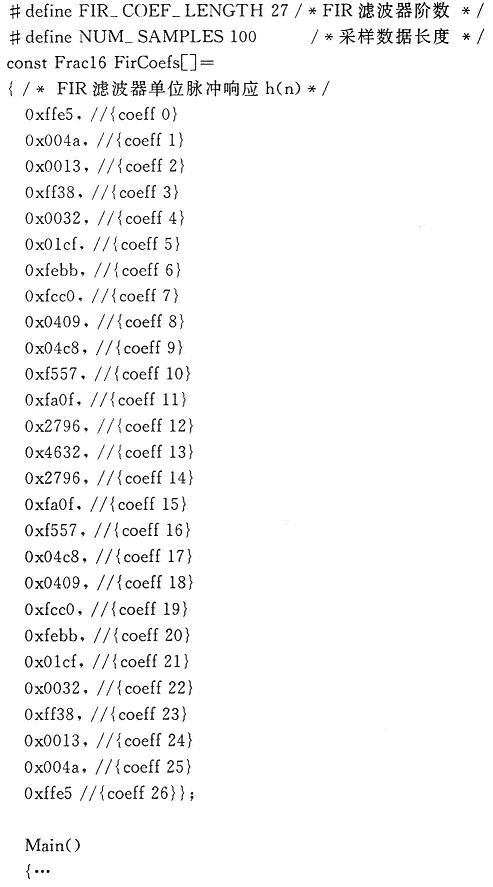

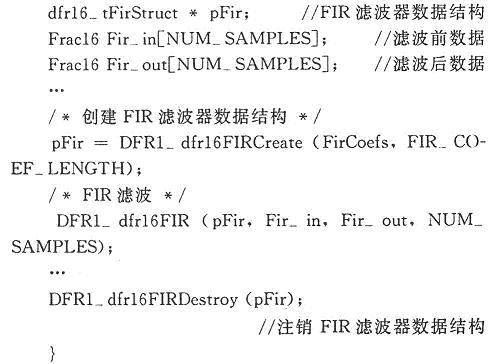

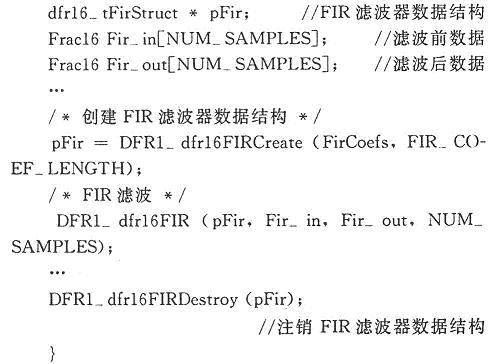

Processor Expert(PE)ЪЧгЩНнПЫUNISЙЋЫОПЊЗЂЕФеыЖдFreeScaleЕЅЦЌЛњКЭDSPЕФЧЖШыЪНШэМўПЊЗЂАќЃЎЫќМЏГЩдкCodeWarriorПЊЗЂЛЗОГжаЁЃProcessor ExpertЬсЙЉСЫСЌНгЁЂЩњГЩЧЖШыЪНЯЕЭГЕФгВМўЁЂНгПкКЭЫуЗЈЕФЧ§ЖЏЃЌЖдCPUКЫЁЂаОЦЌМЏГЩНгПкЁЂащФтЩшБИКЭДПЫуЗЈНјааСЫЗтзА(ИУЗтзАБЛГЦЮЊЁАEmbedded BeansЁБ)ЃЌВЂАбетаЉЙІФмБфГЩЪєадЁЂЗНЗЈКЭЪТМўЃЌетгыУцЯђЖдЯѓЕФГЬађЩшМЦЗНЗЈЪЧвЛбљЕФЁЃгУЛЇдкНјааГЬађЩшМЦЪБЃЌЭЈЙ§ЕїгУProcessor ExpertЬсЙЉЕФИїжжBeanЃЌПЩвдЗНБуЕФЖдDSPФкКЫЁЂЭтВПжаЖЯЁЂDSPЕФЦЌЩЯЭтЩшМАГЬађЫљашЕФИїжжЭЈгУЫуЗЈНјааЩшжУЃЎЪЙгУЛЇжЛашЙизЂећИіЩшМЦЕФДДдьадВПЗжЃЌЖјВЛЪЧЛЈЗбДѓСПЪБМфШУаОЦЌе§ГЃЙЄзїЃЌДѓДѓЬсИпСЫЩњВњТЪЁЃБОЮФЕФFIRТЫВЈЦїЕФЪЕЯжЃЌОЭЪЧЛљгкProcessor ExpertЕФЁАDSP_Func_DFRЁБBeanКЭЁАDSP_MEMЁБBeanЕФЁЃЯжНЋОпЬхЕФЩшМЦЙ§ГЬУшЪіШчЯТЃК

НјШыCodeWarriorПЊЗЂЛЗОГЃЌбЁжаВЫЕЅЯюЁАProcessor Expertl| View| Bean SelectorЁБЃЌдкЕЏГіЕФЁАBean SelectorЁБДАПкжаЃЌбЁжаИКд№ФкДцЙмРэЕФЁАDSP_MEMЁБBeanКЭИКд№Ъ§зжаХКХДІРэЕФЁАDSP_Func_DFRЁБBeaflМгШыЙЄГЬЮФМўЃЌНЋЁАDSP_Func_DFRЁБBeanжаЕФЁАdfrl6FIRCreateЁБЁЂЁАdfrl6FIRЁБКЭЁАdfrl6FIRDestroyЁБЗНЗЈМгШыжїГЬађЁЃаоИФжїГЬађШчЯТЃК

1 FIRТЫВЈЦїЛљБОНсЙЙ

FIRТЫВЈЦїЕФЪ§бЇБэДяЪНЮЊЃК

ЪНжаЃКNЮЊFIRТЫВЈЦїЕФГщЭЗЪ§ЃЛx(n)ЮЊЕкnЪБПЬЕФЪфШыбљБОЃЛh(i)ЮЊFIRТЫВЈЦїЕкiМЖГщЭЗЯЕЪ§ЁЃ

ЦфЯргІЕФzБфЛЛЮЊЃК

ЪНжаЃКz-iЮЊN-1НзЖрЯюЪНЁЃ

ЦеЭЈЕФжБНгаЭFIRТЫВЈЦїНсЙЙШчЭМ1ЫљЪОЁЃ

дкздЪЪгІДІРэЁЂЪ§ОнЭЈаХЕШСьгђжаЭљЭљвЊЧѓаХКХдкДЋЪфЙ§ГЬжаВЛФмгаУїЯдЕФЯрЮЛЪЇецЃЌFIRТЫВЈЦїПЩвдзіЕНЯпадЯрЮЛТњзуДЫвЊЧѓЁЃF1RТЫВЈЦїЪЕжЪЩЯЪЧвЛИіЗжНкЕФбгГйЯпЃЌАбУПвЛНкЕФЪфГіМгШЈРлМгЃЌЕУЕНТЫВЈЦїЕФЪфГіЁЃЖдгкFIRТЫВЈЦїЕФЕЅЮЛТіГхЯьгІh(i)жЛвЊТњзувдЯТ2ИіЬѕМўжЎвЛЃЌдђЮЊЯпадЯрЮЛТЫВЈЦїЁЃ

ЯпадЯрЮЛЕФFIRТЫВЈЦїОпгажааФЖдГЦЕФЬиадЃЌЦфЖдГЦжааФдкNЃЏ2ДІЁЃ

(2)гЩадФмжИБъШЗЖЈДАКЏЪ§w(n)КЭДАПкГЄЖШN

(3)ЧѓЕУЪЕМЪТЫВЈЦїЕФЕЅЮЛТіГхЯьгІh(n)

(4)МьбщТЫВЈЦїадФмЁЃ

ЩшМЦГЃгУЕФДАКЏЪ§гаОиаЮДАЁЂККФўДАЁЂКЃУїДАЁЂПШіДАЕШЁЃЦфжаЃККЃУїДАЕФХдАъЗхжЕаЁгкжїАъЗхжЕЕФ1ЃЅЃЌ99ЃЎ963ЃЅЕФФмСПМЏжадкжїАъФкЃЎЧвЭЈЙ§КЃУїДАЩшМЦЕФFIRТЫВЈЦїдкНЯЩйЕФНзЪ§ЯТПЩвдЕУЕННЯаЁЭЈДјЮЦВЈЃЌЗЧГЃЪЪКЯЙЄГЬЩшМЦЃЌЫљвдБОЩшМЦбЁдёКЃУїДАЪЕЯжЁЃ

3 РћгУQEDesign LiteЩшМЦFIRТЫВЈЦї

ИљОнДАКЏЪ§ЩшМЦЕФFIRТЫВЈЦїЕФЕЅЮЛТіГхЯьгІЃЎh(n)гаЖржжИЈжњЙЄОпНјааЧѓШЁЃЌШчЃКMATLABЕФFDAToolЁЂSPToolКЭNIЕФDigital Fliter Design ToolkitЕШЃЌдкДЫЃЎЮвУЧЪЙгУСЫFreeScaleDSPПЊЗЂЛЗОГCodewarrior8ЃЎOздДјЕФQEDesignliteТЫВЈЦїЩшМЦЙЄОпЯфНјааFIRТЫВЈЦїЕЅЮЛТіГхЯьгІh(n)ЕФЧѓНтЁЃ

РћгУQE Design liteТЫВЈЦїЩшМЦЙЄОпЯфЃЌПЩПьЫйНјааIIRТЫВЈЦїЁЂЛљгкДАКЏЪ§FIRТЫВЈЦїКЭЕШЮЦВЈFIRТЫВЈЦїЕФЕЭЭЈЁЂИпЭЈЁЂДјЭЈКЭДјзшЩшМЦЁЃВЂИљОнЩшМЦВЮЪ§ЃЌздЖЏЩњГЩТЫВЈЦїЕФЗљЦЕЯьгІЁЂЯрЦЕЯьгІЁЂШКбгЪБЁЂГхЛїЯьгІКЭЕЅЮЛНздОЯьгІЃЌвдМАЩњГЩЕЅЮЛТіГхЯьгІh(n)ЕФ*ЃЎhЮФМўКЭИУFIRТЫВЈЦїЪЙгУЪОР§CЮФМўЃЌвдЗНБуКѓајЩшМЦЁЃЦфжївЊЩшМЦВНжшШчЯТЃК

(1)дЫааГЬађQEDesign liteЃЌбЁдёВЫЕЅЯюЁАDesignI FIRWindows DesignЁЁЁБЃК

(2)дкЕЏГіЕФЁАFIR(Windows)DesignЁБДАЬхжаЃЌбЁдёЁАlowpassЁБбЁЯюЃЛ

(3)дкЁАLowpass FilterЁБДАЬхжаЃЌЪфШыFIRТЫВЈЦїЕФЩшМЦжИБъЃКВЩбљЦЕТЪ=20000 HzЁЂЭЈДјЦЕТЪ=5000 HzЁЂзшДјЦЕТЪ=6000 HzЁЂЭЈДјЮЦВЈ=OЃЎ01 dBКЭзшДјЮЦВЈ=40 dBЃЎШчЭМ2ЫљЪОЃЛ

(4)ШЗЖЈВЩгУЕФДАКЏЪ§РраЭМАНзЪ§(БОР§ВЩгУhammingДАЃЎНзЪ§ЮЊ27Нз)ЃЛ

(5)ИљОнЩшЖЈЕФFIRТЫВЈЦїВЮЪ§ЃЌМДПЩЕУЕНИУFIRТЫВЈЦїЕФЗљЦЕЯьгІЭМЁЂЖдЪ§ЗљЦЕЯьгІЭМЁЂЯрЦЕЯьгІЭМЁЂШКбгЪБЭМЁЂГхЛїЯьгІЭМКЭЕЅЮЛНздОЯьгІЭМЃЌПЩжБЙлЕФЙлВьЩшМЦЪЧЗёТњзувЊЧѓЃЎШчЙћВЛТњзуЩшМЦвЊЧѓЃЌПЩжиИДВНжш3)ЁЂ4)ЃЌжБжСТњзуЩшМЦвЊЧѓЮЊжЙЁЃБОFIRТЫВЈЦїЕФЗљЦЕЯьгІЭМЁЂЖдЪ§ЗљЦЕЯьгІЭММћЭМ3ЁЂЭМ4ЃЛ

(6)ЩшМЦЕФFIRТЫВЈЦїТњзувЊЧѓКѓЃЌбЁдёВЫЕЅЯюЁАCode-Gen|FreeScale|DPS56800ЃЏDPS56800EЁБЃЌЕМГіЛљгк16ЮЛЖЈЕуЪ§ЕФЕЅЮЛТіГхЯьгІh(n)ЕФ*ЃЎhЮФМўЃЌгУгкКѓајЕФЙЄГЬЩшМЦЁЃ

4 Лљгк56F8013 DSPЕФЩшМЦЪЕЯж

56F8013ЪЧFreeScaleЭЦГіЕФЛљгк56F800EФкКЫЕФЕЭМлЮЛЁЂЕЭЙІКФЕФ16ЮЛDSPЃЌЫќОпгаI2CЁЂSPIЁЂUARTЁЂADCЁЂQEIЕШЭтВПНгПкЃЌОпгадкЦЌгВМўЕїЪдНгПкЃЌПЩНјаа32ЮЛећЪ§ЁЂ36ЮЛећЪ§МгЗжЪ§дЫЫуЃЌХфКЯCodeWarriorПЊЗЂЛЗОГЗЧГЃЪЪКЯгкЧЖШыЪНПЊЗЂЁЃ

Processor Expert(PE)ЪЧгЩНнПЫUNISЙЋЫОПЊЗЂЕФеыЖдFreeScaleЕЅЦЌЛњКЭDSPЕФЧЖШыЪНШэМўПЊЗЂАќЃЎЫќМЏГЩдкCodeWarriorПЊЗЂЛЗОГжаЁЃProcessor ExpertЬсЙЉСЫСЌНгЁЂЩњГЩЧЖШыЪНЯЕЭГЕФгВМўЁЂНгПкКЭЫуЗЈЕФЧ§ЖЏЃЌЖдCPUКЫЁЂаОЦЌМЏГЩНгПкЁЂащФтЩшБИКЭДПЫуЗЈНјааСЫЗтзА(ИУЗтзАБЛГЦЮЊЁАEmbedded BeansЁБ)ЃЌВЂАбетаЉЙІФмБфГЩЪєадЁЂЗНЗЈКЭЪТМўЃЌетгыУцЯђЖдЯѓЕФГЬађЩшМЦЗНЗЈЪЧвЛбљЕФЁЃгУЛЇдкНјааГЬађЩшМЦЪБЃЌЭЈЙ§ЕїгУProcessor ExpertЬсЙЉЕФИїжжBeanЃЌПЩвдЗНБуЕФЖдDSPФкКЫЁЂЭтВПжаЖЯЁЂDSPЕФЦЌЩЯЭтЩшМАГЬађЫљашЕФИїжжЭЈгУЫуЗЈНјааЩшжУЃЎЪЙгУЛЇжЛашЙизЂећИіЩшМЦЕФДДдьадВПЗжЃЌЖјВЛЪЧЛЈЗбДѓСПЪБМфШУаОЦЌе§ГЃЙЄзїЃЌДѓДѓЬсИпСЫЩњВњТЪЁЃБОЮФЕФFIRТЫВЈЦїЕФЪЕЯжЃЌОЭЪЧЛљгкProcessor ExpertЕФЁАDSP_Func_DFRЁБBeanКЭЁАDSP_MEMЁБBeanЕФЁЃЯжНЋОпЬхЕФЩшМЦЙ§ГЬУшЪіШчЯТЃК

НјШыCodeWarriorПЊЗЂЛЗОГЃЌбЁжаВЫЕЅЯюЁАProcessor Expertl| View| Bean SelectorЁБЃЌдкЕЏГіЕФЁАBean SelectorЁБДАПкжаЃЌбЁжаИКд№ФкДцЙмРэЕФЁАDSP_MEMЁБBeanКЭИКд№Ъ§зжаХКХДІРэЕФЁАDSP_Func_DFRЁБBeaflМгШыЙЄГЬЮФМўЃЌНЋЁАDSP_Func_DFRЁБBeanжаЕФЁАdfrl6FIRCreateЁБЁЂЁАdfrl6FIRЁБКЭЁАdfrl6FIRDestroyЁБЗНЗЈМгШыжїГЬађЁЃаоИФжїГЬађШчЯТЃК