基于DSP与FPGA的运动控制器设计

时间:11-27

来源:互联网

点击:

2.4 数字量输入输出接口模块

考虑到系统的可扩展性和DSP的GPIO口的数量,此运动控制器在DSP与FPGA上分别设计8路,共16路数字量输入输出。运动控制器的所有数字量输入输出信号均采用光电隔离处理,并对每一路信号进行相应的数字滤波处理,以消除噪声信号。数字量输入通道可以根据用户的要求自定义用途,用于零点、限位信号的输入等;数字量输出通道用于各轴方向、脉冲信号的输出以及一些外部设备的启停控制等。

3 系统软件设计

软件设计采用模块化设计方法,程序的总体结构采用以数据管理和位置速度控制为主,以I/O端口控制、逻辑控制、插补运算等为中断任务或子函数任务的形式。位置速度控制主要负责对实时运动状态的监控与调节;I/O端口控制主要负责扫描输入端口、设置输出端口等辅助性任务。

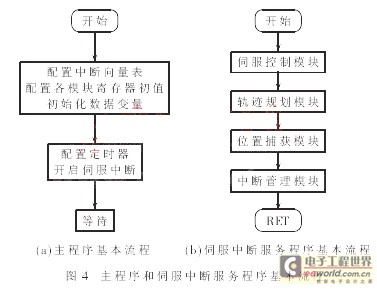

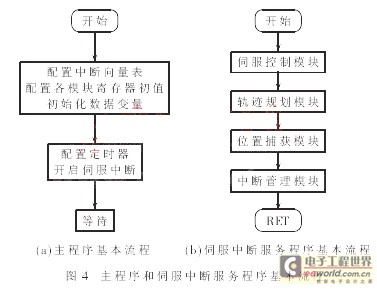

DSP控制程序主要由一个定时中断构成,主程序启动后,首先完成对TMS320F2812的初始化及系统的一些基本配置,并处于等待状态。运动控制功能是在伺服中断服务程序中实现的。主程序和伺服中断服务程序基本流程如图4所示。

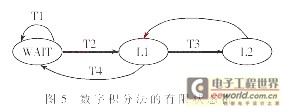

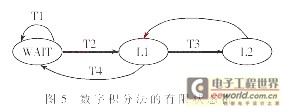

FPGA主要完成运动控制器的精插补功能,采用数字积分法进行插补。把数字积分法分为3个状态:(1)状态WAIT,等待插补信号;(2)状态L1,判断总的脉冲数;(3)状态L2,积分累加器累加一次,如有溢出,相应的输出脉冲为高电平,剩余累加次数减1。

数字积分法的有限状态机如图5所示。

触发条件T1:没有启动信号,下一状态为WAIT,无操作;触发条件T2:有启动信号,下一状态为L1,操作为初始化各寄存器,置忙信号;触发条件T3:剩余累加次数大于0,下一状态为L2,操作为各轴输出脉冲为低电平;触发条件T4:剩余累加次数为0,下一状态为WAIT,操作为各轴输出脉冲为低电平,清忙标志;无触发条件:下一状态为L1。

具体实现方法为:时序电路产生的插补脉冲作为此模块的累加脉冲,每累加1次,剩余累加次数减1。当剩余累加次数为0时,此次插补过程结束。

本文设计了一种通用型四轴伺服运动控制器,该运动控制器的结构设计可以模块化和易于扩展,这样可以满足用户的各种需求。在软件部分中,采用有限状态机的插补方法,在插补速度处理环节做了优化,使脉冲输出更加稳定。此设计采用了模块化思想,各电机可以单独控制,具有较为全面的运动控制功能、较高的控制精度和较快的反应速度,其性能可靠、硬件结构简单、价格便宜。

考虑到系统的可扩展性和DSP的GPIO口的数量,此运动控制器在DSP与FPGA上分别设计8路,共16路数字量输入输出。运动控制器的所有数字量输入输出信号均采用光电隔离处理,并对每一路信号进行相应的数字滤波处理,以消除噪声信号。数字量输入通道可以根据用户的要求自定义用途,用于零点、限位信号的输入等;数字量输出通道用于各轴方向、脉冲信号的输出以及一些外部设备的启停控制等。

3 系统软件设计

软件设计采用模块化设计方法,程序的总体结构采用以数据管理和位置速度控制为主,以I/O端口控制、逻辑控制、插补运算等为中断任务或子函数任务的形式。位置速度控制主要负责对实时运动状态的监控与调节;I/O端口控制主要负责扫描输入端口、设置输出端口等辅助性任务。

DSP控制程序主要由一个定时中断构成,主程序启动后,首先完成对TMS320F2812的初始化及系统的一些基本配置,并处于等待状态。运动控制功能是在伺服中断服务程序中实现的。主程序和伺服中断服务程序基本流程如图4所示。

FPGA主要完成运动控制器的精插补功能,采用数字积分法进行插补。把数字积分法分为3个状态:(1)状态WAIT,等待插补信号;(2)状态L1,判断总的脉冲数;(3)状态L2,积分累加器累加一次,如有溢出,相应的输出脉冲为高电平,剩余累加次数减1。

数字积分法的有限状态机如图5所示。

触发条件T1:没有启动信号,下一状态为WAIT,无操作;触发条件T2:有启动信号,下一状态为L1,操作为初始化各寄存器,置忙信号;触发条件T3:剩余累加次数大于0,下一状态为L2,操作为各轴输出脉冲为低电平;触发条件T4:剩余累加次数为0,下一状态为WAIT,操作为各轴输出脉冲为低电平,清忙标志;无触发条件:下一状态为L1。

具体实现方法为:时序电路产生的插补脉冲作为此模块的累加脉冲,每累加1次,剩余累加次数减1。当剩余累加次数为0时,此次插补过程结束。

本文设计了一种通用型四轴伺服运动控制器,该运动控制器的结构设计可以模块化和易于扩展,这样可以满足用户的各种需求。在软件部分中,采用有限状态机的插补方法,在插补速度处理环节做了优化,使脉冲输出更加稳定。此设计采用了模块化思想,各电机可以单独控制,具有较为全面的运动控制功能、较高的控制精度和较快的反应速度,其性能可靠、硬件结构简单、价格便宜。

DSP FPGA 步进电机 编码器 电路 嵌入式 电压 总线 Altera 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)