跟踪雷达的高速实时信号处理系统研究与设计

时间:11-26

来源:互联网

点击:

计

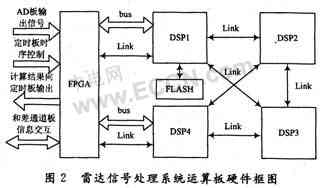

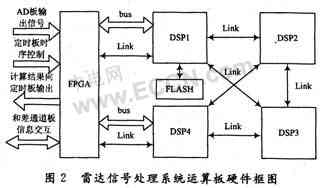

软件编程最重要的是软件处理的高效性,因此在设计信号处理软件时,要对每个模块的运算高效性做详细的分析。基于系统硬件构成,主要介绍对运算板2片DSP编程,完成对雷达回波信号的脉冲压缩、动目标检测(MTD)的运算实现。系统运算板中,DSP1通过并行总线使用DMA握手的方式读入中频解调后的和/差通道I、Q路数据,对数据进行脉冲压缩。后将处理的数据按波门通过链路口1发送给DSP2。DSP2对脉压数据经过32个周期的积累后,采用FFT实现窄带多普勒滤波器组,完成相参积累,并对结果进行求模、恒虚警处理,最后将处理结果通过链路口0传送给DSP4。

系统中需对32个通道(周期)的数据依次进行脉压后做相参积累和CFAR。为了实现并行处理,提高DSP处理速度,实现数据处理的连续性和等待数据传输时间的最小,在设计中将DMA传输与内核并行工作。具体做法是将DSP的输人RAM逻辑上分成两个大小相等的部分A和B。当外部数据向A(B)写数据时,DSP从B(A)取出上一批已经存人的数据,然后进行处理。其输出RAM设置过程同输入RAM。在实现中,DSP进行完初始化后,等待外部中断的到来。外部中断是告知DSP外部数据(双口RAM中)已经准备好,可以进行处理的握手信号。进人中断后,先启动DMA进行外部数据的输入,同时内核进行对上一批输人数据的运算,存入存储区,把上一批的结果送入下一运算模块。下面给出软件设计流程图,如图3所示。

脉冲压缩和MTD的实现都要用到FFT变换,为了在程序处理时最大可能地利用ADSP-TS101的总线资源,提高处理的速度,针对ADSP-TS101 6 Mb片上存储区分为M0,M1,M2三个区域及其各区域可具有独立总线的优点,将程序代码放在片上存储区M0,旋转因子及匹配滤波器系数放在M1,而输入及输出乒乓存储区设置到M2,这样在进行处理最耗时间的FFT/IFFT运算时,便可充分利用ADSP-TS101的指令并行优势。试验证明,这样设置比将所有参与运算的数据采用其他任何方式存放至少节省10%的指令周期。同时对FFT的旋转因子及脉压的匹配滤波器系数均事先放入存储区,进一步减少所耗费的指令周期,提高了效率。利用ADSP-TS101双运算模块,单指令多数据(SIMD)的特点,在求模和CFAR的设计中,同时进行两个距离单元的两个通道的并行处理,大大缩短了算法的实现时间。程序从CFAR算法实现的优化出发,可巧妙地避免重复的求和运算,减少算法的指令周期。

4 系统测试结果

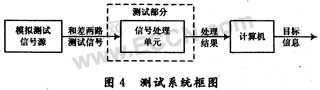

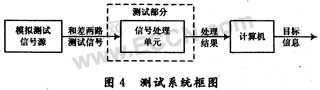

上述设计在实际中得到了验证,用模拟信号源产生脉冲重复周期为300μs的和差两路线性调频信号作为测试信号,然后将该信号送到被测系统中进行处理,最后通过串口将处理结果送到计算机中对目标信息进行观察验证。测试系统框图如图4所示。

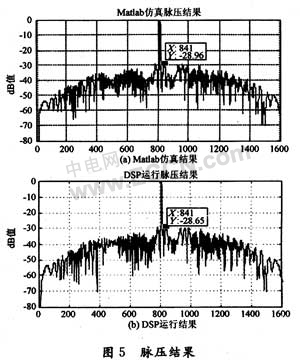

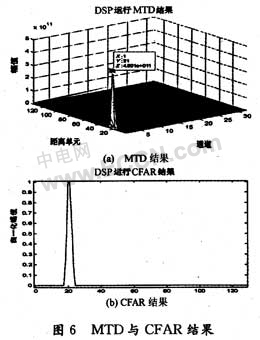

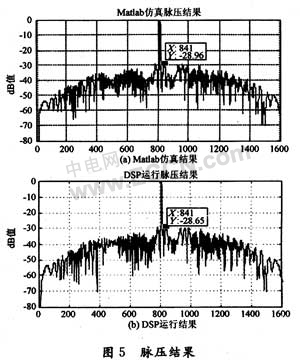

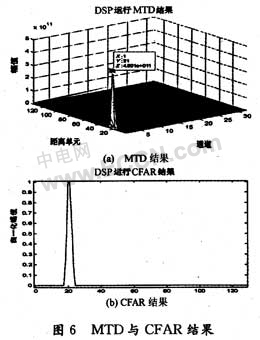

在测试部分中,AD板正交检波后以DMA握手方式将I,Q两路数据打包后送到DSP1中进行脉压,在一个脉冲发射周期内,外部数据DMA传输时间为40μs,脉压完成需198 μs,通过链路口传输数据所需时间约为5.36μs,该实现过程共需40+198+5.36=243.36μs。在实行了运算与数据传输的并行处理后实际处理时间缩小到约200μs,小于脉冲重复周期(300μs)。DSP2接收32通道数据需172 μs,相参积累的完成需118μs,求模和恒虚警的完成需336 μs,该实现过程共需172+118+336=626μs。同样,实行并行处理后实际处理时间缩小,远小于32个脉冲重复周期。由此看出,该系统满足时间要求。图5为测试一个目标的回波脉压后的结果,(a)为Matlab仿真脉压结果,(b)为DSP运行结果,二者误差很小,主副瓣比约为-28 dB。图6(a) 为MTD的结果,由x,y值可知目标fd为0,则速度为0,若每一个距离单元代表15 m,则目标在315 m。图6(b)为CFAR结果,可检测到目标在零通道的第21个距离单元处,与Matlab仿真结果相同。系统输入幅度不同的和差两路测试信号,其角误差为0.006 34°,得到的实测角误差为0.006 54°,误差很小,角跟踪精度高。这是由于系统对和差通道采用了相同的处理,减小了通道不一致性对测量的影响,提高了角跟踪精度。

5 结语

本文以跟踪雷达的处理系统设计为背景,利用ADSP-TS101的超高性能和内部资源,采用并行化和模块化设计,将硬件平台与软件编程相结合,实现了对雷达信号的高速实时处理。对脉冲压缩、MTD、CFAR的实现过程,特别是软件设计过程中的具体问题进行了详细的讨论,最后给出一组测试结果,验证了系统对目标距离跟踪、角度跟踪的可靠性和高效性。

软件编程最重要的是软件处理的高效性,因此在设计信号处理软件时,要对每个模块的运算高效性做详细的分析。基于系统硬件构成,主要介绍对运算板2片DSP编程,完成对雷达回波信号的脉冲压缩、动目标检测(MTD)的运算实现。系统运算板中,DSP1通过并行总线使用DMA握手的方式读入中频解调后的和/差通道I、Q路数据,对数据进行脉冲压缩。后将处理的数据按波门通过链路口1发送给DSP2。DSP2对脉压数据经过32个周期的积累后,采用FFT实现窄带多普勒滤波器组,完成相参积累,并对结果进行求模、恒虚警处理,最后将处理结果通过链路口0传送给DSP4。

系统中需对32个通道(周期)的数据依次进行脉压后做相参积累和CFAR。为了实现并行处理,提高DSP处理速度,实现数据处理的连续性和等待数据传输时间的最小,在设计中将DMA传输与内核并行工作。具体做法是将DSP的输人RAM逻辑上分成两个大小相等的部分A和B。当外部数据向A(B)写数据时,DSP从B(A)取出上一批已经存人的数据,然后进行处理。其输出RAM设置过程同输入RAM。在实现中,DSP进行完初始化后,等待外部中断的到来。外部中断是告知DSP外部数据(双口RAM中)已经准备好,可以进行处理的握手信号。进人中断后,先启动DMA进行外部数据的输入,同时内核进行对上一批输人数据的运算,存入存储区,把上一批的结果送入下一运算模块。下面给出软件设计流程图,如图3所示。

脉冲压缩和MTD的实现都要用到FFT变换,为了在程序处理时最大可能地利用ADSP-TS101的总线资源,提高处理的速度,针对ADSP-TS101 6 Mb片上存储区分为M0,M1,M2三个区域及其各区域可具有独立总线的优点,将程序代码放在片上存储区M0,旋转因子及匹配滤波器系数放在M1,而输入及输出乒乓存储区设置到M2,这样在进行处理最耗时间的FFT/IFFT运算时,便可充分利用ADSP-TS101的指令并行优势。试验证明,这样设置比将所有参与运算的数据采用其他任何方式存放至少节省10%的指令周期。同时对FFT的旋转因子及脉压的匹配滤波器系数均事先放入存储区,进一步减少所耗费的指令周期,提高了效率。利用ADSP-TS101双运算模块,单指令多数据(SIMD)的特点,在求模和CFAR的设计中,同时进行两个距离单元的两个通道的并行处理,大大缩短了算法的实现时间。程序从CFAR算法实现的优化出发,可巧妙地避免重复的求和运算,减少算法的指令周期。

4 系统测试结果

上述设计在实际中得到了验证,用模拟信号源产生脉冲重复周期为300μs的和差两路线性调频信号作为测试信号,然后将该信号送到被测系统中进行处理,最后通过串口将处理结果送到计算机中对目标信息进行观察验证。测试系统框图如图4所示。

在测试部分中,AD板正交检波后以DMA握手方式将I,Q两路数据打包后送到DSP1中进行脉压,在一个脉冲发射周期内,外部数据DMA传输时间为40μs,脉压完成需198 μs,通过链路口传输数据所需时间约为5.36μs,该实现过程共需40+198+5.36=243.36μs。在实行了运算与数据传输的并行处理后实际处理时间缩小到约200μs,小于脉冲重复周期(300μs)。DSP2接收32通道数据需172 μs,相参积累的完成需118μs,求模和恒虚警的完成需336 μs,该实现过程共需172+118+336=626μs。同样,实行并行处理后实际处理时间缩小,远小于32个脉冲重复周期。由此看出,该系统满足时间要求。图5为测试一个目标的回波脉压后的结果,(a)为Matlab仿真脉压结果,(b)为DSP运行结果,二者误差很小,主副瓣比约为-28 dB。图6(a) 为MTD的结果,由x,y值可知目标fd为0,则速度为0,若每一个距离单元代表15 m,则目标在315 m。图6(b)为CFAR结果,可检测到目标在零通道的第21个距离单元处,与Matlab仿真结果相同。系统输入幅度不同的和差两路测试信号,其角误差为0.006 34°,得到的实测角误差为0.006 54°,误差很小,角跟踪精度高。这是由于系统对和差通道采用了相同的处理,减小了通道不一致性对测量的影响,提高了角跟踪精度。

5 结语

本文以跟踪雷达的处理系统设计为背景,利用ADSP-TS101的超高性能和内部资源,采用并行化和模块化设计,将硬件平台与软件编程相结合,实现了对雷达信号的高速实时处理。对脉冲压缩、MTD、CFAR的实现过程,特别是软件设计过程中的具体问题进行了详细的讨论,最后给出一组测试结果,验证了系统对目标距离跟踪、角度跟踪的可靠性和高效性。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)