跟踪雷达的高速实时信号处理系统研究与设计

时间:11-26

来源:互联网

点击:

1 引 言

跟踪雷达是重要的现代雷达体制之一,可以对目标进行连续跟踪并获取目标航迹信息,以便进行瞄准计算。为了实现跟踪作用,要求波束的主瓣指向目标后,波束也必须连续跟随目标移动,以保证天线波束的主瓣指向不断地对准运动目标,并随时测定目标的瞬时坐标数据,以实现天线对目标的跟踪。随着导弹、火箭、人造卫星和宇航技术的发展,采用顺序比较波瓣法的圆锥扫描天线体制已经不能满足跟踪高速飞行器的要求。而单脉冲跟踪由于采用同时比较波瓣法,获取误差信号迅速,跟踪速度快,误差信号只与接收到的几个波束的回波脉冲幅度的相对值有关,不存在目标起伏干扰,因此角跟踪精度高,抗干扰能力强,而且获取目标距离信息的波束在天线轴向辐射最强,使得雷达的作用距离也远。 跟踪雷达对回波信号的特征提取和目标识别对数据的运算量和吞吐量都提出了特殊要求:即要求对和差通道正交两路回波信号同时进行采集,并实现高速传输、实时大容量处理。因此,其对处理性能的高要求使得大规模实时并行数字信号处理得到广泛应用。

文中介绍了基于多片ADSP-TS101芯片的某跟踪雷达的高性能处理系统的设计。系统利用DSP软件编程完成跟踪雷达信号处理算法的实现,设计时充分利用ADSP-TS101芯片的内部资源,发挥其性能,合理地解决了高速数据率问题,在存储雷达回波信号的同时,完成了对雷达回波信号高速实时的并行处理。

2 系统构成

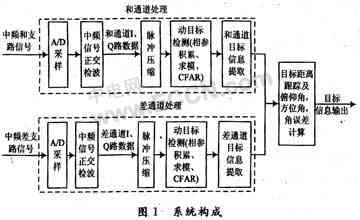

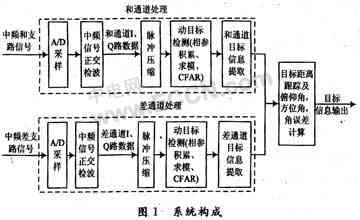

系统为振幅和差单脉冲跟踪雷达,在对目标的跟踪时,只收到一个回波脉冲即可得到目标的全部信息(距离、仰角和方位角)。为了实现距离、角度上的高精度跟踪,系统距离跟踪采用数字式距离跟踪,通过对雷达回波信号进行频域分析,利用回波信号的相移或频移与时延的对应关系得出距离信息。角度信息的提取和跟踪采用比幅式单脉冲。系统将回波信号在AD板中进行采样及中频正交检波后输出I,Q两路数据。在运算板中对数据做脉冲压缩处理后提取目标的距离信息,再通过动目标检测模块,进行相参积累、求模、恒虚警处理就可以实时、有效、准确地检测出目标的距离、速度以及相对于雷达的俯仰角、方位角和角误差,其中俯仰角、方位角与角误差是在差通道中分时处理获取。该系统构成如图1所示。

3 系统设计与实现

3.1硬件平台

跟踪雷达的处理系统硬件由A/D板、定时板、和差通道运算板组成。A/D板可通过A/D转换器完成对外部和差两路通道信号的模数转换,并且在FPGA内对数字信号进行正交中频检波,缓存并送出到运算板。从A/D采样精度和速度综合考虑,选择14 b的A/D转换器,其采样率可达到100 M,可以满足系统对12 b有效位数和40 MHz采样速率的要求。由于FPGA具有门阵列的高逻辑密度和高可靠性,使用FPGA实现正交中频检波具有更快的处理速度及良好的升级和扩展性。定时板是由一片AT91RM9200和一片FPGA构成的,其中AT91RM9200起控制作用,他通过从RS 422串口接收到外部主机的控制命令,对内部系统进行控制,同时根据从和差通道运算板传人的距离、速度、角误差等数据,产生相应的控制命令。而FPGA主要功能是进行高速数据传送,并由外部传人的差分时序定时信号,产生AD板、和差通道板相应的定时信号。运算板通过FPGA完成与外界信息交互以及对DSP的运算控制,利用4片DSP芯片完成雷达信号处理,后将运算完的数据再由FPGA回传到定时板,由此可见DSP在整个运算过程中起着核心的作用。

该系统的运算板将和差通道分开处理,和、差通道运算板采用同样的设计,两块运算板计算之后进行综合求取目标的方位信息。考虑到系统的实际功能及通用性和可扩展性,运算板采用1片FPGA与4片DSP组合构成,其组成框图如图2所示。基于实现功能和性能,所用FPGA为Cyclone II系列。而DSP采用AD公司新一代Tiger-SHARC结构的高性能定点/浮点数字信号处理器ADSP-TS101,他具有很强的数据处理能力和非常高的运算速度,片内有高达6 Mb的双口RlAM。另外,多条相互独立的总线和强大的通信能力,使其可以方便地构成性能更高的多处理器并行信号处理系统。运算板4片DSP以松耦合的链路方式进行无缝连接,每片DSP可单独工作。在硬件设计时,前一片DSP的FLAG0引脚连到下一片DSP的中断引脚IQR0,这样就可以用中断机制控制链路口的传输。每个DSP的其余中断引脚和FLAG引脚都与FPGA相连,从而不直接相连的DSP之间可以通过FPGA进行通信。DSP1通过FLASH加载程序,DSP2,DSP3,DSP4的程序通过链路口串行加载。加载完成后,程序进入等待状态,一直到中断来到时,开始运行主程序,完成处理任务。

3.2软件设

跟踪雷达是重要的现代雷达体制之一,可以对目标进行连续跟踪并获取目标航迹信息,以便进行瞄准计算。为了实现跟踪作用,要求波束的主瓣指向目标后,波束也必须连续跟随目标移动,以保证天线波束的主瓣指向不断地对准运动目标,并随时测定目标的瞬时坐标数据,以实现天线对目标的跟踪。随着导弹、火箭、人造卫星和宇航技术的发展,采用顺序比较波瓣法的圆锥扫描天线体制已经不能满足跟踪高速飞行器的要求。而单脉冲跟踪由于采用同时比较波瓣法,获取误差信号迅速,跟踪速度快,误差信号只与接收到的几个波束的回波脉冲幅度的相对值有关,不存在目标起伏干扰,因此角跟踪精度高,抗干扰能力强,而且获取目标距离信息的波束在天线轴向辐射最强,使得雷达的作用距离也远。 跟踪雷达对回波信号的特征提取和目标识别对数据的运算量和吞吐量都提出了特殊要求:即要求对和差通道正交两路回波信号同时进行采集,并实现高速传输、实时大容量处理。因此,其对处理性能的高要求使得大规模实时并行数字信号处理得到广泛应用。

文中介绍了基于多片ADSP-TS101芯片的某跟踪雷达的高性能处理系统的设计。系统利用DSP软件编程完成跟踪雷达信号处理算法的实现,设计时充分利用ADSP-TS101芯片的内部资源,发挥其性能,合理地解决了高速数据率问题,在存储雷达回波信号的同时,完成了对雷达回波信号高速实时的并行处理。

2 系统构成

系统为振幅和差单脉冲跟踪雷达,在对目标的跟踪时,只收到一个回波脉冲即可得到目标的全部信息(距离、仰角和方位角)。为了实现距离、角度上的高精度跟踪,系统距离跟踪采用数字式距离跟踪,通过对雷达回波信号进行频域分析,利用回波信号的相移或频移与时延的对应关系得出距离信息。角度信息的提取和跟踪采用比幅式单脉冲。系统将回波信号在AD板中进行采样及中频正交检波后输出I,Q两路数据。在运算板中对数据做脉冲压缩处理后提取目标的距离信息,再通过动目标检测模块,进行相参积累、求模、恒虚警处理就可以实时、有效、准确地检测出目标的距离、速度以及相对于雷达的俯仰角、方位角和角误差,其中俯仰角、方位角与角误差是在差通道中分时处理获取。该系统构成如图1所示。

3 系统设计与实现

3.1硬件平台

跟踪雷达的处理系统硬件由A/D板、定时板、和差通道运算板组成。A/D板可通过A/D转换器完成对外部和差两路通道信号的模数转换,并且在FPGA内对数字信号进行正交中频检波,缓存并送出到运算板。从A/D采样精度和速度综合考虑,选择14 b的A/D转换器,其采样率可达到100 M,可以满足系统对12 b有效位数和40 MHz采样速率的要求。由于FPGA具有门阵列的高逻辑密度和高可靠性,使用FPGA实现正交中频检波具有更快的处理速度及良好的升级和扩展性。定时板是由一片AT91RM9200和一片FPGA构成的,其中AT91RM9200起控制作用,他通过从RS 422串口接收到外部主机的控制命令,对内部系统进行控制,同时根据从和差通道运算板传人的距离、速度、角误差等数据,产生相应的控制命令。而FPGA主要功能是进行高速数据传送,并由外部传人的差分时序定时信号,产生AD板、和差通道板相应的定时信号。运算板通过FPGA完成与外界信息交互以及对DSP的运算控制,利用4片DSP芯片完成雷达信号处理,后将运算完的数据再由FPGA回传到定时板,由此可见DSP在整个运算过程中起着核心的作用。

该系统的运算板将和差通道分开处理,和、差通道运算板采用同样的设计,两块运算板计算之后进行综合求取目标的方位信息。考虑到系统的实际功能及通用性和可扩展性,运算板采用1片FPGA与4片DSP组合构成,其组成框图如图2所示。基于实现功能和性能,所用FPGA为Cyclone II系列。而DSP采用AD公司新一代Tiger-SHARC结构的高性能定点/浮点数字信号处理器ADSP-TS101,他具有很强的数据处理能力和非常高的运算速度,片内有高达6 Mb的双口RlAM。另外,多条相互独立的总线和强大的通信能力,使其可以方便地构成性能更高的多处理器并行信号处理系统。运算板4片DSP以松耦合的链路方式进行无缝连接,每片DSP可单独工作。在硬件设计时,前一片DSP的FLAG0引脚连到下一片DSP的中断引脚IQR0,这样就可以用中断机制控制链路口的传输。每个DSP的其余中断引脚和FLAG引脚都与FPGA相连,从而不直接相连的DSP之间可以通过FPGA进行通信。DSP1通过FLASH加载程序,DSP2,DSP3,DSP4的程序通过链路口串行加载。加载完成后,程序进入等待状态,一直到中断来到时,开始运行主程序,完成处理任务。

3.2软件设

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)