雷达目标回波数字模拟的TMS320C6201实现

时间:11-25

来源:互联网

点击:

1 引言

随着科技的发展和需求的不断提高,雷达系统变得越来越复杂,种类越来越多,对于复杂系统的设计、监测和维护变得越来越困难。正是在这样的情形下,使雷达模拟成为解决这一系列问题的有效手段,雷达系统模拟是数字技术和雷达技术相结合的产物,具有灵活性和经济性的优点。用软件建立符合用户需求的模型,区别于实物模型易受环境、物质、技术等条件的约束,具有良好的可控性。

雷达目标模拟是雷达系统模拟的重要组成部分。雷达目标信号可以视为发射波形经过延迟和多普勒频移后的复现波形,而且波形振幅受到天线方向图的双程波瓣调制,利用DSP的高速计算性能,可以实现目标回波信号的实时计算输出。

2 雷达目标回波的模拟

2.1 点目标回波信号

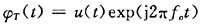

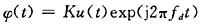

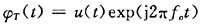

由于本文要模拟的雷达目标尺寸小于雷达分辨单元,因此将此目标视为点目标。设雷达发射信号表示为:

其中u(t)是复调制函数,f0是载频。

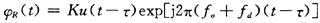

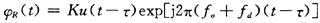

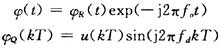

则目标回波的视频信号经过恒定多普勒理论简化后可表示为:

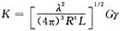

其中τ为回波信号的双程时延,fd为目标回波的多普勒频移,

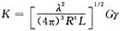

。

上式适用于v<<c,BT<<c/2v的点目标情况。

2.2 点目标回波的相干视频模拟

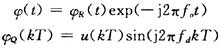

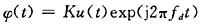

目标回波的相干视频信号是指目标回波信号经过雷达接收机的相干解调后输出的信号,可表示为:

上式没有考虑复反射系数γ引起的附加相移,在不考虑τ及由τ引起的附加固定相位项exp(-j2πfoτ),则上式可简化为:

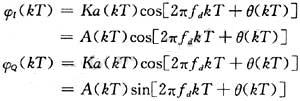

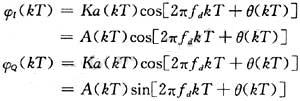

设相干脉冲雷达脉冲重复间隔为T,复调函数u(t)=a(t)exp[jθ(t)],则点目标回波的相干视频信号采样可用其正交分量表示为:

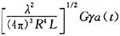

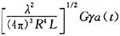

其中k表示采样号,θ(kT)为目标回波的初始相位,计算时可取为0,雷达点目标回波的全部信息都包含在这两个正交分量中。fd是该点目标的多普勒频移;a(kT)为雷达发射信号复调制函数的包罗函数,A(kT)=

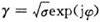

,γ为复反射系数,他与雷达截面积σ的关系为

,式中φ表示反射信号附加的相移。雷达截面积不仅与目标的大小、反射特性等特点有关,还受目标起伏特性的影响,此处雷达截面积采用swelling模型。λ为雷达波长,R为目标与雷达间的距离,G为受天线方向图影响的雷达单边功率增益,L为系统损耗因子。

因此,雷达回波的数字模拟主要是模拟目标的振幅A(kT)和多普勒频移fd。

2.3 天线的调制

单脉冲跟踪雷达采用和差波束来对目标进行跟踪,这种雷达系统的天线在一个角平面内有4个部分重叠的子波束,如图1所示。

4个子波束分别对接收到的目标回波进行幅度调制,可以得到4路信号,雷达将这4路信号进行和差处理,由差信号的大小可以得到目标位置(方位角、俯仰角)与天线中心指向的偏离误差,所以可以调整天线指向,实现对目标的跟踪。从波束截面图方向看,4个波束的中心位置如图1所示,其中原点为天线轴向,α轴为方向角方向,β轴为俯仰角方向,设由4个波束接收到的目标信号为A1,A2,A3,A4,那么和信号Σ,方位差信号Δα、俯仰差信号Δβ可以分别表示为:

Σ=A1+A2+A3+A4

Δα=A2+A4-A1-A3

Δβ=A1+A2-A3-A4

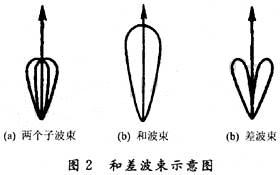

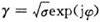

雷达按照上式对回波信号进行处理,也可以看作是和差方向图调制的结果。以两个波束为例,将两个子波束、和波束、差波束的方向图表示如图2所示。

要模拟点目标Σ,Δα,Δβ信号,最直接的办法是产生一路Σ信号,然后分别用图2所示的和、差波束方向图对数据进行调制,从而得到Σ,Δα,Δβ信号,但是必须采用多通道结构。如果换一个角度考虑,采用4个精密衰减器来模拟4个子波束的调制,得到4路信号后,再使用上式求出Σ,Δα,Δβ信号就可以只用一个目标信号通道,在数据输出时再使用衰减器来产生Σ,Δα,Δβ信号,目标的航迹在模拟器中可按主机传送的参数,由DSP实时计算得出。

3 目标轨迹的模拟

由于雷达获得的是离散的目标信号,即以一定时间间隔T获得的目标信息。当这个时间间隔足够小时,可以用直接段(或旋)去逼近目标的飞行轨迹,同时可以认为在这样一个微小的时间间隔内目标是匀加速运动的。因此任意飞行轨迹可视为直线运动和匀速空间圆周运动的组合。

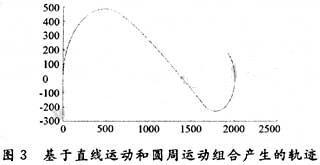

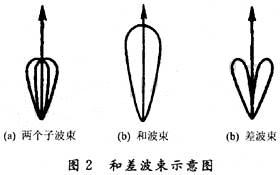

根据以上两种基本运动轨迹,可以组合出很多种复杂的运动轨迹,图3为用TMS320C6201实现的,基于直线和圆周运动进行组合而产生的一个复合轨迹。

4 基于TMS320C6201的实现

4.1 TMS320C6201简介

TMS320C6201是TI公司推出的一款定点数字信号处理器,CPU内含有8个并行处理的运算单元,指令长达256b,采用改进的哈佛结构,即程序存储器和数据存储器分开设置,程序存储器为512kb,或作为外部存储器的Cache。数据存储器为512kb,指令周期为5ns,时钟为200MHz。理想情况下,每次执行8条指令,故可以达到1600MIPS,芯片内集成外设包括:外存储器接口EMIF,主机口HPI,扩展总线XB,自举控制逻辑、多通道缓冲串口、定时、中断选择子、Power-down逻辑。软件设计可采用C语言,汇编语言和线性汇编语言等。

随着科技的发展和需求的不断提高,雷达系统变得越来越复杂,种类越来越多,对于复杂系统的设计、监测和维护变得越来越困难。正是在这样的情形下,使雷达模拟成为解决这一系列问题的有效手段,雷达系统模拟是数字技术和雷达技术相结合的产物,具有灵活性和经济性的优点。用软件建立符合用户需求的模型,区别于实物模型易受环境、物质、技术等条件的约束,具有良好的可控性。

雷达目标模拟是雷达系统模拟的重要组成部分。雷达目标信号可以视为发射波形经过延迟和多普勒频移后的复现波形,而且波形振幅受到天线方向图的双程波瓣调制,利用DSP的高速计算性能,可以实现目标回波信号的实时计算输出。

2 雷达目标回波的模拟

2.1 点目标回波信号

由于本文要模拟的雷达目标尺寸小于雷达分辨单元,因此将此目标视为点目标。设雷达发射信号表示为:

其中u(t)是复调制函数,f0是载频。

则目标回波的视频信号经过恒定多普勒理论简化后可表示为:

其中τ为回波信号的双程时延,fd为目标回波的多普勒频移,

。

上式适用于v<<c,BT<<c/2v的点目标情况。

2.2 点目标回波的相干视频模拟

目标回波的相干视频信号是指目标回波信号经过雷达接收机的相干解调后输出的信号,可表示为:

上式没有考虑复反射系数γ引起的附加相移,在不考虑τ及由τ引起的附加固定相位项exp(-j2πfoτ),则上式可简化为:

设相干脉冲雷达脉冲重复间隔为T,复调函数u(t)=a(t)exp[jθ(t)],则点目标回波的相干视频信号采样可用其正交分量表示为:

其中k表示采样号,θ(kT)为目标回波的初始相位,计算时可取为0,雷达点目标回波的全部信息都包含在这两个正交分量中。fd是该点目标的多普勒频移;a(kT)为雷达发射信号复调制函数的包罗函数,A(kT)=

,γ为复反射系数,他与雷达截面积σ的关系为

,式中φ表示反射信号附加的相移。雷达截面积不仅与目标的大小、反射特性等特点有关,还受目标起伏特性的影响,此处雷达截面积采用swelling模型。λ为雷达波长,R为目标与雷达间的距离,G为受天线方向图影响的雷达单边功率增益,L为系统损耗因子。

因此,雷达回波的数字模拟主要是模拟目标的振幅A(kT)和多普勒频移fd。

2.3 天线的调制

单脉冲跟踪雷达采用和差波束来对目标进行跟踪,这种雷达系统的天线在一个角平面内有4个部分重叠的子波束,如图1所示。

4个子波束分别对接收到的目标回波进行幅度调制,可以得到4路信号,雷达将这4路信号进行和差处理,由差信号的大小可以得到目标位置(方位角、俯仰角)与天线中心指向的偏离误差,所以可以调整天线指向,实现对目标的跟踪。从波束截面图方向看,4个波束的中心位置如图1所示,其中原点为天线轴向,α轴为方向角方向,β轴为俯仰角方向,设由4个波束接收到的目标信号为A1,A2,A3,A4,那么和信号Σ,方位差信号Δα、俯仰差信号Δβ可以分别表示为:

Σ=A1+A2+A3+A4

Δα=A2+A4-A1-A3

Δβ=A1+A2-A3-A4

雷达按照上式对回波信号进行处理,也可以看作是和差方向图调制的结果。以两个波束为例,将两个子波束、和波束、差波束的方向图表示如图2所示。

要模拟点目标Σ,Δα,Δβ信号,最直接的办法是产生一路Σ信号,然后分别用图2所示的和、差波束方向图对数据进行调制,从而得到Σ,Δα,Δβ信号,但是必须采用多通道结构。如果换一个角度考虑,采用4个精密衰减器来模拟4个子波束的调制,得到4路信号后,再使用上式求出Σ,Δα,Δβ信号就可以只用一个目标信号通道,在数据输出时再使用衰减器来产生Σ,Δα,Δβ信号,目标的航迹在模拟器中可按主机传送的参数,由DSP实时计算得出。

3 目标轨迹的模拟

由于雷达获得的是离散的目标信号,即以一定时间间隔T获得的目标信息。当这个时间间隔足够小时,可以用直接段(或旋)去逼近目标的飞行轨迹,同时可以认为在这样一个微小的时间间隔内目标是匀加速运动的。因此任意飞行轨迹可视为直线运动和匀速空间圆周运动的组合。

根据以上两种基本运动轨迹,可以组合出很多种复杂的运动轨迹,图3为用TMS320C6201实现的,基于直线和圆周运动进行组合而产生的一个复合轨迹。

4 基于TMS320C6201的实现

4.1 TMS320C6201简介

TMS320C6201是TI公司推出的一款定点数字信号处理器,CPU内含有8个并行处理的运算单元,指令长达256b,采用改进的哈佛结构,即程序存储器和数据存储器分开设置,程序存储器为512kb,或作为外部存储器的Cache。数据存储器为512kb,指令周期为5ns,时钟为200MHz。理想情况下,每次执行8条指令,故可以达到1600MIPS,芯片内集成外设包括:外存储器接口EMIF,主机口HPI,扩展总线XB,自举控制逻辑、多通道缓冲串口、定时、中断选择子、Power-down逻辑。软件设计可采用C语言,汇编语言和线性汇编语言等。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)