基于DSP和CPLD的低功耗多路数据处理系统

时间:11-25

来源:互联网

点击:

随着电子技术的应用和发展,数字信号处理内容日益复杂,同时,很多情况下要求整个系统具有低功耗的特点。为满足这种要求,DSP芯片设计技术也在向低功耗、高性能的方向发展。从处理速度来看,TMS320VC5502的运算能力已经达到了600MMACS,即每秒钟可以完成6亿次乘加运算。从功耗来看,TMS320VC5502内核电压只有1.26V,整个芯片的功耗也大大降低了。本文介绍了基于TMS320VC5502和CPLD XC95144的低功耗多路数据处理系统。

模拟信号的输入经过50Hz陷波电路(滤除工频干扰)和信号预选频电路。经过预处理的模拟信号作为ADC的模拟输入进行A/D变换,最后由DSP实现对数字信号的滤波处理。将CPLD和DSP技术相结合,利用CPLD编程的灵活性,来控制6路ADC的启动和停止,简化了整个硬件电路的设计,达到动态地选择采样通道的目的。同时将DSP处理后的数据发送到PC ,在PC上利用MATLAB和VC等工具对处理后的数据进行后端分析。本文主要介绍基于低功耗TMS320VC5502和CPLD的前端数据采集和处理系统。

ADS7805简介

ADS7805是一款具有16位量化精度的A/D转换芯片。它的基本组成结构包括16位精度的基于电容网络的逐次逼近型ADC、采样保持电路、时钟、对微处理器的接口和三态输出。ADS7805的最高采样速率为100kHz,模拟信号输入范围为-10V"+10V,5V单电源供电,最大耗散功率为100mW。

ADS7805为5V单电源供电,输出的数据位为‘1’时,电平值为5V,而DSP芯片的I/O电压采用的是3.3V逻辑电平,因此,还需要在ADS7805的数据输出端加上电平转换芯片,设计时选用了74ALVC164245,它可以将5V电平转换为3.3V,也可以将3.3V转换为5V。

硬件接口电路设计

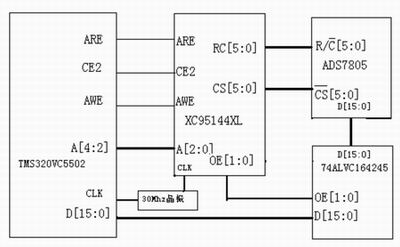

从硬件角度来看,DSP完成滤波运算的核心工作,而整个系统的控制核心是CPLD,DSP对6路A/D采样的操作是由CPLD产生控制信号,控制着ADS7805的采样触发信号、6个ADC的复用和解复用,以及5V转3.3V电压转换芯片74ALVC164245的选通等。CPLD和DSP的时钟输入采用30MHz有源晶振。CPLD、DSP、ADC和电平转换芯片之间的接口电路如图1所示。

图1 DSP、CPLD与ADC接口电路图

DSP利用片选信号、地址信号、读写使能信号向CPLD发出指令,CPLD根据DSP的指令向6个ADS7805发出控制信号,启动芯片进行采样并控制DSP完成对数据的读取。由于ADS7805输出的数据要通过电平转换芯片,CPLD还需要控制74ALVC164245芯片的选通和转换,就是图1中的OE[1:0]信号。因此,DSP必须向CPLD提供的控制信号包括CE2片选信号、ARE读使能信号和AWE写使能信号,当DSP读取A/D转换数据的时候,选通74ALVC164245进行电平转换,当ADC对模拟信号进行A/D转换时,不使能164245芯片,以免造成多路数据引起的数据总线冲突。由于有6个ADS7805,所以至少需要分配3根地址线信号(一般选为最低3位地址线引脚)区分这6个ADS7805,但3根地址线信号实际上可以用来表示8个地址,剩余的2个地址也可以利用起来,例如,对剩余的2个地址中的一个进行读操作可以视为DSP发出命令,用以启动ADS7805,这样就可以省去DSP和CPLD之间AWE信号的连接了。CPLD需要提供给ADS7805的信号包括片选信号CS[5:0]和数据读取/启动转换信号RC[5:0],此外,CPLD还要提供电平转换芯片的片选信号,并且需要接入一个时钟信号,用来给CPLD提供时序逻辑的同步时钟信号。

CPLD程序设计

根据ADS7805的工作原理和DSP读写特性,对CPLD进行编程来实现DSP对6个ADS7805的分时读取操作以及启动ADS7805的转换。

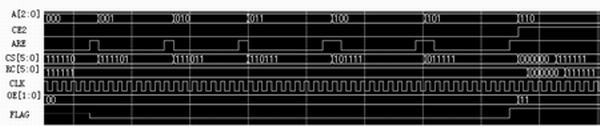

整个程序采用Verilog HDL语言设计。为了便于测试,增加了一个FLAG标志信号,当FLAG为低的时候,说明DSP正在读取ADS7805转换过的数据。当FLAG为高的时候,说明ADS7805正在进行新一轮的转换。程序设计的重点在于启动ADS7805的新一轮采样,而ADS7805启动采样需要CS和RC同时为低且保持40ns。当DSP读完6个ADC的数据后就要启动新一轮采样。当对第6个ADS7805的读取操作完成后,FLAG标志位被拉高并利用计数器进行记时,输入的时钟频率是30MHz。因此需要让RC[5:0]和CS[5:0]输出信号至少保持2个时钟周期的低电平才能成功地启动下一次A/D转换。根据系统的要求,CPLD程序主要分3个always块。

第一个模块利用DSP的CE2地址空间选择信号、地址线A[4:2]、ARE读信号以及定义的3位计数器cnt[2:0]作为触发信号。当CE2和ARE都为低时,根据DSP的A[4:2]选择6个中的一个进行读取,其他5个都被禁止,这时,RC[5:0]应该均为高。如果A[4:2]=000,那么CS[5:0]=111110,开始读第一个ADS7805的数据到DSP。为了防止数据丢失,在读数据的时候,RC[5:0]应该始终保持为高,因为如果CS[5:0]和RC[5:0]信号中同一位均保持为低超过40ns,就会启动一次新的采样,这样会造成没有被读的ADS7805产生一次新的采样而丢掉之前转换的数据,对整个系统的结果造成很大的影响。读完第6个ADC以后,在ARE的上升沿将FLAG标志拉高,这时计数器开始记数,根据记数器的数值,当2

根据以上设计思路,成功地做到了对6路信号的采样和读取控制,达到了预期的效果。仿真波形如图2所示。

图2 CPLD仿真波形图

模拟信号的输入经过50Hz陷波电路(滤除工频干扰)和信号预选频电路。经过预处理的模拟信号作为ADC的模拟输入进行A/D变换,最后由DSP实现对数字信号的滤波处理。将CPLD和DSP技术相结合,利用CPLD编程的灵活性,来控制6路ADC的启动和停止,简化了整个硬件电路的设计,达到动态地选择采样通道的目的。同时将DSP处理后的数据发送到PC ,在PC上利用MATLAB和VC等工具对处理后的数据进行后端分析。本文主要介绍基于低功耗TMS320VC5502和CPLD的前端数据采集和处理系统。

ADS7805简介

ADS7805是一款具有16位量化精度的A/D转换芯片。它的基本组成结构包括16位精度的基于电容网络的逐次逼近型ADC、采样保持电路、时钟、对微处理器的接口和三态输出。ADS7805的最高采样速率为100kHz,模拟信号输入范围为-10V"+10V,5V单电源供电,最大耗散功率为100mW。

ADS7805为5V单电源供电,输出的数据位为‘1’时,电平值为5V,而DSP芯片的I/O电压采用的是3.3V逻辑电平,因此,还需要在ADS7805的数据输出端加上电平转换芯片,设计时选用了74ALVC164245,它可以将5V电平转换为3.3V,也可以将3.3V转换为5V。

硬件接口电路设计

从硬件角度来看,DSP完成滤波运算的核心工作,而整个系统的控制核心是CPLD,DSP对6路A/D采样的操作是由CPLD产生控制信号,控制着ADS7805的采样触发信号、6个ADC的复用和解复用,以及5V转3.3V电压转换芯片74ALVC164245的选通等。CPLD和DSP的时钟输入采用30MHz有源晶振。CPLD、DSP、ADC和电平转换芯片之间的接口电路如图1所示。

图1 DSP、CPLD与ADC接口电路图

DSP利用片选信号、地址信号、读写使能信号向CPLD发出指令,CPLD根据DSP的指令向6个ADS7805发出控制信号,启动芯片进行采样并控制DSP完成对数据的读取。由于ADS7805输出的数据要通过电平转换芯片,CPLD还需要控制74ALVC164245芯片的选通和转换,就是图1中的OE[1:0]信号。因此,DSP必须向CPLD提供的控制信号包括CE2片选信号、ARE读使能信号和AWE写使能信号,当DSP读取A/D转换数据的时候,选通74ALVC164245进行电平转换,当ADC对模拟信号进行A/D转换时,不使能164245芯片,以免造成多路数据引起的数据总线冲突。由于有6个ADS7805,所以至少需要分配3根地址线信号(一般选为最低3位地址线引脚)区分这6个ADS7805,但3根地址线信号实际上可以用来表示8个地址,剩余的2个地址也可以利用起来,例如,对剩余的2个地址中的一个进行读操作可以视为DSP发出命令,用以启动ADS7805,这样就可以省去DSP和CPLD之间AWE信号的连接了。CPLD需要提供给ADS7805的信号包括片选信号CS[5:0]和数据读取/启动转换信号RC[5:0],此外,CPLD还要提供电平转换芯片的片选信号,并且需要接入一个时钟信号,用来给CPLD提供时序逻辑的同步时钟信号。

CPLD程序设计

根据ADS7805的工作原理和DSP读写特性,对CPLD进行编程来实现DSP对6个ADS7805的分时读取操作以及启动ADS7805的转换。

整个程序采用Verilog HDL语言设计。为了便于测试,增加了一个FLAG标志信号,当FLAG为低的时候,说明DSP正在读取ADS7805转换过的数据。当FLAG为高的时候,说明ADS7805正在进行新一轮的转换。程序设计的重点在于启动ADS7805的新一轮采样,而ADS7805启动采样需要CS和RC同时为低且保持40ns。当DSP读完6个ADC的数据后就要启动新一轮采样。当对第6个ADS7805的读取操作完成后,FLAG标志位被拉高并利用计数器进行记时,输入的时钟频率是30MHz。因此需要让RC[5:0]和CS[5:0]输出信号至少保持2个时钟周期的低电平才能成功地启动下一次A/D转换。根据系统的要求,CPLD程序主要分3个always块。

第一个模块利用DSP的CE2地址空间选择信号、地址线A[4:2]、ARE读信号以及定义的3位计数器cnt[2:0]作为触发信号。当CE2和ARE都为低时,根据DSP的A[4:2]选择6个中的一个进行读取,其他5个都被禁止,这时,RC[5:0]应该均为高。如果A[4:2]=000,那么CS[5:0]=111110,开始读第一个ADS7805的数据到DSP。为了防止数据丢失,在读数据的时候,RC[5:0]应该始终保持为高,因为如果CS[5:0]和RC[5:0]信号中同一位均保持为低超过40ns,就会启动一次新的采样,这样会造成没有被读的ADS7805产生一次新的采样而丢掉之前转换的数据,对整个系统的结果造成很大的影响。读完第6个ADC以后,在ARE的上升沿将FLAG标志拉高,这时计数器开始记数,根据记数器的数值,当2

根据以上设计思路,成功地做到了对6路信号的采样和读取控制,达到了预期的效果。仿真波形如图2所示。

图2 CPLD仿真波形图

电子 DSP 电压 CPLD 电路 ADC 电容 电路图 总线 Verilog 仿真 滤波器 电流 相关文章:

- 利用蓝牙技术和远程信息控制单元实现汽车诊断(11-13)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)

- 汽车网络的分类及发展趋向(11-13)

- 多核嵌入式处理技术推动汽车技术发展(11-18)

- CAN总线的客车轻便换档系统设计与实现(02-13)

- 高性能嵌入式ARM MPU在医疗电子系统中的设计应用(05-12)