FPGA-DSP瞄准目标:用得起的DSP性能

时间:09-21

来源:互联网

点击:

FPGA-DSP性能揭秘

在无线基站等高性能 DSP应用中,考虑将 FPGA 用作处理引擎者日益增多。在这些应用中,FPGA 既可与 DSP处理器一争高下,亦可与之比翼齐飞。

有了更多选择,就意味着系统设计者有必要了解高端FPGA的信号处理性能,其中既包括FPGA之间的性能对比,也包括与高端 DSP 处理器的性能对比。遗憾的是,最常用的性能数字非但有失可靠、含混不清,而且常常是矛盾百出。

例如,因为 DSP 应用常常在很大程度上依赖乘法累加 (MAC) 运算,所以 DSP 处理器和 FPGA 供应商有时用每秒MAC运算次数的峰值作为简单度量来比较数字信号处理性能。但 MAC流量对于 FPGA 和 DSP 二者都同样是糟糕的性能预测值。我们来分析几个原因。

简单度量显露缺憾

FPGA的MAC性能数字常常假设硬连线 DSP 器件是在其可能的最高时钟速率下工作。但实际上,典型FPGA设计的工作速率都比较低。另外,使用硬连线器件并非在FPGA上执行MAC运算的唯一方法,您可以使用可编程逻辑资源和分布式算法获得更大的MAC流量。与仅使用硬连线器件相比,这种方法可产生更高的MAC流量。

另一个考虑因素是,除了MAC运算,典型的DSP应用还依赖许多其他运算方法。例如,Viterbi解码就是在完全不使用MAC的电信应用中使用的一种关键 DSP 算法。

另一种评价信号处理性能的方法是使用常用的DSP函数,如FIR滤波器函数。但此方法也有缺点。其中一个问题是,每个供应商在使用这样的函数时,实现方法往往不同,他们可能使用不同的数据宽度、不同的算法或不同的实现参数(如延时参数)。这意味着不同供应商的结果通常是不可比的。

再者,较小的核函数通常对FPGA基准测试无效,因为在完整 FPGA 应用中实现函数的方法常常与单独实现该函数的方法大相径庭。相反,对于处理器来说,这些小型基准测试往往颇能预测DSP应用的总体性能。最后,处理器或 FPGA 供应商实施的基准测试常常缺乏独立验证,这使工程师们很难在器件之间做出自信的比较。

独立基准测试填补空白

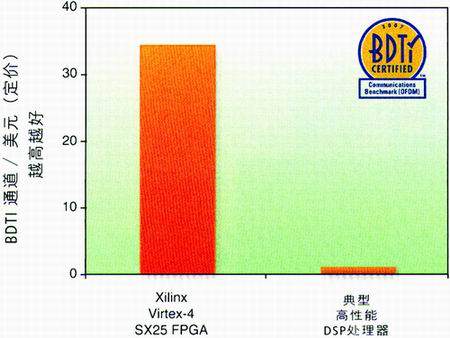

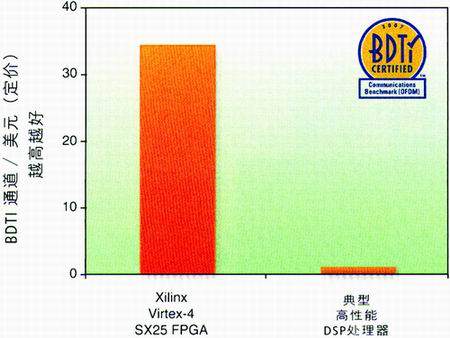

最近,BDTI 使用 BDTI 通讯基准测试 (OFDM) 对若干新型高性能 FPGA 和 DSP 处理器进行了评价,此报告结论在 DSP 系统设计者中引起了极大关注。该报告包括两套基准测试结果:高容量结果(为支持每芯片最大通道数而优化)和低成本结果(针对每通道最低成本而优化)。图1所示为一个 Xilinx Virtex-4 SX25 FPGA 和一个典型高性能 DSP处理器的规范化低成本结果。

图1 BDTI通讯基准测试(OFDM)BDTI验证的性价比优化结果

此基准测试结果显示,Virtex-4 SX25器件的成本效益比典型的高性能 DSP处理器高出一个数量级。

当然,仅基准测试结果还不足以回答是否在新系统设计中使用 FPGA 或选择哪种 FPGA的问题。设计者必须了解处理引擎的选择对开发流程、实现难度和系统设计有何影响。

Sparten-DSP:瞄准用得起的DSP性能

在 DSP 市场中,并不总是那些最快的、最便宜的或最节能的处理器才能胜出:对于每个范畴都能应付自如的平台,才能稳操胜券。在高密度Virtex系列之外,Xilinx今年4月第一次推出了基于低成本系列的Spartan-3A DSP。Spartan-3A DSP实现了32GMAC/s、高达2200Mbps的内存带宽和更小的体积。对于以下种种应用来说,充分满足了其要求:单通道微微蜂窝无线基站中的数字前端(DFE)和基带解决方案;军用移动软件定义无线电(SDR);超声波系统;驾驶员助手/媒体系统;高清晰度视频;智能IP摄像机。

Spartan-3A DSP不仅拥有高达53712个逻辑单元、2268Kb的Block RAM、373 Kb的分布式 RAM、519只I/O 引脚、安全专用 DeviceDNA、新开发的休眠/悬挂式电源管理功能,提供了足够的集成空间,使得价位/性能/功耗的比率降至更低。除此之外,还有基于 FPGA的 DSP 解决方案所固有的优点:通过设计上的灵活性和更快的上市时间实现低风险。

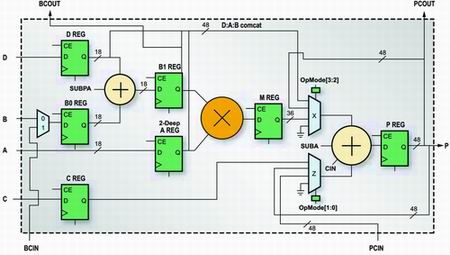

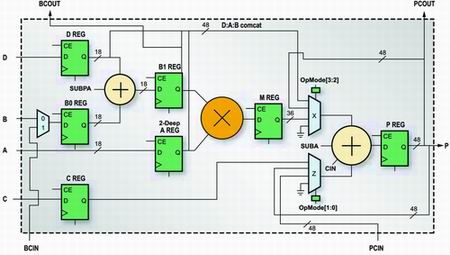

Spartan-3A DSP的核心是XtremeDSP DSP48 Slice的一个修订版本—DSP48A。DSP48 Slice最初是随着Virtex-4 FPGA的发布而推出的,它具有“面向应用的组合模块”(ASMBL) 架构,能提供 Virtex DSP 器件中的 DSP 功能。这些 XtremeDSP Slice 使得设计者们能够针对复杂的挑战实施解决方案,例如:数百个IF(中频)到基带下变频转换通道,用于3G传输频谱系统的128倍芯片速率处理和高清晰度 H .264 及 MPEG-4 编码/解码算法。

这种 DSP48 Slice 支持许多独立功能,包括:乘法器、MAC、乘法器带加法器、3输入加法器、桶式移位器、宽总线多路复用器、量级比较器或宽计数器。这种架构也支持将多个 DSP48 Slice连在一起形成宽数学函数、DSP 过滤器和复杂算术函数,而无需使用总体 FPGA 架构,从而降低了功耗,同时达到高的性能和芯片使用率。

为降低成本,DSP48A Slice去掉了舍入模式、17 位移位器和 3 输入加法器。如有需要,您可以在 FPGA 架构中实现这些功能。DSP48A Slice还有两项额外增强功能:一个独立控制的C-port和一个预加器。独立的C-port在实施 DSP 算法时提供了更高的灵活性。预加器则提高了普通 DSP 过滤器 和 FFT 的密度。特别值得一提的是,预加器可以用来减少所需 DSP48A Slice 的数量:对对称 FIR 过滤器来说,可减少50%;对FFT算法,可减少25%。在Spartan-3A DSP 平台上,优化过的DSP48A Slice在最慢的速度级别上也达到了 250 MHz 的运行频率。

在无线基站等高性能 DSP应用中,考虑将 FPGA 用作处理引擎者日益增多。在这些应用中,FPGA 既可与 DSP处理器一争高下,亦可与之比翼齐飞。

有了更多选择,就意味着系统设计者有必要了解高端FPGA的信号处理性能,其中既包括FPGA之间的性能对比,也包括与高端 DSP 处理器的性能对比。遗憾的是,最常用的性能数字非但有失可靠、含混不清,而且常常是矛盾百出。

例如,因为 DSP 应用常常在很大程度上依赖乘法累加 (MAC) 运算,所以 DSP 处理器和 FPGA 供应商有时用每秒MAC运算次数的峰值作为简单度量来比较数字信号处理性能。但 MAC流量对于 FPGA 和 DSP 二者都同样是糟糕的性能预测值。我们来分析几个原因。

简单度量显露缺憾

FPGA的MAC性能数字常常假设硬连线 DSP 器件是在其可能的最高时钟速率下工作。但实际上,典型FPGA设计的工作速率都比较低。另外,使用硬连线器件并非在FPGA上执行MAC运算的唯一方法,您可以使用可编程逻辑资源和分布式算法获得更大的MAC流量。与仅使用硬连线器件相比,这种方法可产生更高的MAC流量。

另一个考虑因素是,除了MAC运算,典型的DSP应用还依赖许多其他运算方法。例如,Viterbi解码就是在完全不使用MAC的电信应用中使用的一种关键 DSP 算法。

另一种评价信号处理性能的方法是使用常用的DSP函数,如FIR滤波器函数。但此方法也有缺点。其中一个问题是,每个供应商在使用这样的函数时,实现方法往往不同,他们可能使用不同的数据宽度、不同的算法或不同的实现参数(如延时参数)。这意味着不同供应商的结果通常是不可比的。

再者,较小的核函数通常对FPGA基准测试无效,因为在完整 FPGA 应用中实现函数的方法常常与单独实现该函数的方法大相径庭。相反,对于处理器来说,这些小型基准测试往往颇能预测DSP应用的总体性能。最后,处理器或 FPGA 供应商实施的基准测试常常缺乏独立验证,这使工程师们很难在器件之间做出自信的比较。

独立基准测试填补空白

最近,BDTI 使用 BDTI 通讯基准测试 (OFDM) 对若干新型高性能 FPGA 和 DSP 处理器进行了评价,此报告结论在 DSP 系统设计者中引起了极大关注。该报告包括两套基准测试结果:高容量结果(为支持每芯片最大通道数而优化)和低成本结果(针对每通道最低成本而优化)。图1所示为一个 Xilinx Virtex-4 SX25 FPGA 和一个典型高性能 DSP处理器的规范化低成本结果。

图1 BDTI通讯基准测试(OFDM)BDTI验证的性价比优化结果

此基准测试结果显示,Virtex-4 SX25器件的成本效益比典型的高性能 DSP处理器高出一个数量级。

当然,仅基准测试结果还不足以回答是否在新系统设计中使用 FPGA 或选择哪种 FPGA的问题。设计者必须了解处理引擎的选择对开发流程、实现难度和系统设计有何影响。

Sparten-DSP:瞄准用得起的DSP性能

在 DSP 市场中,并不总是那些最快的、最便宜的或最节能的处理器才能胜出:对于每个范畴都能应付自如的平台,才能稳操胜券。在高密度Virtex系列之外,Xilinx今年4月第一次推出了基于低成本系列的Spartan-3A DSP。Spartan-3A DSP实现了32GMAC/s、高达2200Mbps的内存带宽和更小的体积。对于以下种种应用来说,充分满足了其要求:单通道微微蜂窝无线基站中的数字前端(DFE)和基带解决方案;军用移动软件定义无线电(SDR);超声波系统;驾驶员助手/媒体系统;高清晰度视频;智能IP摄像机。

Spartan-3A DSP不仅拥有高达53712个逻辑单元、2268Kb的Block RAM、373 Kb的分布式 RAM、519只I/O 引脚、安全专用 DeviceDNA、新开发的休眠/悬挂式电源管理功能,提供了足够的集成空间,使得价位/性能/功耗的比率降至更低。除此之外,还有基于 FPGA的 DSP 解决方案所固有的优点:通过设计上的灵活性和更快的上市时间实现低风险。

Spartan-3A DSP的核心是XtremeDSP DSP48 Slice的一个修订版本—DSP48A。DSP48 Slice最初是随着Virtex-4 FPGA的发布而推出的,它具有“面向应用的组合模块”(ASMBL) 架构,能提供 Virtex DSP 器件中的 DSP 功能。这些 XtremeDSP Slice 使得设计者们能够针对复杂的挑战实施解决方案,例如:数百个IF(中频)到基带下变频转换通道,用于3G传输频谱系统的128倍芯片速率处理和高清晰度 H .264 及 MPEG-4 编码/解码算法。

这种 DSP48 Slice 支持许多独立功能,包括:乘法器、MAC、乘法器带加法器、3输入加法器、桶式移位器、宽总线多路复用器、量级比较器或宽计数器。这种架构也支持将多个 DSP48 Slice连在一起形成宽数学函数、DSP 过滤器和复杂算术函数,而无需使用总体 FPGA 架构,从而降低了功耗,同时达到高的性能和芯片使用率。

为降低成本,DSP48A Slice去掉了舍入模式、17 位移位器和 3 输入加法器。如有需要,您可以在 FPGA 架构中实现这些功能。DSP48A Slice还有两项额外增强功能:一个独立控制的C-port和一个预加器。独立的C-port在实施 DSP 算法时提供了更高的灵活性。预加器则提高了普通 DSP 过滤器 和 FFT 的密度。特别值得一提的是,预加器可以用来减少所需 DSP48A Slice 的数量:对对称 FIR 过滤器来说,可减少50%;对FFT算法,可减少25%。在Spartan-3A DSP 平台上,优化过的DSP48A Slice在最慢的速度级别上也达到了 250 MHz 的运行频率。

FPGA DSP 滤波器 Xilinx 无线电 电源管理 总线 比较器 电路 硬件工程师 仿真 VHDL Verilog 相关文章:

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)