低功耗模式下微控制器时钟配置应用

时间:09-18

来源:互联网

点击:

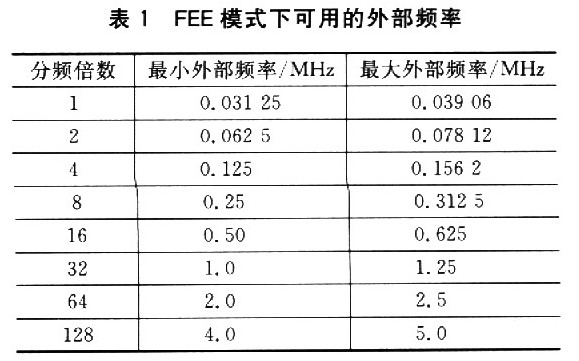

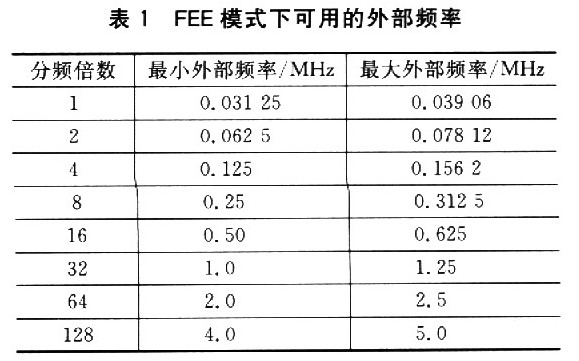

2.3 FEE模式

FEE(FLL启用、选用外部参考时钟)模式下,锁频环处于运行状态,可驱动CPU和总线时钟,采用外部时钟源作为其参考时钟。为了让系统正常运行,锁频环的输出要求在16 MHz~20MHz之间。这样外部参考时钟会受到限制。内部时钟源模块有一个参考时钟分频器,可用于降低外部参考时钟的频率,表l列出了根据分频设置所能容许的外部频率。

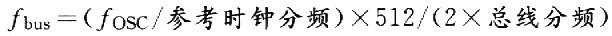

FEI模式下的总线频率可按下式计算:

2.4 FBI和FBILP模式

FBI(锁频环旁路、内部参考时钟)和FBILP(锁频环旁路、内部参考时钟低功耗)模式均旁路锁频环,而直接采用内部时钟源生成时钟信号。不同之处在于,FBI模式让锁频环保持运行,而FBILP模式则关闭锁频环,从而降低更多的功耗。FBILP是通过配置为FBI并设定ICS控制寄存器2(ICSC2)中的LP位来启动的。

采用FBI而非FBILP的原因之一,是为了采用背景调试模式(BDM);其二,当需要切换到FEI时可节省锁频环的锁定时间。锁频环必须处于运行状态才能给背景调试模式通信提供一个高速时钟源。锁定时间的最大规定值为lms,通常需要约500μs。关闭锁频环可节省大约220~310μA的电流。

2.5 FBE和FBELP模式

FBE(FLL旁路、外部参考时钟)和FBELP(FLL旁路、外部参考时钟低功耗)模式与2.4小节中的FBI和FBILP模式类似。除了是用外部时钟产生时钟源,而不是用内部时钟源外,FLL仍被旁路,LP位则在未启动BDM时关闭锁频环。

3 低功耗模式中的内部时钟源

3.1 停止1和停止2模式

当MCU进入停止1或停止2模式时,内部时钟源总是被置于关断模式。因此,执行STOP指令时。内部时钟模块所处的模式无关紧要,也不会影响处于停止l和停止2期间的功耗。

由于停止1和停止2模式均导致MCU在停止恢复时执行上电复位,因此,复位后的模式总是FEI,总线分频被设置为2分频,产生大约4MHz的总线时钟。内部时钟调整位ICSTRM将被重置为0x80,微调寄存器的FTRIM位会被清零,所以如果要采用内部参考时钟,则须对它进行重新校准;如果调整值已保存在Flash存储器中,则须把保存值重新载入寄存器。

3.2 停止3模式

当进入停止3模式后,内部时钟源的大部分(包括锁频环)将关闭。内部时钟源在执行STOP指令时所处的模式不会影响停止3的功耗。但是,ICS的两个控制位,IREFSTEN和EREFSTEN会影响停止3的电流。若置1,则IREFSTEN可使IRC在停止3模式中保持启用状态;

同样,若置1,则EREFSTEN可使OSC在停止3模式中保持启用状态。将IREFSTEN置位,将产生约100μA的停止3电流;将EREFSTEN置位,将对停止3电流产生不同的影响,取决于OSC的频率和设置。

如果因复位而退出停止3,ICS会像停止1或停止2的恢复那样回复至FEI模式。不同之处是调整值不会重置,除非发生了上电复位。

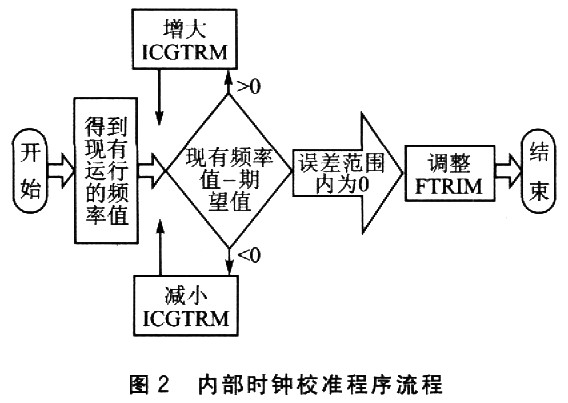

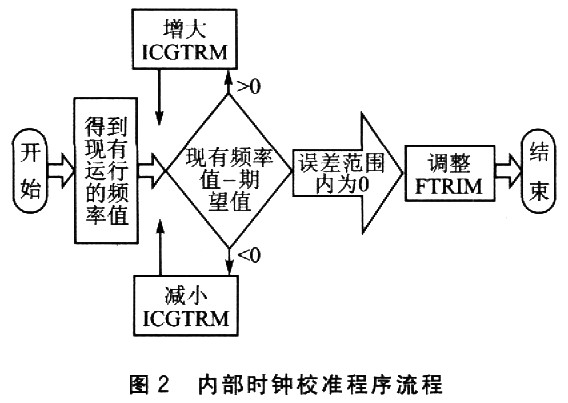

4 内部时钟校准

系统经过上电复位后,ICSTRM将被重置为0x80,FTRIM位会被清零。如果要采用内部参考时钟,则需要对其进行重新校准。增大ICSTRM的值,将降低参考时钟频率;相反,减小ICSTRM的值,将提高参考时钟频率。FTRIM置0或1会更精细地对频率进行调整。根据这个原理,内部时钟校准的程序流程框图如图2所示。

关于具体的程序町根据参考文献编制。待ICGTRM和FTRIM选定后,可存入微控制器的Flash中,下次上电复位后直接读取数值载入即可。

结语

恰当地运用时钟设置,对于降低微控制器的功耗有很大帮助。在微控制器各种不同的运行模式下,时钟都有不同的配置方法与之配合。同样的方案也适用于功能类似的微控制器。巧妙地运用各种时钟模式,可以使系统的功耗最低。

FEE(FLL启用、选用外部参考时钟)模式下,锁频环处于运行状态,可驱动CPU和总线时钟,采用外部时钟源作为其参考时钟。为了让系统正常运行,锁频环的输出要求在16 MHz~20MHz之间。这样外部参考时钟会受到限制。内部时钟源模块有一个参考时钟分频器,可用于降低外部参考时钟的频率,表l列出了根据分频设置所能容许的外部频率。

FEI模式下的总线频率可按下式计算:

2.4 FBI和FBILP模式

FBI(锁频环旁路、内部参考时钟)和FBILP(锁频环旁路、内部参考时钟低功耗)模式均旁路锁频环,而直接采用内部时钟源生成时钟信号。不同之处在于,FBI模式让锁频环保持运行,而FBILP模式则关闭锁频环,从而降低更多的功耗。FBILP是通过配置为FBI并设定ICS控制寄存器2(ICSC2)中的LP位来启动的。

采用FBI而非FBILP的原因之一,是为了采用背景调试模式(BDM);其二,当需要切换到FEI时可节省锁频环的锁定时间。锁频环必须处于运行状态才能给背景调试模式通信提供一个高速时钟源。锁定时间的最大规定值为lms,通常需要约500μs。关闭锁频环可节省大约220~310μA的电流。

2.5 FBE和FBELP模式

FBE(FLL旁路、外部参考时钟)和FBELP(FLL旁路、外部参考时钟低功耗)模式与2.4小节中的FBI和FBILP模式类似。除了是用外部时钟产生时钟源,而不是用内部时钟源外,FLL仍被旁路,LP位则在未启动BDM时关闭锁频环。

3 低功耗模式中的内部时钟源

3.1 停止1和停止2模式

当MCU进入停止1或停止2模式时,内部时钟源总是被置于关断模式。因此,执行STOP指令时。内部时钟模块所处的模式无关紧要,也不会影响处于停止l和停止2期间的功耗。

由于停止1和停止2模式均导致MCU在停止恢复时执行上电复位,因此,复位后的模式总是FEI,总线分频被设置为2分频,产生大约4MHz的总线时钟。内部时钟调整位ICSTRM将被重置为0x80,微调寄存器的FTRIM位会被清零,所以如果要采用内部参考时钟,则须对它进行重新校准;如果调整值已保存在Flash存储器中,则须把保存值重新载入寄存器。

3.2 停止3模式

当进入停止3模式后,内部时钟源的大部分(包括锁频环)将关闭。内部时钟源在执行STOP指令时所处的模式不会影响停止3的功耗。但是,ICS的两个控制位,IREFSTEN和EREFSTEN会影响停止3的电流。若置1,则IREFSTEN可使IRC在停止3模式中保持启用状态;

同样,若置1,则EREFSTEN可使OSC在停止3模式中保持启用状态。将IREFSTEN置位,将产生约100μA的停止3电流;将EREFSTEN置位,将对停止3电流产生不同的影响,取决于OSC的频率和设置。

如果因复位而退出停止3,ICS会像停止1或停止2的恢复那样回复至FEI模式。不同之处是调整值不会重置,除非发生了上电复位。

4 内部时钟校准

系统经过上电复位后,ICSTRM将被重置为0x80,FTRIM位会被清零。如果要采用内部参考时钟,则需要对其进行重新校准。增大ICSTRM的值,将降低参考时钟频率;相反,减小ICSTRM的值,将提高参考时钟频率。FTRIM置0或1会更精细地对频率进行调整。根据这个原理,内部时钟校准的程序流程框图如图2所示。

关于具体的程序町根据参考文献编制。待ICGTRM和FTRIM选定后,可存入微控制器的Flash中,下次上电复位后直接读取数值载入即可。

结语

恰当地运用时钟设置,对于降低微控制器的功耗有很大帮助。在微控制器各种不同的运行模式下,时钟都有不同的配置方法与之配合。同样的方案也适用于功能类似的微控制器。巧妙地运用各种时钟模式,可以使系统的功耗最低。

飞思卡尔 单片机 电压 总线 仿真 电路 振荡器 滤波器 电容 电阻 MCU 电流 相关文章:

- 飞思卡尔用超低功率8位微控制器简化绿色嵌入式设计(01-09)

- 飞思卡尔利用基于优化微控制器技术的先进电表参考设计(09-11)

- 飞思卡尔 i.MX 处理器助力 Sharp 的 NetWalker(08-12)

- 艾默生与飞思卡尔携手开发面向小型板卡的Power Architecture技术(02-03)

- 飞思卡尔嵌入式硅片为福特汽车下一代SYNC系统提供动力(01-08)

- 飞思卡尔半导体使用Tektronix IConnect软件为发射机建模 (04-01)