基于WISHBONE总线的FLASH闪存接口设计

时间:09-04

来源:互联网

点击:

|

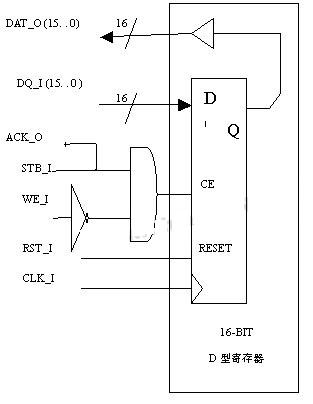

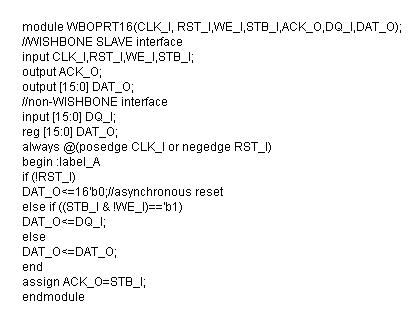

图3

FLASH写接口设计

因为FLASH写命令需要多个时钟周期时间,其中采用Unlock Bypass模式时为2个时钟周期,采用正常写模式需要4个时钟周期,并且在对FLASH写和擦写时更是需要等待几十微秒到几秒钟的时间,因此对接口SLAVE必须引入写或擦写完成状态信号来控制总线数据的传输。为简化设计采用RY/BY引脚来判断。输出端口原理图与图3类似,只需对部分端口进行修改即可。

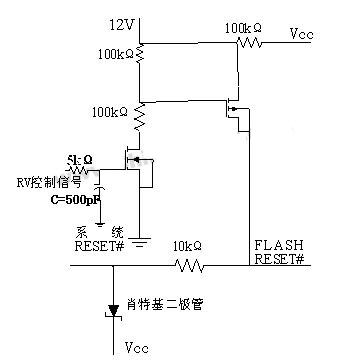

为了能够对块保护的程序代码进行升级,特别设计了一个12V电源电路来实现暂时块写保护解除功能,如图4所示。利用Am29LV160D芯片提供的暂时块写保护解除模式——即通过对RESET#引脚加VID电压。在该模式下先前被保护的块可以通过块地址选中来进行编程和擦除。并且一旦VID移除所有先前保护的块恢复到保护状态。

|

图4

图4中RV控制信号处采用了R=5kΩ,C=100pF,以便使得VID电压上升时间与下降时间≥500ns,从而满足相应的时序要求。肖特基二极管的引入保证了系统RESET信号被钳制在Vcc+0.3V以内。总体上来说,该电源隔离电路的引入对整个系统的成本影响很小,而使系统可以在线编程被保护的FLASH存储块。

总结

本文介绍了AMD公司Am29LV160D芯片特点,并在此基础上设计了基于WISHBONE总线的接口。该接口设计方法对其他相关SoC总线接口设计具有直接的参考意义。

半导体 SoC FPGA 总线 电流 Xilinx 电路 电压 二极管 相关文章:

- 在选用FPGA进行设计时如何降低功耗 (03-09)

- LPC2294的实时时钟显示工程设计分析(05-03)

- 飞思卡尔用超低功率8位微控制器简化绿色嵌入式设计(01-09)

- 恩智浦打造中国电子护照安全“芯”(09-21)

- 意法半导体安全解决方案强化防盗版功能(11-01)

- 新的步进电机控制器/驱动器简化步进电机系统设计(10-29)