基于WISHBONE总线的FLASH闪存接口设计

时间:09-04

来源:互联网

点击:

引言

随着半导体工艺技术的发展,IC设计者已能将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,即SoC芯片。对片上系统(SoC)数据记录需要低功耗、大容量、可快速重复擦写的存储器。常用的介质主要有:动态存储器(DRAM)、静态存储器(SRAM)和闪速存储器(FLASH MEMORY)。DRAM容量大,但需要不断刷新才能保持数据,会占用微处理器时间,同时增加了功耗;SRAM虽然不需要动态刷新,但价格太贵,并且断电后跟DRAM一样数据都无法保存。FLASH MEMORY是一种兼有紫外线擦除EPROM和电可擦除可编程只读存储器(EEPROM)两者优点的新型非易失存储器。由于它可在线进行电可擦除和编程,芯片每区可独立擦写至少1000 000次以上,因而对于需周期性地修改被存储的代码和数据表的应用场合,以及作为一种高密度的、非易失的数据存储介质FLASH是理想的器件选择。在我们设计的系统中,处理器是Openrisc1 200,所用的FLASH是AMD与富士公司的Am29LV160D芯片。利用FPGA实现接口,由于Openrisc1200(OR1200)采用WISHBONE总线,所以本设计的接口具有可移植性。

Am29LV160D芯片特点

Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器插入等待状态进行速度匹配。为了消除总线竞争,芯片引入了片选使能(CE#),写使能(WE#)和输出使能(OE#)控制端口。芯片采用分块结构,非常适用于要求高密度的代码或数据存储的低功耗系统。

● 甚低功耗

工作在5MHz时, 电流典型值为:

睡眠模式下电流为200nA;

备用模式下电流为200nA;

读数据时为9mA;

编程/擦除模式下电流为20mA。

● 灵活的分块结构

一个16KB,两个8KB,一个32KB,和31个64KB块(字节模式);

一个8KB,两个4 KB,一个16 KB,和31个32 KB块(字模式);

支持整个芯片擦除;

复杂的块保护特性。

● 具有内部嵌入算法

内部嵌入擦除算法自动预编程和擦除整个芯片或任意块的组合;

内部嵌入算法自动将给定地址的数据写入芯片及对其校验。

● 与JEDEC标准兼容

● 具有硬件RESET复位与Ready/Busy擦写查询管脚

● 具有擦除暂停与擦除继续功能

图1

WISHBONE总线简介

WISHBONE总线规范是一种片上系统IP核互连体系结构。它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度。WISHBONE总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容所有的综合工具,可以用多种硬件描述语言来实现。

灵活性是WISHBONE总线的另一个优点。由于 IP核种类多样,其间并没有一种统一的间接方式。为满足不同系统的需要,WISHBONE总线提供了四种不同的IP核互连方式:

点到点(point-to-point),用于两IP核直接互连;

数据流(data flow),用于多个串行IP核之间的数据并发传输;

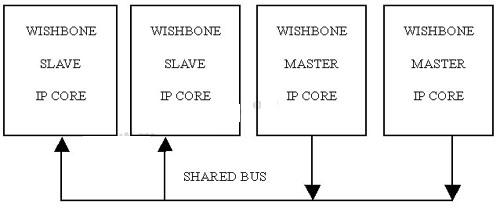

共享总线(shared bus)(见图1),多个IP核共享一条总线;

交叉开关(crossbar switch),同时连接多个主从部件,提高系统吞吐量。

FLASH接口的设计

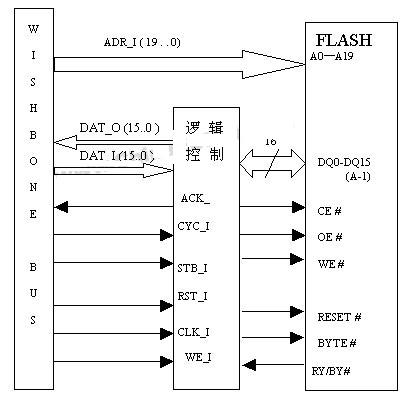

图2

由于OR1200采用的是WISHBONE共享总线,其地址线为32位,数据线也为32位。设计中采用将低位与FLASH相联接,并将接口位度设计为16位。原理框图如图2所示。逻辑接口部分采用FPGA来实现。系统选用Xilinx公司最新推出的90nm工艺制造的现场可编程门阵列芯片Spartan-3来实现接口设计,利用它的可编程性特性带来了电路设计的简单化和调试的灵活性。

FLASH读接口设计

该接口可实现单周期读与块读功能,时序部分与WISHBONE兼容。由于采用的FLASH最大读周期时间至少为90ns,故只有在总线时钟工作在10MHz以下频率时可以直接将ACK_O端口与STB_I端口相联。当MASTER(指令CACHE)发出块读信号时,将发出一个LOCK_O=VIH信号给总线仲裁器,要求总线能不间断提供总线。其对SLAVE(FLASH接口部分)控制信号为:

WE_I=VIL,CYC_I=VIH,STB_I=VIH,BYTE=VIH

当MASTER结束块读时发出STB_O= VIL信号即可。其输出接口部分如图3所示。该输出接口模块源代码如下:

随着半导体工艺技术的发展,IC设计者已能将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,即SoC芯片。对片上系统(SoC)数据记录需要低功耗、大容量、可快速重复擦写的存储器。常用的介质主要有:动态存储器(DRAM)、静态存储器(SRAM)和闪速存储器(FLASH MEMORY)。DRAM容量大,但需要不断刷新才能保持数据,会占用微处理器时间,同时增加了功耗;SRAM虽然不需要动态刷新,但价格太贵,并且断电后跟DRAM一样数据都无法保存。FLASH MEMORY是一种兼有紫外线擦除EPROM和电可擦除可编程只读存储器(EEPROM)两者优点的新型非易失存储器。由于它可在线进行电可擦除和编程,芯片每区可独立擦写至少1000 000次以上,因而对于需周期性地修改被存储的代码和数据表的应用场合,以及作为一种高密度的、非易失的数据存储介质FLASH是理想的器件选择。在我们设计的系统中,处理器是Openrisc1 200,所用的FLASH是AMD与富士公司的Am29LV160D芯片。利用FPGA实现接口,由于Openrisc1200(OR1200)采用WISHBONE总线,所以本设计的接口具有可移植性。

Am29LV160D芯片特点

Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器插入等待状态进行速度匹配。为了消除总线竞争,芯片引入了片选使能(CE#),写使能(WE#)和输出使能(OE#)控制端口。芯片采用分块结构,非常适用于要求高密度的代码或数据存储的低功耗系统。

● 甚低功耗

工作在5MHz时, 电流典型值为:

睡眠模式下电流为200nA;

备用模式下电流为200nA;

读数据时为9mA;

编程/擦除模式下电流为20mA。

● 灵活的分块结构

一个16KB,两个8KB,一个32KB,和31个64KB块(字节模式);

一个8KB,两个4 KB,一个16 KB,和31个32 KB块(字模式);

支持整个芯片擦除;

复杂的块保护特性。

● 具有内部嵌入算法

内部嵌入擦除算法自动预编程和擦除整个芯片或任意块的组合;

内部嵌入算法自动将给定地址的数据写入芯片及对其校验。

● 与JEDEC标准兼容

● 具有硬件RESET复位与Ready/Busy擦写查询管脚

● 具有擦除暂停与擦除继续功能

|

图1

WISHBONE总线简介

WISHBONE总线规范是一种片上系统IP核互连体系结构。它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度。WISHBONE总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容所有的综合工具,可以用多种硬件描述语言来实现。

灵活性是WISHBONE总线的另一个优点。由于 IP核种类多样,其间并没有一种统一的间接方式。为满足不同系统的需要,WISHBONE总线提供了四种不同的IP核互连方式:

点到点(point-to-point),用于两IP核直接互连;

数据流(data flow),用于多个串行IP核之间的数据并发传输;

共享总线(shared bus)(见图1),多个IP核共享一条总线;

交叉开关(crossbar switch),同时连接多个主从部件,提高系统吞吐量。

FLASH接口的设计

|

图2

由于OR1200采用的是WISHBONE共享总线,其地址线为32位,数据线也为32位。设计中采用将低位与FLASH相联接,并将接口位度设计为16位。原理框图如图2所示。逻辑接口部分采用FPGA来实现。系统选用Xilinx公司最新推出的90nm工艺制造的现场可编程门阵列芯片Spartan-3来实现接口设计,利用它的可编程性特性带来了电路设计的简单化和调试的灵活性。

FLASH读接口设计

该接口可实现单周期读与块读功能,时序部分与WISHBONE兼容。由于采用的FLASH最大读周期时间至少为90ns,故只有在总线时钟工作在10MHz以下频率时可以直接将ACK_O端口与STB_I端口相联。当MASTER(指令CACHE)发出块读信号时,将发出一个LOCK_O=VIH信号给总线仲裁器,要求总线能不间断提供总线。其对SLAVE(FLASH接口部分)控制信号为:

WE_I=VIL,CYC_I=VIH,STB_I=VIH,BYTE=VIH

当MASTER结束块读时发出STB_O= VIL信号即可。其输出接口部分如图3所示。该输出接口模块源代码如下:

半导体 SoC FPGA 总线 电流 Xilinx 电路 电压 二极管 相关文章:

- 在选用FPGA进行设计时如何降低功耗 (03-09)

- LPC2294的实时时钟显示工程设计分析(05-03)

- 飞思卡尔用超低功率8位微控制器简化绿色嵌入式设计(01-09)

- 恩智浦打造中国电子护照安全“芯”(09-21)

- 意法半导体安全解决方案强化防盗版功能(11-01)

- 新的步进电机控制器/驱动器简化步进电机系统设计(10-29)