在SoC设计中采用ESL设计和验证方法

时间:08-06

来源:互联网

点击:

3.验证视图TLM

验证视图本质上就是AV模型,它在周期精确的时序方面得到增强。这种模型能够实现可精确预测真实芯片时序的硬件验证和硬件/软件验证,它还使开发团队能创建用于RTL验证的测试基准。用Verilog和/或者VHDL编写的RTL模型一旦完成,便可在VV TLM模型中例示,这样在完整的SoC实现模型完成之前就能进行系统验证以及调试。

VV仿真的执行速度一般比RTL仿真和C/RTL HW/SW协同验证速度快三个数量级。

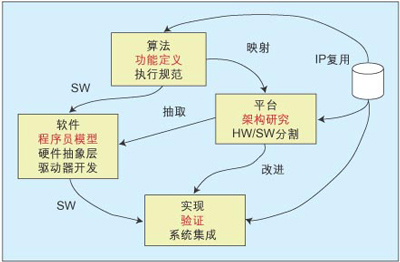

这三个TLM视图组成了全部ESL设计流程(如图5所示),不同模型可以利用易于设计的处理器和转换器协同执行。

图5:带有三种主要TLM使用模式的HW/SW开发流程。

ESL设计成功案例

领先的系统和半导体公司已经公开宣称ESL设计的结果超出预期,他们已转向采用在准硅片多处理器系统仿真模型上开发软件的标准操作过程,该模型能以近似实时性能执行。在某些情况下,仿真模型仅在两秒内就可引导普通的RTOS,例如嵌入式Linux。TLM方法具有良好的精确性,在将硅原型交付制造之前,这种精确性对于优化芯片架构的性能和功耗来说很关键。

例如,某大型日本打印机公司采用ESL设计方法,因为基于RTL的方法已不能应对每一代打印机所需的架构上的重大修改。该公司对其从低端家庭打印机到高端网络打印机的所有产品都采用相同的基本算法。然而,不同打印机类型在数据通信、处理、存储需求上的重大差异要求那些算法有明显不同的实现,包括不同的存储器架构和通信总线架构。

优化这些不同架构只能在ESL设计提供的TLM抽象级别上才能得到有效实现。不过,简单地转向ESL设计而缺少到RTL实现的链接将导致下游问题。该公司用管脚精确的事务器建立了这种允许SystemC TLM与RTL协同验证的链接。

从RTL转到ESL设计是一条很好的转移路径。ESL是一种“由中间开始(middle-out)”的设计流程,允许重复利用原有的RTL IP。在那些没有传统约束的情况下,可以采用“自顶向下”的设计流程。东芝公司便是采用这种流程,利用设计套件开发用户可配置媒体嵌入式处理器(MeP)。这个设计套件的基础是使设计工程师能针对特定应用定制配置的ESL设计环境。设计工程师可研究不同配置以确定哪种配置最佳,他们不仅要验证架构,而且还要验证每个硬件和软件模块是否满足系统要求。

LSI逻辑公司在其ZSP数字信号处理器内核设计中采用了类似方法。LSI对每种不同的内核开发周期和事务精确的SystemC模型,这使设计工程师能够对SoC架构中的内核性能建模。这些模型还使设计工程师能对硬软件交互进行调试。此外,设计师还可分析处理器的吞吐量和时延以及存储器性能。

本文小结

ESL设计和验证方法使设计工程师能够专注于那些给产品及IP带来差异化和价值的系统设计属性,即功能性和性能。这些属性是由先进算法、复杂的多处理器和存储器架构、高级通信协议以及针对应用优化的处理器(它们都由嵌入式软件驱动)决定的。RTL实现的精巧性与高效的实现有关,但其价值则存在系统设计中。IP的创新和拥有将成为中国电子产业的下一场革命,而ESL设计和验证方法学将成为这场革命的支撑力量。

电子 SoC 嵌入式 半导体 蓝牙 DSP C语言 仿真 电路 总线 解码器 Verilog VHDL Linux 相关文章:

- 利用蓝牙技术和远程信息控制单元实现汽车诊断(11-13)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)

- 汽车网络的分类及发展趋向(11-13)

- 多核嵌入式处理技术推动汽车技术发展(11-18)

- CAN总线的客车轻便换档系统设计与实现(02-13)

- 高性能嵌入式ARM MPU在医疗电子系统中的设计应用(05-12)