基于EPIC技术的密码处理器体系结构研究与设计

时间:08-03

来源:互联网

点击:

3 指令系统设计

指令系统是算法要素和密码处理器体系结构特性的集中体现,指令系统的设计必须支 持硬件的并行执行,即开发指令级并行性(ILP),指令级并行性的开发程度对发挥密码微处理器的硬件特性,提高程序运行性能至为关键。ILP技术实际上是指一套完整的处理器设计和编译技术,这些技术通过并行地执行独立的机器操作(如存储器读写、逻辑运算、算术运算等)来加速程序的执行。ILP的大小可以采用每周期平均执行的指令数(IPC)朱衡量,或者采用整个程序的每条指令平均执行的周期数CPI(CPT=l/IPC)来衡量。在可编程密码处理器体系结构中采用了显式并行指令计算结构,指令级并行数达到5。

3.1 指令分类

可编程密码处理器体系结构中的指令分为以下几类:

(1)静态配置指令。它是在密钥生成及加/解密过程中保持不变或者改变次数很少的控制信息配置指令,算法确定后,其S盒查找表信息、有限域乘数矩阵和不可约多项式、若干个置换的控制信息等就确定了,它们不会因为操作模式不同而改变。在加/解密过程中采用将配置指令分离出来的方法,可以大大减少执行密码运算时指令的冗余编码,从而缩短了指令字的长度,增加了运算指令字中包含有效操作的个数,有效地提高了加/解密速度并减少了密码程序的代码量。

(2)短指令。它执行除置换与128bit移位运算外的各种密码运算和内部寄存器问的数据传输操作。

(3)长指令。它执行置换与128bit移位运算。

(4)超长指令。它执行立即数操作和多分支判断操作。

(5)控制指令。它执行程序跳转、子程序调用及返回、单分支判断等控制操作。

3.2 指令形态

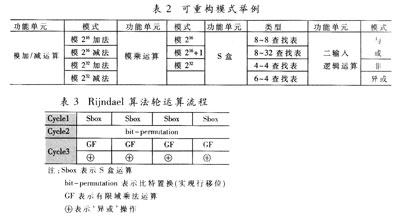

在硬件上,多个功能单元的设置为多条指令的并行执行提供了支持,而哪些指令可以并行执行,哪些指令不能并行执行以及如何将多条指令组装成一条指令的原则,即称为指令的拼装规则。在此设计中有以下几种指令形态:

(1) 静态配置指令。

(2) 超长指令。

(3) 短指令Ⅱ短指令Ⅱ短指令Ⅱ短指令ll控制指令。

(4) 长指令Ⅱ控制指令。

其中短指令长度为37bit,控制指令长度为32bit,长指令长度为148bit。无论上述哪种形态,最终的指令字长度都为192bit(包括指令拼装标识),如四个短指令可以与控制指令拼装成一条指令,长指令也可以与控制指令拼装成一条指令,但静态配置指令与超长指令不能与其他指令拼装,自身组成一个192bit的指令字。

4 性能分析

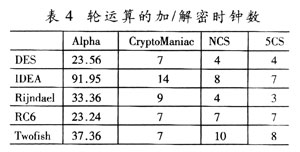

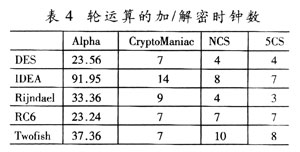

由于可编程密码处理器体系结构支持5条指令绑定并行执行,因此其数据路径定义为5CS(5Combining-Strands),假设不采用绑定的数据路径定义为NCS(No-Combining-Strands),将这两种情况与Alpha处理器、Cryp-toManiac密码处理器[9]路程进行比较,四种数据路径下加/解密所需时钟数如表4所示。分析比较表明可编程密码处理器执行时钟大量减少,尤其与通用处理器Al-pha相比,加/解时钟数DES算法减少83%,IDEA算法减少92%,Rijndael算法减少9l%,RC6算法减少69%,Twofish算法减少78%。

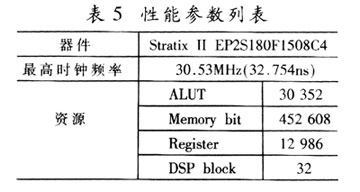

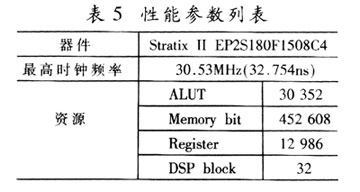

为了验证可编程密码处理器体系结构实现数据通路和控制通路的正确性,使用Altera StratixlIEP2S180F1508C4器件作为FPCA目标芯片,使用AlteraQuartusII 5.0工具进行综合,在综合前和综合后使用Mentor公司的ModelSim 5.8c分别进行功能仿真和时序仿真,结果均正确。其具体资源占用情况如表5所示。

密码处理的灵活性和高效性一直是密码算法使用中的制约因素,采用通用微处理器虽然能获得较好的灵活性,但却使一些算法的性能达不到要求;采用专用算法芯片,在获得很高性能的同时丧失了灵活性。本文针对这一矛盾以EPIC结构微处理器构架为出发点,系统地研究了通用的并行分组密码处理器模型、各种密码运算单元、指令集等关键技术,并最终得以实现,达到了实现性能与灵活性之间的良好折衷。

指令系统是算法要素和密码处理器体系结构特性的集中体现,指令系统的设计必须支 持硬件的并行执行,即开发指令级并行性(ILP),指令级并行性的开发程度对发挥密码微处理器的硬件特性,提高程序运行性能至为关键。ILP技术实际上是指一套完整的处理器设计和编译技术,这些技术通过并行地执行独立的机器操作(如存储器读写、逻辑运算、算术运算等)来加速程序的执行。ILP的大小可以采用每周期平均执行的指令数(IPC)朱衡量,或者采用整个程序的每条指令平均执行的周期数CPI(CPT=l/IPC)来衡量。在可编程密码处理器体系结构中采用了显式并行指令计算结构,指令级并行数达到5。

3.1 指令分类

可编程密码处理器体系结构中的指令分为以下几类:

(1)静态配置指令。它是在密钥生成及加/解密过程中保持不变或者改变次数很少的控制信息配置指令,算法确定后,其S盒查找表信息、有限域乘数矩阵和不可约多项式、若干个置换的控制信息等就确定了,它们不会因为操作模式不同而改变。在加/解密过程中采用将配置指令分离出来的方法,可以大大减少执行密码运算时指令的冗余编码,从而缩短了指令字的长度,增加了运算指令字中包含有效操作的个数,有效地提高了加/解密速度并减少了密码程序的代码量。

(2)短指令。它执行除置换与128bit移位运算外的各种密码运算和内部寄存器问的数据传输操作。

(3)长指令。它执行置换与128bit移位运算。

(4)超长指令。它执行立即数操作和多分支判断操作。

(5)控制指令。它执行程序跳转、子程序调用及返回、单分支判断等控制操作。

3.2 指令形态

在硬件上,多个功能单元的设置为多条指令的并行执行提供了支持,而哪些指令可以并行执行,哪些指令不能并行执行以及如何将多条指令组装成一条指令的原则,即称为指令的拼装规则。在此设计中有以下几种指令形态:

(1) 静态配置指令。

(2) 超长指令。

(3) 短指令Ⅱ短指令Ⅱ短指令Ⅱ短指令ll控制指令。

(4) 长指令Ⅱ控制指令。

其中短指令长度为37bit,控制指令长度为32bit,长指令长度为148bit。无论上述哪种形态,最终的指令字长度都为192bit(包括指令拼装标识),如四个短指令可以与控制指令拼装成一条指令,长指令也可以与控制指令拼装成一条指令,但静态配置指令与超长指令不能与其他指令拼装,自身组成一个192bit的指令字。

4 性能分析

由于可编程密码处理器体系结构支持5条指令绑定并行执行,因此其数据路径定义为5CS(5Combining-Strands),假设不采用绑定的数据路径定义为NCS(No-Combining-Strands),将这两种情况与Alpha处理器、Cryp-toManiac密码处理器[9]路程进行比较,四种数据路径下加/解密所需时钟数如表4所示。分析比较表明可编程密码处理器执行时钟大量减少,尤其与通用处理器Al-pha相比,加/解时钟数DES算法减少83%,IDEA算法减少92%,Rijndael算法减少9l%,RC6算法减少69%,Twofish算法减少78%。

为了验证可编程密码处理器体系结构实现数据通路和控制通路的正确性,使用Altera StratixlIEP2S180F1508C4器件作为FPCA目标芯片,使用AlteraQuartusII 5.0工具进行综合,在综合前和综合后使用Mentor公司的ModelSim 5.8c分别进行功能仿真和时序仿真,结果均正确。其具体资源占用情况如表5所示。

密码处理的灵活性和高效性一直是密码算法使用中的制约因素,采用通用微处理器虽然能获得较好的灵活性,但却使一些算法的性能达不到要求;采用专用算法芯片,在获得很高性能的同时丧失了灵活性。本文针对这一矛盾以EPIC结构微处理器构架为出发点,系统地研究了通用的并行分组密码处理器模型、各种密码运算单元、指令集等关键技术,并最终得以实现,达到了实现性能与灵活性之间的良好折衷。

电路 PIC 总线 Altera Quartus Mentor ModelSim 仿真 相关文章:

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)