宽频带数字锁相环的设计及基于FPGA的实现

时间:07-19

来源:互联网

点击:

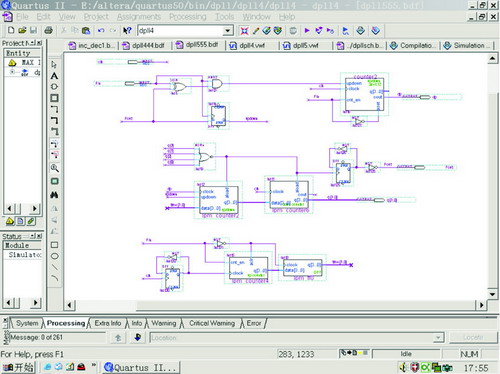

图3 改进型异或门鉴相器DPLL原理图

其中,可逆计数器counter2为环路滤波器DLF,预设初值为12,加法进位模值为4,减法进位模值为12。可逆计数器lmp_counter2为数控振荡器,其预置值为time[3..0],其输出即为锁相环路分频器的模值N,输出值大小随着控制脉冲信号DP的数目有关。在本设计中,fclk=64MHz,fin=2Mb/s,则time[3..0]=0100b=8。加法计数器lmp_counter2为模值N受控的锁相环路分频器。值得注意的是锁相环路分频器lmp_counter2的进位输出Cout不可直接作为分频输出,因为在仿真过程中发现随着fclk频率的升高,Cout容易产生冒险毛刺,影响锁相环的稳定性。因此外加一4输入或非门作为分频器输出判决。

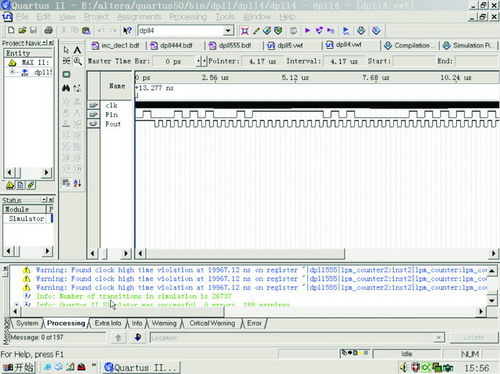

在图4仿真结果中,fclk=64MHz,fin=2Mb/s。 仿真输入信号Fin为一任意的二进制码流信号。可见,对于多位连1或连0的码流信号,该锁相环的输出Fout都能准确恢复出同步所需的时钟。在第二个输入码位到来时本地恢复时钟Fout就已经进入同步状态,捕捉速度很快。相位锁定误差最大为π/2N=π/16。

图4 改进型异或门鉴相器DPLL仿真结果

捕获带宽的扩展

上述设计的数字锁相环虽然可以快速锁定,锁相精度也较高,但其捕捉范围较窄。该数字锁相环的最大相移调整能力为±π,一旦输入信号Fin的相位抖动超过这个范围或Fin的频率发生改变,锁相环无法自动完成捕捉锁定。因此,对该设计需进行扩展设计,以实现宽频带捕捉功能。

为实现宽频带捕捉,设置一专门电路,测定输入信号Fin每个比特的周期(或频率),并判定是否发生变化,若测得比特周期发生变化,就会去控制调整DCO的输出振荡频率,使其快速跟踪Fin的频率,再配合前述数字锁相环的相位跟踪,就可完成宽范围频率锁定。电路原理如图5。

宽频带DPLL频率捕获电路原理图

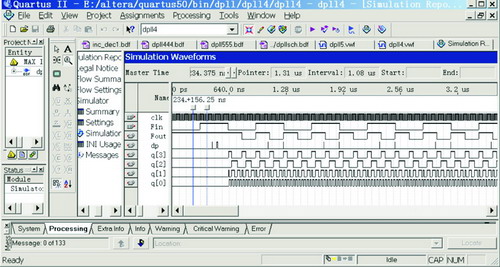

将图5电路和图3上面的一个电路合并,即为完整的宽频带DPLL电路。测得输入信号Fin的周期信号time[3..0]被送往图3锁相环路分频器lmp_counter2,去控制DCO的输出振荡频率。该宽频带DPLL电路的捕获范围最高频率fcmax=fclk/4,最低频率fcmax=fclk/4M,M为N分频器的最大取值。本设计中,fclk =64MHz,M=16。所以锁相环的频率捕获范围理论值为16MHz-1MHz。对应于输入码流的速率为32MHz-2MHz。当Fin=16MHz和Fin=1.6MHz时的仿真结果如图6(1)(2)。

图6-1 Fin="16MHz时的仿真波形"

图6-2 Fin="1".6MHz时的仿真波形

根据仿真结果,可实现稳定锁相的最低频率为1.2MHz,略高于理论值1MHz;可实现的最高锁相频率为16MHz。捕获时间1个Fin周期。

结语

在一般的数字锁相环设计中,“捕获时间”和“捕获带宽”这两项关键的性能指标是相互矛盾的,其中任何一项指标的提高都会牺牲另一项指标为代价。本文所介绍的宽频带范围数字锁相环采用较为简单的完成实现了捕获时间小而捕获带宽又相当宽的全数字锁相环,解决了“捕获时间”和“捕获带宽”指标相互矛盾的问题。其中“捕获带宽”指标可以通过提高工作时钟fclk的频率以及锁相环中的计数器的计数容量来进一步扩展。由于该数字锁相环可直接用于同步串行通信中二进制码流的同步时钟的恢复,可自动跟踪接收码流速率的变换,同时该设计是基于FPGA的模块化设计,便于其他数字系统设计的移植和集成,在其他数字应用系统特别是在基于FPGA的通信电路中有着重要的意义。

无线电 电子 模拟电路 电压 集成电路 FPGA 电路 滤波器 振荡器 Altera VHDL CPLD 仿真 相关文章:

- 基于DSP的单兵作战用机器人控制系统设计(07-25)

- 应用处理器连接汽车和消费电子两大领域(02-26)

- TMS320C6000嵌入式系统优化编程的研究(04-08)

- TI首席科学家展望2020年处理器架构和DSP的发展(10-24)

- 基于JTAG接口实现ARM的FPGA在线配置(04-24)

- 数字信号处理器的市场竞争及技术发展趋势(06-24)