TMS320C54xx DSP的USB接口实现

时间:06-27

来源:互联网

点击:

通用串行总线USB(Universal Serial Bus)应用由三部分组成:具有USB接口的PC系统、能够支持USB的系统软件和使用USB接口的设备。USB应用采用通用连接技术,实现外设的简单快速连接,借以达到方便用户、降低成本、扩展PC机连接外设范围的目的。USB的特点如下:

(1)连接灵活、使用方便 现在计算机系统连接外围设备的接口并无统一的标准,如键盘用PS/2接口,打印机用25针的并行接口等。USB则将这些不同的接口统一起来,由一组微小的矩型插座和软件构成。用户插入外设后,计算机系统能够自动识别接入的外设,而不需要重新启动系统,用户可以带电插拔;为USB设计的驱动程序和应用软件可以自动启动,无需用户干预USB设备,也不涉及IRQ冲突等问题;USB单独使用自己的保留中断,不会同其它设备争用PC机的有限资源。

(2)为外设提供电源 USB能自动识别外设所需的电源,并通过USB电缆向该设备供电(最高可达500mA)。

(3)速度快 USB的最高传输率可达12Mbit/s,比串口速度快100倍,比并口速度快近10倍。USB端口的传输速率比目前PC机平台上的任何其它类型端口的传输速率都快。预计今后USB的速度将会提高到100Mbit/s以上。

(4)支持多媒体 USB提供了对电话的两路数据支持,它可支持异步及等时数据传输,使电话可与PC机集成,共享语音邮件及其它功能。由于USB音频信息生成于计算机外,因而减少了电子噪音干扰声音质量的机会,从而使音频系统具有更高的保真度。

1 USB接口芯片AN2131Q

目前市场上USB接口芯片很多,使用较为广泛的是Crypress公司的AN2131系列的USB接口芯片AN2131Q。AN2131Q具有以下优点:

(1)基于RAM的"软"系统解决方案(SOFT,RAM BASED),不需要ROM或其它的固化存储器,而只使用片内的程序/数据RAM。通过主机下载的方式来配置USB接口,因而使接口系统的修改和升级变得非常简单,使外设硬件的更新和升级变得更为方便。

(2)数据吞吐量完全达到USB协议要求,可以向用户提供足够的端口、缓冲区和传输速度;提供USB协议要求的全部四种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种类型数据传输的需求。

(3)片上的串行接口处理机(SIE)完成大部分的USB协议操作,使用户可以摆脱复杂的协议细节,简化了用户配置代码,加快了开发过程。

(4)内嵌增强型8051处理器,兼容8051指令系统;一个指令周期仅需四个时钟周期,可提供标准8051三倍以上的处理能力;双数据指针,方便数据块搬移;使用片内RAM作为数据/程序存储器,非复用数据/地址总线,使程序执行速度更快,并且其同外部器件的连接更加简单。

(5)休眠模式可以降低系统功耗,延长器件的使用寿命。

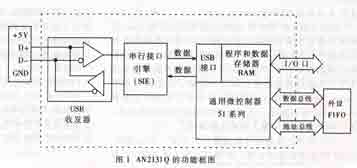

AN2131Q的功能框图如图1所示。

USB收发器和PC机的接口只有四根导线:+5V、GND、D+、D-。数据以12Mb/s的全速信号或者以1.5Mb/s的低速信号在D+和D信号线上差分传输。收发器固化在芯片上,不需要外部电路,最多只需要用来选择全速或者低速的上拉电阻。

串行接口引擎(SIE)通过包排序、信号产生及检测、CRC产生及校验、NRZI数据编码、位填充以及包标识产生及解码等功能块处理USB通信协议,并保证传送到USB电缆上的数据字节以LSB开头。

AN2131Q采用通用的8051微控制器及片上RAM,其编程语言为51系列单片机的通用语言,使用方便。

2 TMS320C54XX DSP和AN2131Q接口芯片的硬件连接

TMS320C54xx DSP芯片选用TI公司的TMS320VC5409,Tms320VC5409是定点DSP芯片,它使用改进的哈佛结构,8级流水线操作,最高速度可以达到166MIPS。

在AN2131Q芯片和TMS320C54xx DSP芯片之间采用FIFO(First In First Out SRAM)芯片连接,可以使USB接口芯片和DSP之间的最大数据交换速度超过USB总线的速度,使之不成为数据传输的瓶颈,从而使DSP和主机间的数据传输速度只受USB协议限制。

由于AN2131Q芯片内嵌8位8051处理器,所以使用两片8位FIFO芯片实现USB接口和DSP之间的双向通信。FIFO选用具有1K×9bit内存的IDT72V02。从AN2131Q或者DSP传输的数据首先保存在FIFO中,然后再由DSP或者AN2131Q读走,从而使得数据的传输不会出现堵塞情况,其硬件连接框图如图2所示。

由于选用的FIFO只有双端数据总线和状态信号,没有地址总线,所以DSP采用I/O译码方式访问FIFO。FIFO状态信号有空(EF)、半满(HF)和满(FF),它们都是低有效。合理利用这三个信号可以很有效地提高FIFO的读写效率。例如利用HF,如果其无效,表示FIFO中的数据没有达到半满,此时不用查询FF就可以向FIFO中写入一块数据,只要数据块的大小等于或小于FIFO容量的一半,FIFO肯定不会满溢出。这样就可以大大提高FIFO的写入速度。

3 TMS320C54XX DSP芯片和AN2131Q芯片的软件连接

AN2131Q芯片和TMS320C54XX DSP芯片之间的软件连接包括四个部分:AN2131Q对FIFO1的写、AN2131Q对FIFO2的读、DSP对FIFO1的读、DSP对FIFO2的写。为了描述方便,将FIFO1的三个状态信号称之为:EF1、HF1和FF1,将FIFO2的状态信号称为EF2、HF2和HF2。

3.1 AN2131Q写FIFO1

当USB总线上有数据要传送至DSP时,AN2131Q查询HF1。若HF1无效,AN2131Q一次向FIFO1写入一个数据包。包大小要小于或等于FIFO1容量的一半,写每一个字节时不需再查询FF1。

3.2 DSP读FIFO1

DSP每次从FIFO1中读入一个数据包。每读一个字节前,DSP需要查询EF1,只有当EF1无效(FIFO1不空)时,DSP才可能进行读操作。

3.3 DSP写FIFO2

当DSP有数据要传送至主机时,DSP把数据打包,每次向FIFO2中写入一包数据。方法同AN2131Q写FIFO1,只不过DSP查询的信号是HF2。写完一包后,DSP向AN2131Q发一个中断信号,DSP在写下一包数据时要等待AN2131Q的应答。AN2131Q应答的方法是利用DSP的外部中断INT1中断DSP。

3.4 AN2131Q读FIFO2

AN2131Q收到DSP发出的中断信号,应答DSP后,从FIFO2中读入一包数据,不用再查询EF2。

3.5 数据包格式

每个数据包由包头和数据两部分构成?如图3所示。包头长度为一个字节,指明以字节为单位包中数据(不含包头)的长度。包中的数据要少于或等于64字节,即最大的包总长度为65字节。

(1)连接灵活、使用方便 现在计算机系统连接外围设备的接口并无统一的标准,如键盘用PS/2接口,打印机用25针的并行接口等。USB则将这些不同的接口统一起来,由一组微小的矩型插座和软件构成。用户插入外设后,计算机系统能够自动识别接入的外设,而不需要重新启动系统,用户可以带电插拔;为USB设计的驱动程序和应用软件可以自动启动,无需用户干预USB设备,也不涉及IRQ冲突等问题;USB单独使用自己的保留中断,不会同其它设备争用PC机的有限资源。

(2)为外设提供电源 USB能自动识别外设所需的电源,并通过USB电缆向该设备供电(最高可达500mA)。

(3)速度快 USB的最高传输率可达12Mbit/s,比串口速度快100倍,比并口速度快近10倍。USB端口的传输速率比目前PC机平台上的任何其它类型端口的传输速率都快。预计今后USB的速度将会提高到100Mbit/s以上。

(4)支持多媒体 USB提供了对电话的两路数据支持,它可支持异步及等时数据传输,使电话可与PC机集成,共享语音邮件及其它功能。由于USB音频信息生成于计算机外,因而减少了电子噪音干扰声音质量的机会,从而使音频系统具有更高的保真度。

1 USB接口芯片AN2131Q

目前市场上USB接口芯片很多,使用较为广泛的是Crypress公司的AN2131系列的USB接口芯片AN2131Q。AN2131Q具有以下优点:

(1)基于RAM的"软"系统解决方案(SOFT,RAM BASED),不需要ROM或其它的固化存储器,而只使用片内的程序/数据RAM。通过主机下载的方式来配置USB接口,因而使接口系统的修改和升级变得非常简单,使外设硬件的更新和升级变得更为方便。

(2)数据吞吐量完全达到USB协议要求,可以向用户提供足够的端口、缓冲区和传输速度;提供USB协议要求的全部四种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种类型数据传输的需求。

(3)片上的串行接口处理机(SIE)完成大部分的USB协议操作,使用户可以摆脱复杂的协议细节,简化了用户配置代码,加快了开发过程。

(4)内嵌增强型8051处理器,兼容8051指令系统;一个指令周期仅需四个时钟周期,可提供标准8051三倍以上的处理能力;双数据指针,方便数据块搬移;使用片内RAM作为数据/程序存储器,非复用数据/地址总线,使程序执行速度更快,并且其同外部器件的连接更加简单。

(5)休眠模式可以降低系统功耗,延长器件的使用寿命。

AN2131Q的功能框图如图1所示。

|

USB收发器和PC机的接口只有四根导线:+5V、GND、D+、D-。数据以12Mb/s的全速信号或者以1.5Mb/s的低速信号在D+和D信号线上差分传输。收发器固化在芯片上,不需要外部电路,最多只需要用来选择全速或者低速的上拉电阻。

串行接口引擎(SIE)通过包排序、信号产生及检测、CRC产生及校验、NRZI数据编码、位填充以及包标识产生及解码等功能块处理USB通信协议,并保证传送到USB电缆上的数据字节以LSB开头。

AN2131Q采用通用的8051微控制器及片上RAM,其编程语言为51系列单片机的通用语言,使用方便。

2 TMS320C54XX DSP和AN2131Q接口芯片的硬件连接

TMS320C54xx DSP芯片选用TI公司的TMS320VC5409,Tms320VC5409是定点DSP芯片,它使用改进的哈佛结构,8级流水线操作,最高速度可以达到166MIPS。

在AN2131Q芯片和TMS320C54xx DSP芯片之间采用FIFO(First In First Out SRAM)芯片连接,可以使USB接口芯片和DSP之间的最大数据交换速度超过USB总线的速度,使之不成为数据传输的瓶颈,从而使DSP和主机间的数据传输速度只受USB协议限制。

由于AN2131Q芯片内嵌8位8051处理器,所以使用两片8位FIFO芯片实现USB接口和DSP之间的双向通信。FIFO选用具有1K×9bit内存的IDT72V02。从AN2131Q或者DSP传输的数据首先保存在FIFO中,然后再由DSP或者AN2131Q读走,从而使得数据的传输不会出现堵塞情况,其硬件连接框图如图2所示。

|

由于选用的FIFO只有双端数据总线和状态信号,没有地址总线,所以DSP采用I/O译码方式访问FIFO。FIFO状态信号有空(EF)、半满(HF)和满(FF),它们都是低有效。合理利用这三个信号可以很有效地提高FIFO的读写效率。例如利用HF,如果其无效,表示FIFO中的数据没有达到半满,此时不用查询FF就可以向FIFO中写入一块数据,只要数据块的大小等于或小于FIFO容量的一半,FIFO肯定不会满溢出。这样就可以大大提高FIFO的写入速度。

3 TMS320C54XX DSP芯片和AN2131Q芯片的软件连接

AN2131Q芯片和TMS320C54XX DSP芯片之间的软件连接包括四个部分:AN2131Q对FIFO1的写、AN2131Q对FIFO2的读、DSP对FIFO1的读、DSP对FIFO2的写。为了描述方便,将FIFO1的三个状态信号称之为:EF1、HF1和FF1,将FIFO2的状态信号称为EF2、HF2和HF2。

3.1 AN2131Q写FIFO1

当USB总线上有数据要传送至DSP时,AN2131Q查询HF1。若HF1无效,AN2131Q一次向FIFO1写入一个数据包。包大小要小于或等于FIFO1容量的一半,写每一个字节时不需再查询FF1。

3.2 DSP读FIFO1

DSP每次从FIFO1中读入一个数据包。每读一个字节前,DSP需要查询EF1,只有当EF1无效(FIFO1不空)时,DSP才可能进行读操作。

3.3 DSP写FIFO2

当DSP有数据要传送至主机时,DSP把数据打包,每次向FIFO2中写入一包数据。方法同AN2131Q写FIFO1,只不过DSP查询的信号是HF2。写完一包后,DSP向AN2131Q发一个中断信号,DSP在写下一包数据时要等待AN2131Q的应答。AN2131Q应答的方法是利用DSP的外部中断INT1中断DSP。

3.4 AN2131Q读FIFO2

AN2131Q收到DSP发出的中断信号,应答DSP后,从FIFO2中读入一包数据,不用再查询EF2。

3.5 数据包格式

每个数据包由包头和数据两部分构成?如图3所示。包头长度为一个字节,指明以字节为单位包中数据(不含包头)的长度。包中的数据要少于或等于64字节,即最大的包总长度为65字节。

总线 USB 电子 收发器 电路 电阻 单片机 DSP MIPS IDT Cypress 相关文章:

- 基于MSP430系列单片机的CAN总线接口转换卡设计(01-17)

- 各种通讯总线介绍(01-18)

- I2C总线原理及应用实例 (01-18)

- I2C总线在多机通信中的应用(01-17)

- 基于SPI总线的电能计量芯片ATT7022及其在配电监测终端的应用(01-18)

- CAN总线—PROFIBUS-DP总线网关的实现方法(01-17)