ADSP21062信号处理板的一种简易测试方法

时间:06-25

来源:互联网

点击:

ADSP2106x SHARC是一个适用于语音、通信和图像处理的高速32位数字信号处理器。该芯片是基于ADSP21000系列DSP芯片发展起来的一个完整的单片系统,增加了一个双口片内SRAM,并集成了I/O设备。借助它的片内指令缓存,处理器可以在一个时钟周期内执行每一个指令。ADSP2106x SHARC体现了数字信号处理器的一个新的集成标准,它把一个高速运行的浮点DSP主处理器与集成的片内部件结合在一起,包括一个主机接口、DMA控制器、串口和连接口。由于它处理速度快、便于DSP多处理系统的连接和通信,目前已在更多的领域获得了开发和应用 1 。但如何对基于ADSP2106x的处理系统进行调试是人们在应用该芯片时必须解决的关键问题。本文提出了一种简单易行的测试方法,并在基于ADSP21062的雷达信号处理系统调试中获得了成功,验证了该方法的可行性。

1 雷达信号处理系统设计简介

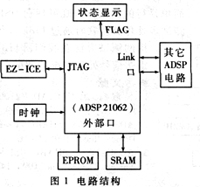

我们应用ADSP21062处理器设计了一个雷达信号处理系统。此系统可以独立地进行工作,也可通过Link口与其它DSP进行通信。ADSP21062利用JTAG接口与EZ-ICE仿真器连接,实现对系统的仿真和测试。系统的电路结构见图1。

EZ-ICE仿真器应用IEEE1149.1 JTAG测试标准,监视和控制目标板处理器的工作。EZ-ICE仿真器的测试头通过一个14针的连接头与目标板处理器的CLKIN (可选)、TMS、TCK、TRST、TDI、TDO、和GND信号相连。在电路板上设计了一个14针的接口,其信号的接口如图2所示。

2 电路的测试

电路测试主要应用EZ-ICE仿真器。该仿真器插在PC机的ISA槽中,通过JTAG口与ADSP21062处理系统相连,可在PC机的显示器上利用Emulator控制界面对DSP系统运行情况进行实时监控。ADSP2106x提供了模拟(Simulator)和仿真(Emulator)两套软件,它们的界面完全相同,只是一个不需要硬件,一个需要硬件。测试程序可先由Assembler汇编器汇编,再经Simulator模拟通过。最后在Emulator界面控制下可以装入由汇编生成的可执行文件(.EXE文件)和汇编的结构文件(.ACH文件),实现对硬件的测试和仿真。

2.1 硬件测试的基本操作

对硬件测试时,先对存储器的内部控制、状态寄存器和存储器做简单的操作,确定EZ-ICE仿真器与处理器的通信正常。

对寄存器的操作一般有两种:位操作和字操作 2~3 。

(1)位操作:寄存器的位操作主要用于BIT SET,BIT CLR。

例如:BIT SET MODE2 0x00000001?

BIT CLR MODE2 0x00000001。

以上操作将MODE2的第一位置位或清除,而不影响到其它位。

(2)字操作:寄存器的字操作用DM()寻址指令。

例如:R0=0x00000001;

DM(SYSCON)=R0。

以上操作将SYSCON的第一位置位,其它位清除。

对存储器的操作采用DM()指令寻扯,在指令中加入立即数、寄存器Rx(内容为寻址值)、基址(Ix)和变址(Mx)可实现直接寻址、间接寻址和变址寻址。

例如:R0=0x23;

DM(0x00030000 =R0。

以上操作将0x23放入0x00030000的地址内。

2.2 系统运行测试

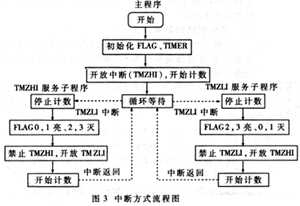

设计一个对FLAG位的四个指示灯的操作,让其交替地闪烁,来检验ADSP21062处理器是否能够正常运行。程序采用中断方式,利用定时器溢出时产生两个中断TMZHI和TMZLI。一个中断的服务程序设置FLAG0,1的指示灯亮,FLAG2 3的指示灯灭;另一个中断服务程序设置情况相反。两个服务程序交替执行,交替的间隔由定时器的初值确定。程序流程图见图3。

由于处理器在系统复位时MODE2寄存器被清除,使FLAG管脚作为输入,处理器不能改变其状态。所以主程序需对其初始化,使FLAG管脚作为输出,然后才能在ASTAT寄存器中改变FLAG的状态。同样,对定时器也要进行设置。

(1)定时器的设置:

BIT SET MODE1 0x1000;(开放全局中断)

BIT SET MODE2 0x20; (开放定时器)

BIT SET IMASK 0x10; (开放TMZHI中断)

(2)FLAG位的设置:

BIT SET MODE2 0x78000; (设置为输出)

BIT CLR ASTAT 0x180000; (FLAG0 1亮)

BIT SET ASTAT 0x600000; (FLAG2 3灭)

此程序可通过JTAG仿真测试,用通用编程器将此程序写入EPROM,然后让系统单独工作,来验证系统能否正常引导和工作。上电后四个指示灯交替闪烁,经验证系统顺利地完成了引导,并且工作正常。

2.3 Link口测试

用传输线把处理器的两个Link口连在一起,然后让一个Link口发数据,另一个收数据,通过Emulator JTAG 采用单步执行的方式对其测试,观察发送和接收的过程。

(1)Link口传输速率的设置:

R0=0x00006000;

DM LCOM =R0; 2倍速率)

(2)LBUF的设置:

R0=0x0003fe8f;

DM LAR =R0 ;?LBUF1给Link口1,LBUF2

给Link口2)

(3)开放Link口:

R0=0x00000190;

DM LCTL =R0 ; Link口1发,Link口2收)

(4)传输操作:

R0=0x12345678;

DM LBUF1 =R0 ; Link口1发0x12345678)

R1=DM LBUF2 ; 取Link口2收到的数据)

经测试,Link口的工作正常。通过Emulator的Link口控制窗口可以看到:当Link口设置完成,执行DM(LBUF1)=R0指令时,可以看到Link口2缓冲区的状态(通过LxSTAT寄存器)为有一个数据;当执行R1=DM(LBUF2)指令时,Link口2缓冲区的状态为空,寄存器R1口的值为Link口1的缓冲区(LBUF1)的内容。证明通过Link口1顺利地把数传给Link口2,通过Link口可以完成处理器之间的通信。

2.4 DSP算法的执行时间

将一个用汇编编写的DSP算法通过EZ-ICE仿真器放到系统中执行,由Emulator提供的时钟(指令)计数功能,可以知道算法在处理器中实际执行的时间。在Emulator的计数窗口中有一个时钟计数(Cycle Count),它记录程序从开始执行到停止所用时钟周期的个数,用时钟的个数(Cycle Count)乘以时钟周期就可以得到执行的总的时间。

针对ADSP2106x处理系统的开发研究,本文提出的简单易行的测试方法既可判别DSP能否正常工作,又可测试多处理器互联时通过Link口传输信息的有效性。所提的测试方法在我们研制的基于ADSP21062的雷达信号处理系统的调试中获得了验证。

1 雷达信号处理系统设计简介

我们应用ADSP21062处理器设计了一个雷达信号处理系统。此系统可以独立地进行工作,也可通过Link口与其它DSP进行通信。ADSP21062利用JTAG接口与EZ-ICE仿真器连接,实现对系统的仿真和测试。系统的电路结构见图1。

EZ-ICE仿真器应用IEEE1149.1 JTAG测试标准,监视和控制目标板处理器的工作。EZ-ICE仿真器的测试头通过一个14针的连接头与目标板处理器的CLKIN (可选)、TMS、TCK、TRST、TDI、TDO、和GND信号相连。在电路板上设计了一个14针的接口,其信号的接口如图2所示。

2 电路的测试

电路测试主要应用EZ-ICE仿真器。该仿真器插在PC机的ISA槽中,通过JTAG口与ADSP21062处理系统相连,可在PC机的显示器上利用Emulator控制界面对DSP系统运行情况进行实时监控。ADSP2106x提供了模拟(Simulator)和仿真(Emulator)两套软件,它们的界面完全相同,只是一个不需要硬件,一个需要硬件。测试程序可先由Assembler汇编器汇编,再经Simulator模拟通过。最后在Emulator界面控制下可以装入由汇编生成的可执行文件(.EXE文件)和汇编的结构文件(.ACH文件),实现对硬件的测试和仿真。

2.1 硬件测试的基本操作

对硬件测试时,先对存储器的内部控制、状态寄存器和存储器做简单的操作,确定EZ-ICE仿真器与处理器的通信正常。

对寄存器的操作一般有两种:位操作和字操作 2~3 。

(1)位操作:寄存器的位操作主要用于BIT SET,BIT CLR。

例如:BIT SET MODE2 0x00000001?

BIT CLR MODE2 0x00000001。

以上操作将MODE2的第一位置位或清除,而不影响到其它位。

(2)字操作:寄存器的字操作用DM()寻址指令。

例如:R0=0x00000001;

DM(SYSCON)=R0。

以上操作将SYSCON的第一位置位,其它位清除。

对存储器的操作采用DM()指令寻扯,在指令中加入立即数、寄存器Rx(内容为寻址值)、基址(Ix)和变址(Mx)可实现直接寻址、间接寻址和变址寻址。

例如:R0=0x23;

DM(0x00030000 =R0。

以上操作将0x23放入0x00030000的地址内。

2.2 系统运行测试

设计一个对FLAG位的四个指示灯的操作,让其交替地闪烁,来检验ADSP21062处理器是否能够正常运行。程序采用中断方式,利用定时器溢出时产生两个中断TMZHI和TMZLI。一个中断的服务程序设置FLAG0,1的指示灯亮,FLAG2 3的指示灯灭;另一个中断服务程序设置情况相反。两个服务程序交替执行,交替的间隔由定时器的初值确定。程序流程图见图3。

由于处理器在系统复位时MODE2寄存器被清除,使FLAG管脚作为输入,处理器不能改变其状态。所以主程序需对其初始化,使FLAG管脚作为输出,然后才能在ASTAT寄存器中改变FLAG的状态。同样,对定时器也要进行设置。

(1)定时器的设置:

BIT SET MODE1 0x1000;(开放全局中断)

BIT SET MODE2 0x20; (开放定时器)

BIT SET IMASK 0x10; (开放TMZHI中断)

(2)FLAG位的设置:

BIT SET MODE2 0x78000; (设置为输出)

BIT CLR ASTAT 0x180000; (FLAG0 1亮)

BIT SET ASTAT 0x600000; (FLAG2 3灭)

此程序可通过JTAG仿真测试,用通用编程器将此程序写入EPROM,然后让系统单独工作,来验证系统能否正常引导和工作。上电后四个指示灯交替闪烁,经验证系统顺利地完成了引导,并且工作正常。

2.3 Link口测试

用传输线把处理器的两个Link口连在一起,然后让一个Link口发数据,另一个收数据,通过Emulator JTAG 采用单步执行的方式对其测试,观察发送和接收的过程。

(1)Link口传输速率的设置:

R0=0x00006000;

DM LCOM =R0; 2倍速率)

(2)LBUF的设置:

R0=0x0003fe8f;

DM LAR =R0 ;?LBUF1给Link口1,LBUF2

给Link口2)

(3)开放Link口:

R0=0x00000190;

DM LCTL =R0 ; Link口1发,Link口2收)

(4)传输操作:

R0=0x12345678;

DM LBUF1 =R0 ; Link口1发0x12345678)

R1=DM LBUF2 ; 取Link口2收到的数据)

经测试,Link口的工作正常。通过Emulator的Link口控制窗口可以看到:当Link口设置完成,执行DM(LBUF1)=R0指令时,可以看到Link口2缓冲区的状态(通过LxSTAT寄存器)为有一个数据;当执行R1=DM(LBUF2)指令时,Link口2缓冲区的状态为空,寄存器R1口的值为Link口1的缓冲区(LBUF1)的内容。证明通过Link口1顺利地把数传给Link口2,通过Link口可以完成处理器之间的通信。

2.4 DSP算法的执行时间

将一个用汇编编写的DSP算法通过EZ-ICE仿真器放到系统中执行,由Emulator提供的时钟(指令)计数功能,可以知道算法在处理器中实际执行的时间。在Emulator的计数窗口中有一个时钟计数(Cycle Count),它记录程序从开始执行到停止所用时钟周期的个数,用时钟的个数(Cycle Count)乘以时钟周期就可以得到执行的总的时间。

针对ADSP2106x处理系统的开发研究,本文提出的简单易行的测试方法既可判别DSP能否正常工作,又可测试多处理器互联时通过Link口传输信息的有效性。所提的测试方法在我们研制的基于ADSP21062的雷达信号处理系统的调试中获得了验证。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)